REV. 0

AD7708/AD7718

–27–

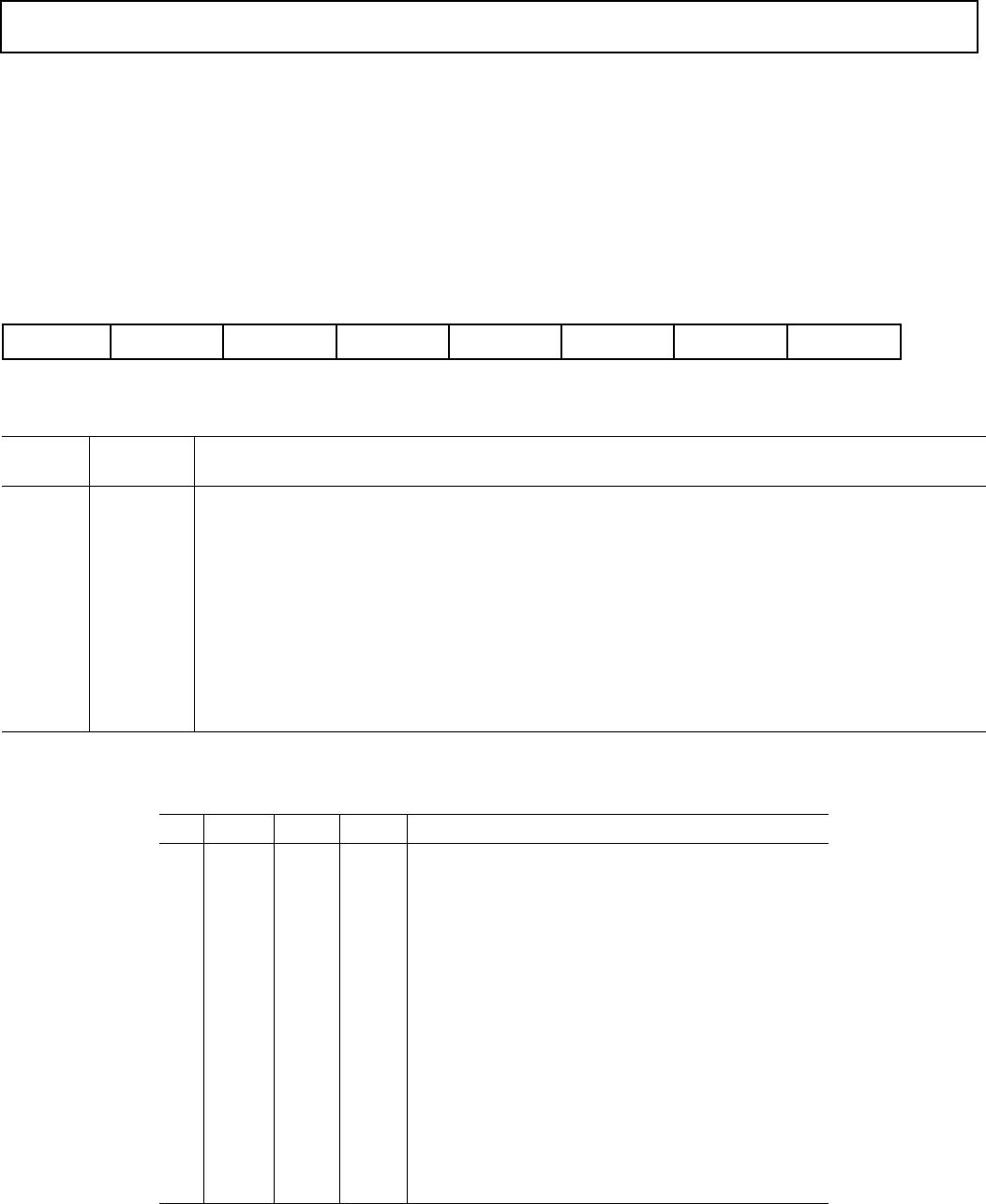

Mode Register (A3, A2, A1, A0 = 0, 0, 0, 1; Power-On-Reset = 00Hex)

The Mode Register is an 8-bit register from which data can be read or to which data can be written. This register configures the

operating modes of the AD7708/AD7718. Table XV outlines the bit designations for the Mode Register. MR7 through MR0 indi-

cate the bit location, MR denoting the bits are in the Mode Register. MR7 denotes the first bit of the data stream. The number in

brackets indicates the power-on/reset default status of that bit.

7RM6RM5RM4RM3RM2RM1RM0RM

POHC )0(

)0(FUBGEN)0(LESFER)0(NOCHC)0(DPCSO)0(2DM)0(1DM)0(0DM

Table XV. Mode Register Bit Designations

Bit Bit

Location Mnemonic Description

MR7 CHOP If this bit is cleared, chopping is enabled. When this bit is set chopping is disabled. The default is for

chop enabled.

MR6 NEGBUF This bit controls the operation of the input buffer on the AINCOM input when a channel is config-

ured for pseudo-differential mode of operation. If cleared, the analog negative input (AINCOM) is

unbuffered allowing it to be tied to AGND in single-ended input configuration. If this bit is set the

analog negative input (AINCOM) is buffered, placing a restriction on its common-mode input range.

MR5 REFSEL If this bit is cleared, the reference selected is REFIN1(+) and REFIN1(–) for the active channel. If

this bit is set, the reference selected is REFIN2(+) and REFIN2(–) for the active channel. The con-

tents of the CHCON bit overrides the REFSEL bit. If the ADC is configured in five fully-differential

or 10 pseudo-differential input channel mode, the REFSEL bit setting is irrelevant as only one

reference input is available. V

REF

Select implemented using the REFSEL bit enables the user to

perform both absolute and ratiometric measurements.

MR4 CHCON When cleared the device is configured as an 8-input channel converter, configured as eight pseudo-

differential input channels with respect to AINCOM or four differential input arrangements

with two reference input selection options. When set the device is configured as a 10 pseudo-

differential input or a five differential input channel arrangement with a single reference

input option.

MR3 OSCPD Oscillator Power-Down Bit.

If this bit is set, placing the AD7708/AD7718 in standby mode will stop the crystal oscillator reducing

the power drawn by these parts to a minimum. The oscillator will require 300 ms to begin oscillating

when the ADC is taken out of standby mode. If this bit is cleared, the oscillator is not shut off when

the ADC is put into standby mode and will not require the 300 ms start-up time when the ADC is

taken out of standby.

MR2–MR0 MD2–MD0 ADC Mode Bits.

These bits select the operational mode of the ADC as follows:

MD2 MD1 MD0

0 0 0 Power-Down Mode (Power-On Default)

0 0 1 Idle Mode

In Idle Mode the ADC filter and modulator are held in a reset state although the modulator clocks

are still provided.

0 1 0 Single Conversion Mode

In Single Conversion Mode, a single conversion is performed on the enabled channels. On comple-

tion of the conversion the ADC data registers are updated, the relevant flags in the STATUS register

are written, and idle mode is reentered with the MD2–MD0 being written accordingly to 001.

0 1 1 Continuous Conversion

In continuous conversion mode, the ADC data registers are regularly updated at the selected update

rate (see Filter register).

1 0 0 Internal Zero-Scale Calibration

Internal short automatically connected to the enabled channel(s)

1 0 1 Internal Full-Scale Calibration

External V

REF

is connected automatically to the ADC input for this calibration.

1 1 0 System Zero-Scale Calibration

User should connect system zero-scale input to the channel input pins as selected by CH3–CH0 bits

in the control registers.

1 1 1 System Full-Scale Calibration

User should connect system full-scale input to the channel input pins as selected by CH3–CH0 bits

in the control registers.