REV. 0

–40–

AD7708/AD7718

Calibration

The AD7708/AD7718 provides four calibration modes that can

be programmed via the mode bits in the mode register. One of

the major benefits of the AD7708/AD7718 is that it is factory-

calibrated with chopping enabled as part of the final test process

with the generated coefficients stored within the ADC. At power-

on, the factory gain calibration coefficients are automatically

loaded to the gain calibration registers on the AD7708/AD7718.

This gives excellent offset and drift performance and it is

envisaged that in the majority of applications the user will not

need to perform any field calibrations.

Also, because factory

gain calibration coefficients (generated at 25°C ambient) are

automatically present at power-on, an internal full-scale calibration

will only be required if the part is being operated at temperatures

significantly different from 25°C.

When chopping is disabled (CHOP =1) the AD7708/AD7718

requires an offset calibration or new calibration coefficients on

range changing or when significant temperature changes occur

as the signal chain is no longer chopped and offset and drift

errors are no longer removed as part of the conversion process.

The factory-calibration values for any one channel will be over-

written if any one of the four calibration options is initiated.

The AD7708/AD7718 offers “internal” or “system” calibration

facilities. For full calibration to occur, the calibration logic must

record the modulator output for two different input conditions.

These are “zero-scale” and “full-scale” points. These points

are derived by performing a conversion on the different input

voltages provided to the input of the modulator during calibration.

The result of the “zero-scale” calibration conversion is stored in

the Offset Calibration Registers for the appropriate channel.

The result of the “full-scale” calibration conversion is stored

in the Gain Calibration Registers. With these readings, the

calibration logic can calculate the offset and the gain slope for

the input-to-output transfer function of the converter. During an

“internal” zero-scale or full-scale calibration, the respective

“zero” input and “full-scale” input are automatically connected

to the ADC input pins internally to the device. A “system” cali-

bration, however, expects the system zero-scale and system

full-scale voltages to be applied to the external ADC pins

before the calibration mode is initiated. In this way external

ADC errors are taken into account and minimized as a result

of system calibration. It should also be noted that to optimize

calibration accuracy, all AD7708/AD7718 ADC calibrations

are carried out automatically at the slowest update rate with

chop enabled. When chop mode is disabled calibrations are

carried out at the update rate defined by the SF word in the

filter register.

Internally in the AD7708/AD7718, the coefficients are normalized

before being used to scale the words coming out of the digital

filter. The offset calibration coefficient is subtracted from the

result prior to the multiplication by the gain coefficient. With

chopping disabled AD7708/AD7718 ADC specifications will

only apply after a zero-scale calibration at the operating point of

interest. From an operational point of view, a calibration should

be treated like another ADC conversion. A zero-scale calibration

(if required) should always be carried out before a full-scale

calibration. System software should monitor the RDY bit in the

STATUS register to determine end of calibration via a polling

sequence or interrupt driven routine.

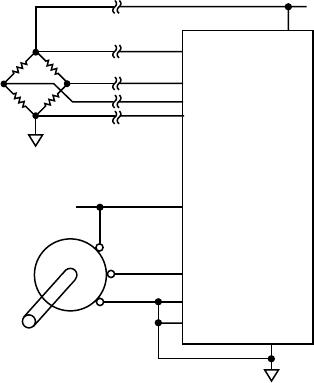

Grounding and Layout

Since the analog inputs and reference inputs are differential,

most of the voltages in the analog modulator are common-mode

voltages. The excellent common-mode rejection of the part will

remove common-mode noise on these inputs. The analog and

digital supplies to the AD7708/AD7718 are independent and

separately pinned out to minimize coupling between the analog

and digital sections of the device. The AD7708/AD7718 can be

operated with 5 V analog and 3 V digital supplies or vice versa.

The digital filter will provide rejection of broadband noise on

the power supplies, except at integer multiples of the modulator

sampling frequency. The digital filter also removes noise from

the analog and reference inputs provided these noise sources do

not saturate the analog modulator. As a result, the AD7708/

AD7718 is more immune to noise interference than a conventional

high-resolution converter. However, because the resolution of the

AD7708/AD7718 is so high and the noise

levels from the

converter so low, care must be taken with regard to grounding

and layout.

The printed circuit board that houses the ADC should be designed

so the analog and digital sections are separated and confined to

certain areas of the board. This facilitates the use of ground planes

that can be easily separated. A minimum etch technique is

generally best for ground planes as it gives the best shielding.

Although the AD7708/AD7718 has separate pins for analog and

digital ground, the AGND and DGND pins are tied together

internally via the substrate. Therefore, the user must not tie

these two pins to separate ground planes unless the ground

planes are connected together near the AD7708/AD7718.

In systems where the AGND and DGND are connected some-

where else in the system, i.e., the systems power supply, they

should not be connected again at the AD7708/AD7718 or a

ground loop will result. In these situations it is recommended that

ground pins of the AD7708/AD7718 be tied to the AGND plane.

In any layout it is implicit that the user keep in mind the flow of

currents in the system, ensuring that the paths for all currents

are as close as possible to the paths the currents took to reach

their destinations. Avoid forcing digital currents to flow through

the AGND.

Avoid running digital lines under the device as these will couple

noise onto the die. The analog ground plane should be allowed

to run under the AD7708/AD7718 to prevent noise coupling.

The power supply lines to the AD7708/AD7718 should use as

wide a trace as possible to provide low impedance paths and

reduce the effects of glitches on the power supply line. Fast

switching signals like clocks should be shielded with digital

ground to avoid radiating noise to other sections of the board

and clock signals should never be run near the analog inputs.

Avoid crossover of digital and analog signals. Traces on opposite

sides of the board should run at right angles to each other. This will

reduce the effects of feedthrough through the board. A microstrip

technique is by far the best, but is not always possible with a

double-sided board. In this technique, the component side of

the board is dedicated to ground planes while signals are placed

on the solder side.