REV. 0

–7–

AD7708/AD7718

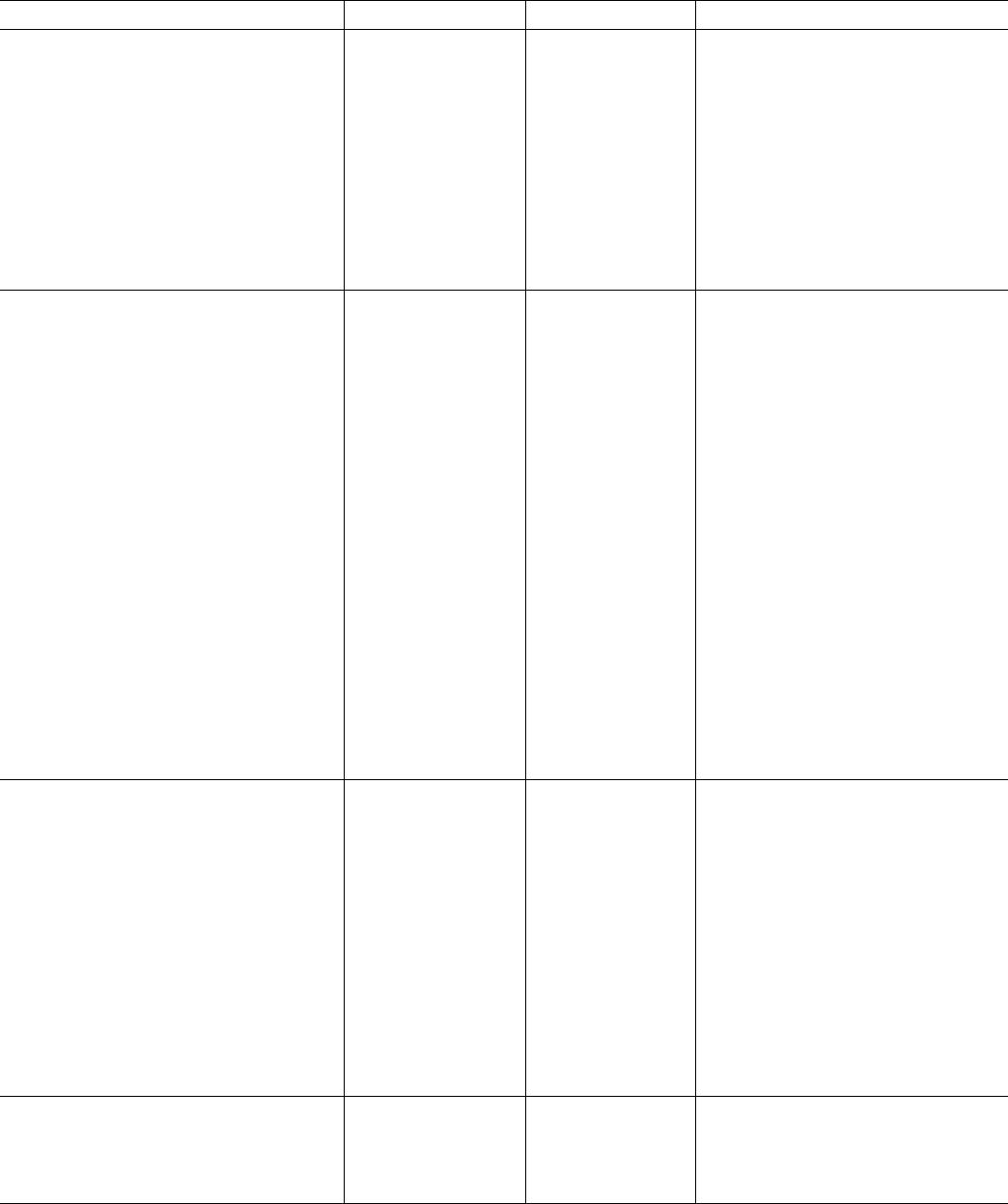

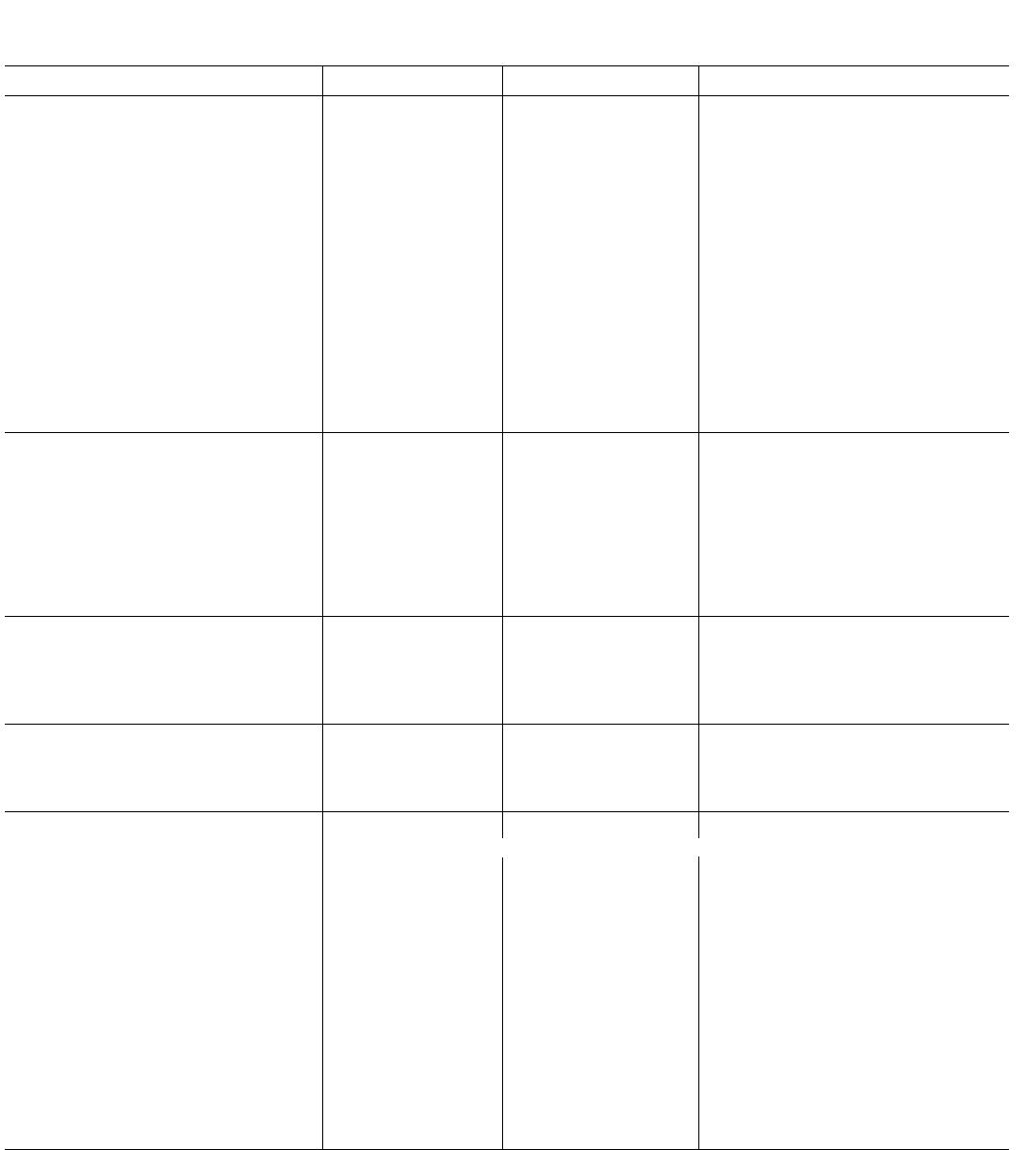

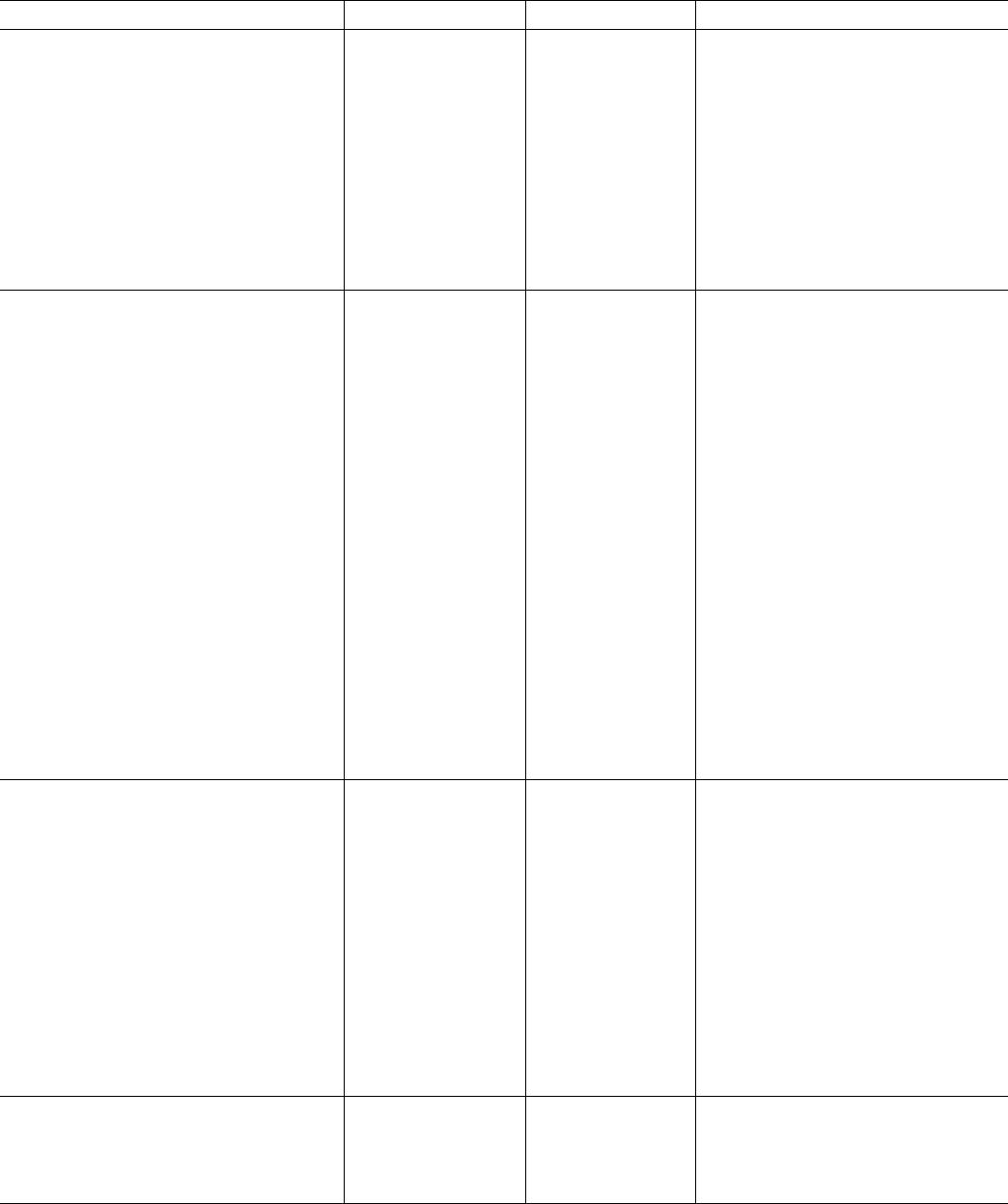

Parameter B Grade Unit Test Conditions

AD7708 (CHOP ENABLED)

Output Update Rate 5.4 Hz min CHOP = 1

105 Hz max 0.732 ms Increments

No Missing Codes

2

16 Bits min 20 Hz Update Rate

Resolution 13 Bits p-p ±20 mV Range, 20 Hz Update Rate

16 Bits p-p ±2.56 V Range, 20 Hz Update Rate

Output Noise and Update Rates See Tables in

ADC Description

Integral Nonlinearity ±15 ppm of FSR max 2 ppm Typical

Offset Error

3

±3 µV typ Calibration is Accurate to ±0.5 LSB

Offset Error Drift vs. Temp

4

10 nV/°C typ

Full-Scale Error

3

±0.75 LSB typ Includes Positive and Negative ERRORS

Gain Drift vs. Temp

4

±0.5 ppm/°C typ

ANALOG INPUTS

Differential Input Full-Scale Voltage ±1.024 × REFIN/GAIN V nom REFIN Refers to Both REFIN1 and

REFIN2. REFIN = REFIN(+) REFIN(–)

GAIN = 1 to 128

Range Matching ±2 µV typ Analog Input = 18 mV

Absolute AIN Voltage Limits AGND + 100 mV V min AIN1–AIN10 and AINCOM with

AV

DD

– 100 mV V max NEGBUF = 1

Absolute AINCOM Voltage Limits AGND – 30 mV V min NEGBUF = 0

AV

DD

+ 30 mV V max

Analog Input Current AIN1–AIN10 and AINCOM with

NEGBUF = 1

DC Input Current

2

±1 nA max

DC Input Current Drift ±5 pA/°C typ

AINCOM Input Current NEGBUF = 0

DC Input Current

2

±125 nA/V typ

DC Bias Current Drift ±2 pA/V/°C typ

Normal-Mode Rejection

2

@ 50 Hz 100 dB min 50 Hz ± 1 Hz, SF Word = 82

@ 60 Hz 94 dB min 60 Hz ± 1 Hz, SF Word = 68

Common-Mode Rejection

@ DC 90 dB min 100 dB typ, Analog Input = 1 V,

Input Range = ±2.56 V

110 dB typ on ±20 mV Range

@ 50 Hz

2

100 dB min 50 Hz ± 1 Hz, 20 Hz Update Rate

@ 60 Hz

2

100 dB min 60 Hz ± 1 Hz, 20 Hz Update Rate

REFERENCE INPUTS (REFIN1 AND REFIN2)

REFIN(+) to REFIN(–) Voltage 2.5 V nom REFIN Refers to Both REFIN1 and

REFIN2

REFIN(+) to REFIN(–) Range

2

1V min

AV

DD

V max

REFIN Common-Mode Range AGND – 30 mV V min

AV

DD

+ 30 mV V max

Reference DC Input Current

2

±0.5 µA/V typ

Reference DC Input Current Drift ±0.01 nA/V/°C typ

Normal-Mode Rejection

2

@ 50 Hz 100 dB min 50 Hz ± 1 Hz, SF Word = 82

@ 60 Hz 100 dB min 60 Hz ± 1 Hz, SF Word = 68

Common-Mode Rejection Input Range = ±2.56 V

@ DC 110 dB typ Analog Input = 1 V

@ 50 Hz 110 dB typ 50 Hz ± 1 Hz, 20 Hz Update Rate

@ 60 Hz 110 dB typ 60 Hz ± 1 Hz, 20 Hz Update Rate

LOGIC INPUTS

5

All Inputs Except SCLK and XTAL1

2

V

INL

, Input Low Voltage 0.8 V max DV

DD

= 5 V

0.4 V max DV

DD

= 3 V

V

INH

, Input High Voltage 2.0 V min DV

DD

= 3 V or 5 V