AD7705/AD7706

Rev. C | Page 13 of 44

OUTPUT NOISE (3 V OPERATION)

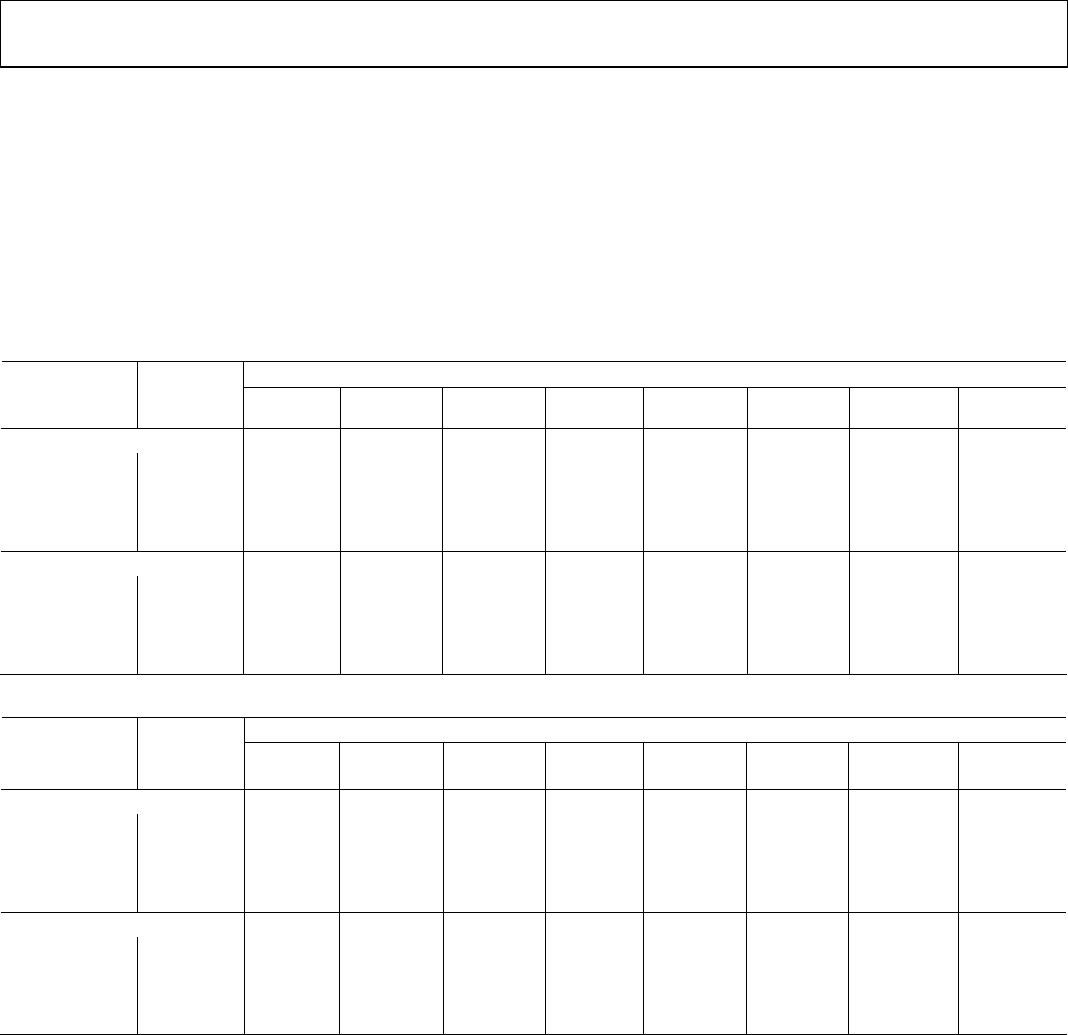

Table 7 shows the AD7705/AD7706 output rms noise for the

selectable notch and −3 dB frequencies for the parts, as selected

by FS0 and FS1 of the clock register. The numbers given are for

the bipolar input ranges with a V

REF

of 1.225 V and a V

DD

= 3 V.

These numbers are typical and are generated at an analog input

voltage of 0 V with the parts used in either buffered or unbuffered

mode.

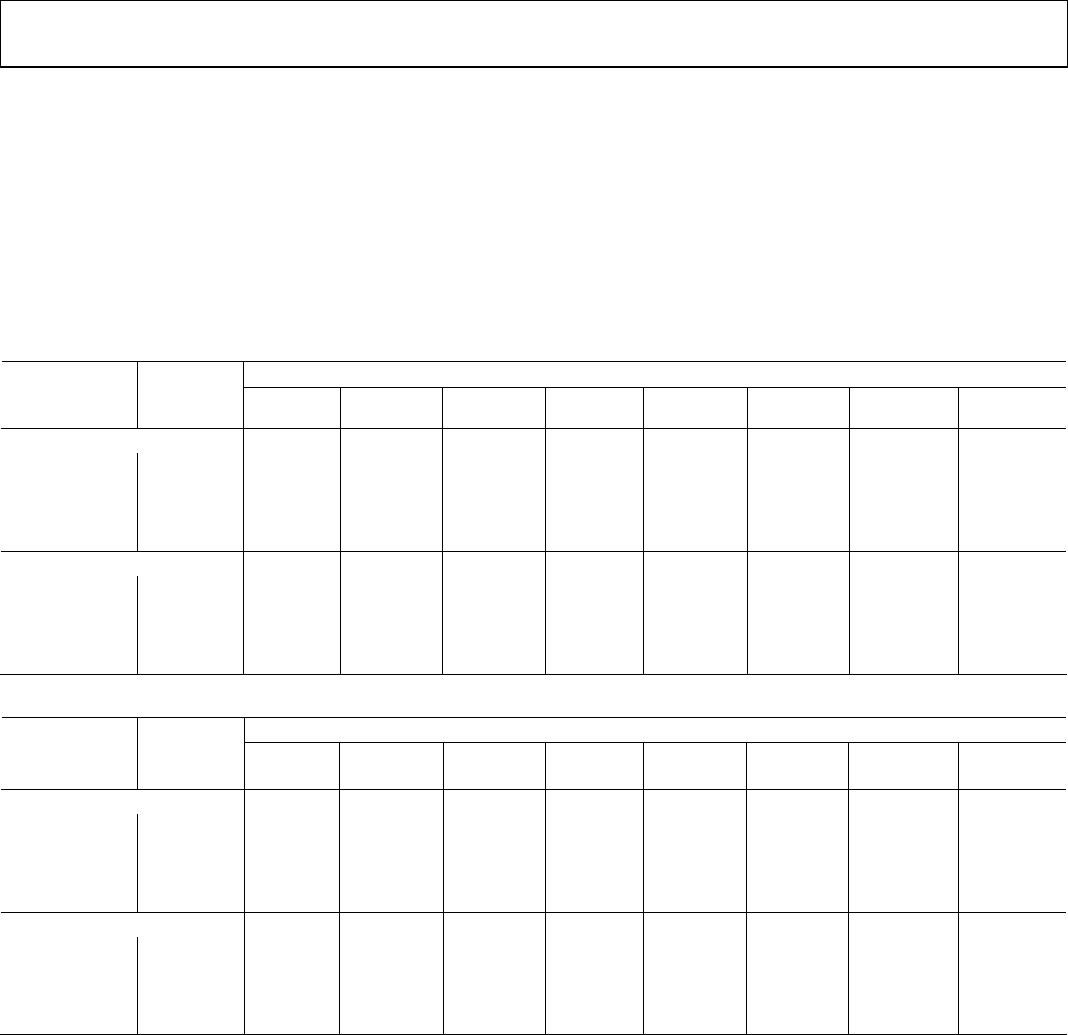

Table 8 shows the output peak-to-peak noise for the

selectable notch and −3 dB frequencies for the parts.

Note that these numbers represent the resolution for which

there is no code flicker. They are not calculated based on rms

noise, but on peak-to-peak noise. The numbers given are for

bipolar input ranges with a V

REF

of 1.225 V for either buffered or

unbuffered mode. These numbers are typical and are rounded

to the nearest LSB. The numbers apply for the CLKDIV bit of

the clock register set to 0.

Table 7. Output RMS Noise vs. Gain and Output Update Rate @ 3 V

Typical Output RMS Noise in μV Filter First

Notch and

O/P Data Rate

−3 dB

Frequency

Gain of 1 Gain of 2 Gain of 4 Gain of 8 Gain of 16 Gain of 32 Gain of 64 Gain of 128

MCLK IN = 2.4576 MHz

50 Hz 13.1 Hz 3.8 2.4 1.5 1.3 1.1 1.0 0.9 0.9

60 Hz 15.72 Hz 5.1 2.9 1.7 1.5 1.2 1.0 0.9 0.9

250 Hz 65.5 Hz 50 25 14 9.9 5.1 2.6 2.3 2.0

500 Hz 131 Hz 270 135 65 41 22 9.7 5.1 3.3

MCLK IN = 1 MHz

20 Hz 5.24 Hz 3.8 2.4 1.5 1.3 1.1 1.0 0.9 0.9

25 Hz 6.55 Hz 5.1 2.9 1.7 1.5 1.2 1.0 0.9 0.9

100 Hz 26.2 Hz 50 25 14 9.9 5.1 2.6 2.3 2.0

200 Hz 52.4 Hz 270 135 65 41 22 9.7 5.1 3.3

Table 8. Peak-to-Peak Resolution vs. Gain and Output Update Rate @ 3 V

Typical Peak-to-Peak Resolution in Bits

Filter First

Notch and

O/P Data Rate

−3 dB

Frequency Gain of 1 Gain of 2 Gain of 4 Gain of 8 Gain of 16 Gain of 32 Gain of 64 Gain of 128

MCLK IN = 2.4576 MHz

50 Hz 13.1 Hz 16 16 15 15 14 13 13 12

60 Hz 15.72 Hz 16 16 15 14 14 13 13 12

250 Hz 65.5 Hz 13 13 13 13 12 12 11 11

500 Hz 131 Hz 10 10 10 10 10 10 10 10

MCLK IN = 1 MHz

20 Hz 5.24 Hz 16 16 15 15 14 13 13 12

25 Hz 6.55 Hz 16 16 15 14 14 13 13 12

100 Hz 26.2 Hz 13 13 13 13 12 12 11 11

200 Hz 52.4 Hz 10 10 10 10 10 10 10 10