AD7705/AD7706

Rev. C | Page 5 of 44

SPECIFICATIONS

V

DD

= 3 V or 5 V, REF IN(+) = 1.225 V with V

DD

= 3 V, and 2.5 V with V

DD

= 5 V; REF IN(−) = GND; MCLK IN = 2.4576 MHz, unless

otherwise noted. All specifications T

MIN

to T

MAX

, unless otherwise noted.

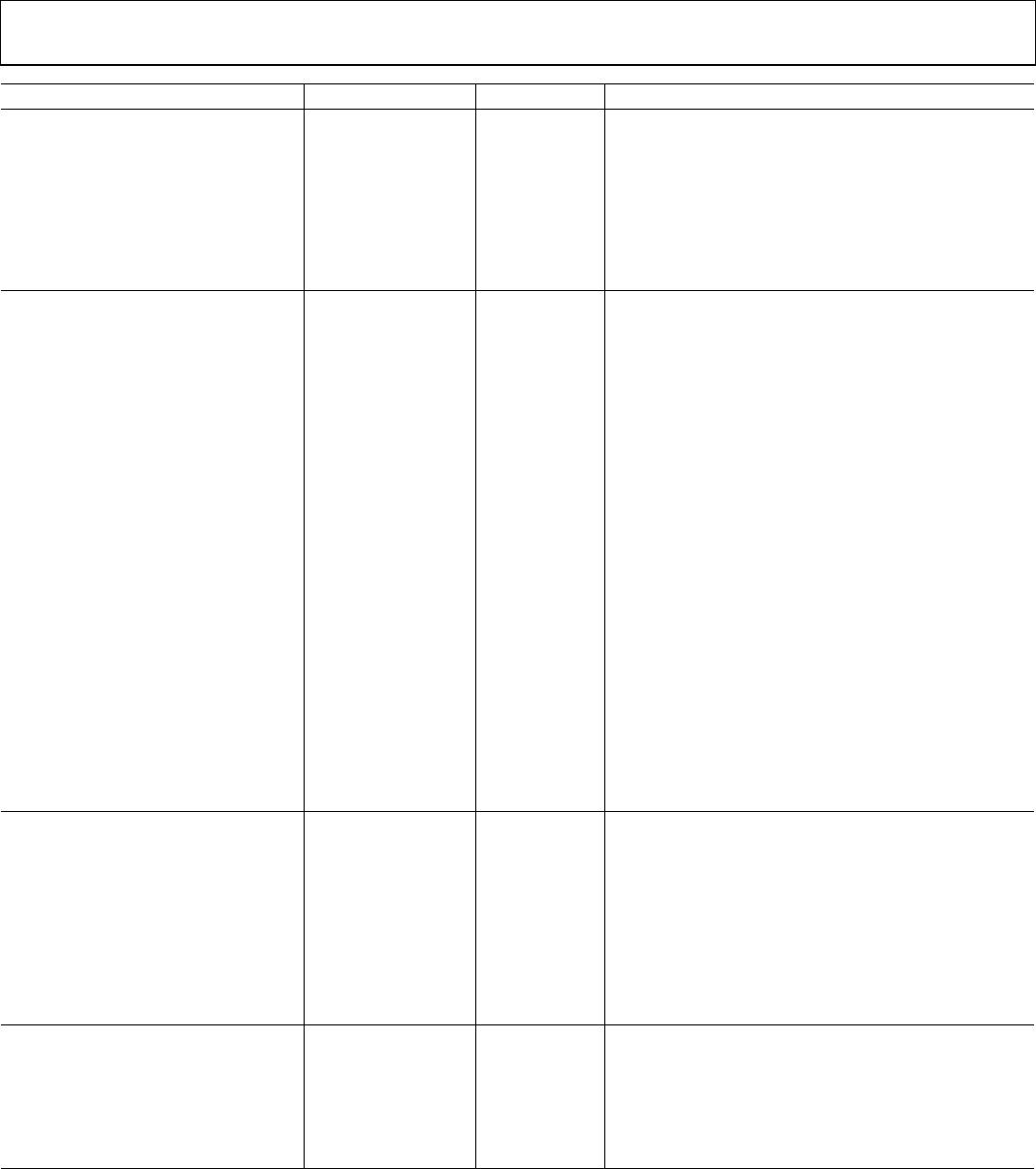

Table 1.

Parameter B Version

1

Unit Conditions/Comments

STATIC PERFORMANCE

No Missing Codes 16 Bits min Guaranteed by design, filter notch < 60 Hz

Output Noise

See

Table 5 and

Table 7

Depends on filter cutoffs and selected gain

Integral Nonlinearity

2

±0.003 % of FSR max Filter notch < 60 Hz, typically ±0.0003%

Unipolar Offset Error

3

Unipolar Offset Drift

4

0.5 μV/°C typ

Bipolar Zero Error

3

Bipolar Zero Drift

4

0.5 μV/°C typ For gains 1, 2, and 4

0.1 μV/°C typ For gains 8, 16, 32, 64, and 128

Positive Full-Scale Error

3, 5

Full-Scale Drift

4, 6

0.5 μV/°C typ

Gain Error

3, 7

Gain Drift

4, 8

0.5

ppm of FSR/°C

typ

Bipolar Negative Full-Scale Error

2

±0.003 % of FSR typ Typically ±0.001%

Bipolar Negative Full-Scale Drift

4

1 μV/°C typ For gains of 1 to 4

0.6 μV/°C typ For gains of 8 to 128

ANALOG INPUTS/REFERENCE INPUTS

Specifications for AIN and REF IN, unless otherwise

noted

Common-Mode Rejection (CMR)

2

V

DD

= 5 V

Gain = 1 96 dB typ

Gain = 2 105 dB typ

Gain = 4 110 dB typ

Gain = 8 to 128 130 dB typ

V

DD

= 3 V

Gain = 1 105 dB typ

Gain = 2 110 dB typ

Gain = 4 120 dB typ

Gain = 8 to 128 130 dB typ

Normal-Mode 50 Hz Rejection

2

98 dB typ For filter notches of 25 Hz, 50 Hz, ±0.02 × f

NOTCH

Normal-Mode 60 Hz Rejection

2

98 dB typ For filter notches of 20 Hz, 60 Hz, ±0.02 × f

NOTCH

Common-Mode 50 Hz Rejection

2

150 dB typ For filter notches of 25 Hz, 50 Hz, ±0.02 × f

NOTCH

Common-Mode 60 Hz Rejection

2

150 dB typ For filter notches of 20 Hz, 60 Hz, ±0.02 × f

NOTCH

Absolute/Common-Mode REF IN

Voltage

2

GND to V

DD

V min to V max

Absolute/Common-Mode AIN

Voltage

2, 9, 10

GND − 100 mV V min BUF bit of setup register = 0

V

DD

+ 30 mV V max

Absolute/Common-Mode AIN

Voltage

2, 9

GND + 50 mV V min BUF bit of setup register = 1

V

DD

− 1.5 V V max

AIN DC Input Current

2

1 nA max

AIN Sampling Capacitance

2

10 pF max

AIN Differential Voltage Range

11

0 to +V

REF

/gain

12

nom

Unipolar input range (B

/U bit of setup register = 1)

±V

REF

/gain nom

Bipolar input range (B

/U bit of setup register = 0)