AD7705/AD7706

Rev. C | Page 20 of 44

DATA REGISTER (RS2, RS1, RS0 = 0, 1, 1)

The data register is a 16-bit, read-only register that contains the

most up-to-date conversion result from the AD7705/AD7706. If

the communication register sets up the part for a write

operation to this register, a write operation must take place to

return the part to its default state. However, the 16 bits of data

written to the part will be ignored by the AD7705/AD7706.

TEST REGISTER (RS2, RS1, RS0 = 1, 0, 0);

POWER-ON/RESET STATUS: 00 HEXADECIMAL

The part contains a test register that is used when testing the

device. The user is advised not to change the status of any of the

bits in this register from the default (power-on or reset) status

of all 0s, because the part will be placed in one of its test modes

and will not operate correctly.

ZERO-SCALE CALIBRATION REGISTER

(RS2, RS1, RS0 = 1, 1, 0);

POWER-ON/RESET STATUS: 1F4000 HEXADECIMAL

The AD7705/AD7706 contain independent sets of zero-scale

registers, one for each of the input channels. Each register is a

24-bit read/write register; therefore, 24 bits of data must be

written, or no data is transferred to the register. This register is

used in conjunction with its associated full-scale register to

form a register pair. These register pairs are associated with

input channel pairs, as outlined in

Table 12 and Table 13.

While the part is set up to allow access to these registers over

the digital interface, the parts themselves can no longer access

the register coefficients to scale the output data correctly. As a

result, the first output data read from the part after accessing

the calibration registers (for either a read or write operation)

might contain incorrect data. In addition, a write to the

calibration register should not be attempted while a calibration

is in progress. These eventualities can be avoided by taking the

FSYNC bit in the mode register high before the calibration

register operation, and taking it low after the operation is

complete.

FULL-SCALE CALIBRATION REGISTER

(RS2, RS1, RS0 = 1, 1, 1);

POWER-ON/RESET STATUS: 5761AB HEXADECIMAL

The AD7705/AD7706 contain independent sets of full-scale

registers, one for each of the input channels. Each register is a

24-bit read/write register; therefore, 24 bits of data must be

written, or no data is transferred to the register. This register is

used in conjunction with its associated zero-scale register to

form a register pair. These register pairs are associated with

input channel pairs, as outlined in

Table 12 and Table 13.

While the part is set up to allow access to these registers over

the digital interface, the part itself can no longer access the

register coefficients to scale the output data correctly. As a

result, the first output data read from the part after accessing

the calibration registers (for either a read or write operation)

might contain incorrect data. In addition, a write to the

calibration register should not be attempted while a calibration

is in progress. These eventualities can be avoided by taking

FSYNC bit in the mode register high before the calibration

register operation, and taking it low after the operation is

complete.

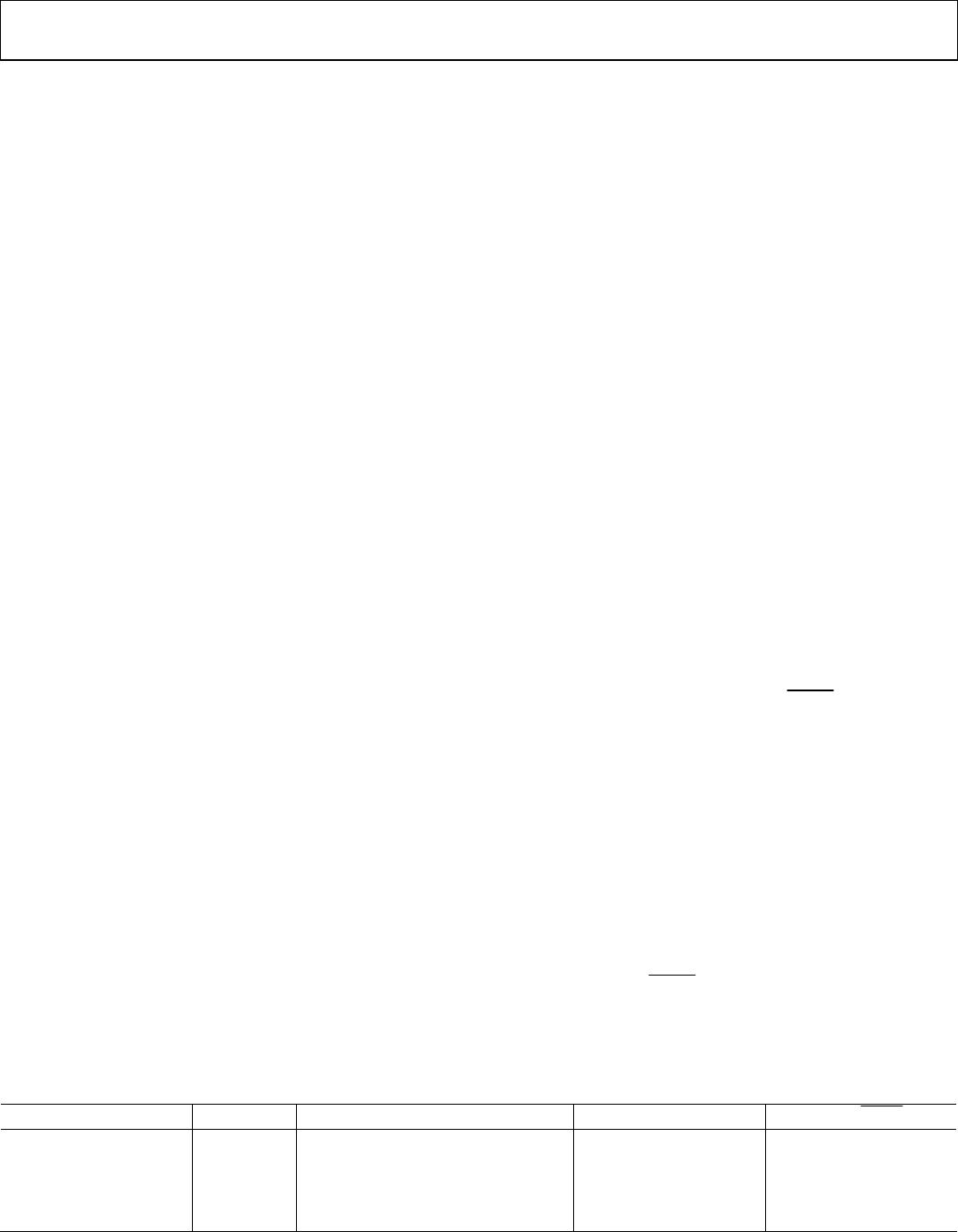

Calibration Sequences

The AD7705/AD7706 contain a number of calibration options,

as previously outlined.

Table 21 summarizes the calibration

types, the operations involved, and the duration of the

operations. There are two methods for determining the end of a

calibration. The first is to monitor when

DRDY

returns low at

the end of the sequence. This technique not only indicates when

the sequence is complete, but also when the part has a valid new

sample in its data register. This valid new sample is the result of

a normal conversion that follows the calibration sequence. The

second method for determining when calibration is complete is

to monitor the MD1 and MD0 bits of the setup register. When

these bits return to 0 following a calibration command, the

calibration sequence is complete. This technique can indicate

the completion of a calibration earlier than the first method

can, but it cannot indicate when there is a valid new result in

the data register. The time that it takes the mode bits, MD1 and

MD0, to return to 0 represents the duration of the calibration.

The sequence when

DRDY

goes low includes a normal

conversion and a pipeline delay, t

P

, to scale the results of this

first conversion correctly. Note that t

P

never exceeds 2000 ×

t

CLKIN

. The time for both methods is shown in Table 21.

Table 21. Calibration Sequences

Calibration Type MD1, MD0 Calibration Sequence Duration of Mode Bits Duration of

DRDY

Self-Calibration 0, 1

Internal ZS calibration @ selected gain

+ internal FS calibration @ selected

gain

6 × 1/output rate 9 × 1/output rate + t

P

ZS System Calibration 1, 0 ZS calibration on AIN @ selected gain 3 × 1/output rate 4 × 1/output rate + t

P

FS System Calibration 1, 1 FS calibration on AIN @ selected gain 3 × 1/output rate 4 × 1/output rate + t

P