AD7705/AD7706

Rev. C | Page 7 of 44

Parameter B Version

1

Unit Conditions/Comments

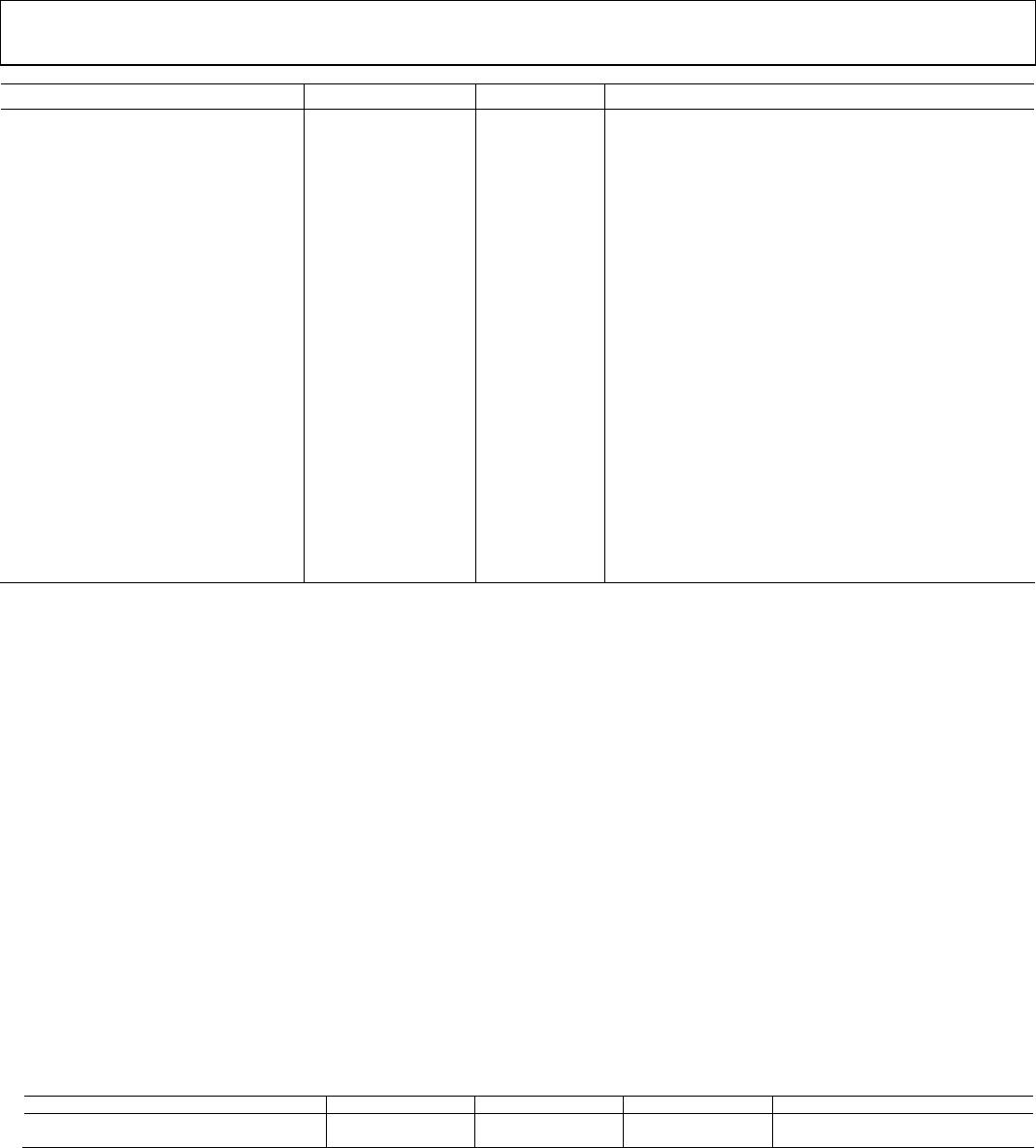

POWER REQUIREMENTS

V

DD

Voltage 2.7 to 3.3 V min to V max For specified performance

Power Supply Currents

17

Digital I/Ps = 0 V or V

DD

, external MCLK IN and CLKDIS = 1

0.32 mA max BUF bit = 0, f

CLKIN

= 1 MHz, gains of 1 to 128

0.6 mA max BUF bit = 1, f

CLKIN

= 1 MHz, gains of 1 to 128

0.4 mA max BUF bit = 0, f

CLKIN

= 2.4576 MHz, gains of 1 to 4

0.6 mA max BUF bit = 0, f

CLKIN

= 2.4576 MHz, gains of 8 to 128

0.7 mA max BUF bit = 1, f

CLKIN

= 2.4576 MHz, gains of 1 to 4

1.1 mA max BUF bit = 1, f

CLKIN

= 2.4576 MHz, gains of 8 to 128

V

DD

Voltage 4.75 to 5.25 V min to V max For specified performance

Power Supply Currents

17

Digital I/Ps = 0 V or V

DD

, external MCLK IN and CLKDIS = 1

0.45 mA max BUF bit = 0, f

CLKIN

= 1 MHz, gains of 1 to 128

0.7 mA max BUF bit = 1, f

CLKIN

= 1 MHz, gains of 1 to 128

0.6 mA max BUF bit = 0, f

CLKIN

= 2.4576 MHz, gains of 1 to 4

0.85 mA max BUF bit = 0, f

CLKIN

= 2.4576 MHz, gains of 8 to 128

0.9 mA max BUF bit = 1, f

CLKIN

= 2.4576 MHz, gains of 1 to 4

1.3 mA max BUF bit = 1, f

CLKIN

= 2.4576 MHz, gains of 8 to 128

Standby (Power-Down) Current

18

16 μA max External MCLK IN = 0 V or V

DD

, V

DD

= 5 V, see Figure 12

8 μA max External MCLK IN = 0 V or V

DD

, V

DD

= 3 V

Power Supply Rejection

19, 20

dB typ

1

Temperature range is −40°C to +85°C.

2

These numbers are established from characterization or design data at initial product release.

3

A calibration is effectively a conversion; therefore, these errors are of the order of the conversion noise shown in Table 5 and Table 7. This applies after calibration at

the temperature of interest.

4

Recalibration at any temperature removes these drift errors.

5

Positive full-scale error includes zero-scale errors (unipolar offset error or bipolar zero error) and applies to both unipolar and bipolar input ranges.

6

Full-scale drift includes zero-scale drift (unipolar offset drift or bipolar zero drift) and applies to both unipolar and bipolar input ranges.

7

Gain error does not include zero-scale errors. It is calculated as (full-scale error – unipolar offset error) for unipolar ranges and (full-scale error - bipolar zero error) for

bipolar ranges.

8

Gain drift does not include unipolar offset drift or bipolar zero drift. It is effectively the drift of the part if only zero-scale calibrations are performed.

9

This common-mode voltage range is allowed, provided that the input voltage on analog inputs is not more positive than V

DD

+ 30 mV or more negative than

GND − 100 mV. Parts are functional with voltages down to GND − 200 mV, but with increased leakage at high temperatures.

10

The AD7705/AD7706 can tolerate absolute analog input voltages down to GND − 200 mV, but the leakage current increases.

11

The analog input voltage range on AIN(+) is given with respect to the voltage on AIN(−) on the AD7705, and with respect to the voltage of the COMMON input on the

AD7706. The absolute voltage on the analog inputs should not be more positive than V

DD

+ 30 mV, or more negative than GND − 100 mV for specified performance.

Input voltages of GND − 200 mV can be accommodated, but with increased leakage at high temperatures.

12

V

REF

= REFIN(+) − REFIN(−).

13

These logic output levels apply to the MCLK OUT only when it is loaded with one CMOS load.

14

Sample tested at 25°C to ensure compliance.

15

After calibration, if the analog input exceeds positive full scale, the converter outputs all 1s. If the analog input is less than negative full scale, the device outputs all 0s.

16

These calibration and span limits apply, provided that the absolute voltage on the analog inputs does not exceed V

DD

+ 30 mV or go more negative than

GND − 100 mV. The offset calibration limit applies to both the unipolar zero point and the bipolar zero point.

17

When using a crystal or ceramic resonator across the MCLK pins as the clock source for the device, the V

DD

current and power dissipation varies depending on the

crystal or resonator type (see Clocking and Oscillator Circuit section).

18

If the external master clock continues to run in standby mode, the standby current increases to 150 μA typical at 5 V and 75 μA at 3 V. When using a crystal or ceramic

resonator across the MCLK pins as the clock source for the device, the internal oscillator continues to run in standby mode, and the power dissipation depends on the

crystal or resonator type (see Standby Mode section).

19

Measured at dc and applies in the selected pass band. PSRR at 50 Hz exceeds 120 dB, with filter notches of 25 Hz or 50 Hz. PSRR at 60 Hz exceeds 120 dB, with filter

notches of 20 Hz or 60 Hz.

20

PSRR depends on both gain and V

DD

, as follows:

Gain 1 2 4 8 to 128

V

DD

= 3 V 86 78 85 93

V

DD

= 5 V 90 78 84 91