3–14 Chapter 3: DC and Switching Characteristics for MAX V Devices

Timing Model and Specifications

MAX V Device Handbook May 2011 Altera Corporation

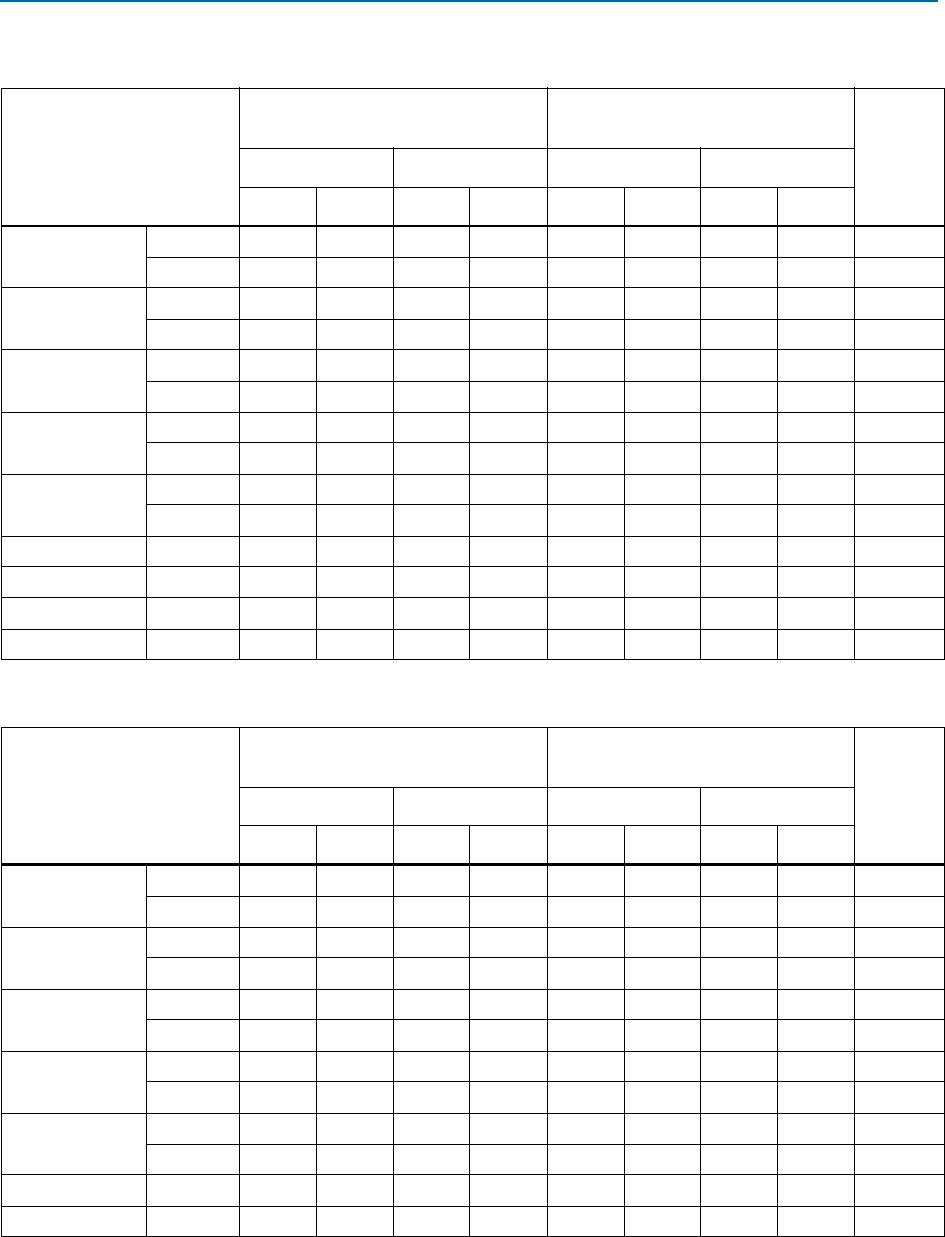

Table 3–20 through Ta bl e 3–2 3 list the adder delays for t

ZX

and t

XZ

microparameters

when using an I/O standard other than 3.3-V LVTTL with 16 mA drive strength.

Table 3–20. t

ZX

IOE Microparameter Adders for Fast Slew Rate for MAX V Devices

Standard

5M40Z/ 5M80Z/ 5M160Z/

5M240Z/ 5M570Z

5M1270Z/ 5M2210Z

Unit

C4 C5, I5 C4 C5, I5

Min Max Min Max Min Max Min Max

3.3-V LVTTL

16 mA —0 —0 —0 —0 ps

8 mA — 72 — 74 — 101 — 125 ps

3.3-V LVCMOS

8 mA —0 —0 —0 —0 ps

4 mA — 72 — 74 — 101 — 125 ps

2.5-V LVTTL /

LVCMOS

14 mA — 126 — 127 — 155 — 191 ps

7 mA — 196 — 197 — 545 — 671 ps

1.8-V LVTTL /

LVCMOS

6 mA — 608 — 610 — 721 — 888 ps

3 mA — 681 — 685 — 2012 — 2477 ps

1.5-V LVCMOS

4 mA — 1162 — 1157 — 1590 — 1957 ps

2 mA — 1245 — 1244 — 3269 — 4024 ps

1.2-V LVCMOS 3 mA — 1889 — 1856 — 2860 — 3520 ps

3.3-V PCI 20 mA — 72 — 74 — –18 — –22 ps

LVDS — — 126 — 127 — 155 — 191 ps

RSDS — — 126 — 127 — 155 — 191 ps

Table 3–21. t

ZX

IOE Microparameter Adders for Slow Slew Rate for MAX V Devices

Standard

5M40Z/ 5M80Z/ 5M160Z/

5M240Z/ 5M570Z

5M1270Z/ 5M2210Z

Unit

C4 C5, I5 C4 C5, I5

Min Max Min Max Min Max Min Max

3.3-V LVTTL

16 mA — 5,951 — 6,063 — 6,012 — 5,743 ps

8 mA — 6,534 — 6,662 — 8,785 — 8,516 ps

3.3-V LVCMOS

8 mA — 5,951 — 6,063 — 6,012 — 5,743 ps

4 mA — 6,534 — 6,662 — 8,785 — 8,516 ps

2.5-V LVTTL /

LVCMOS

14 mA — 9,110 — 9,237 — 10,072 — 9,803 ps

7 mA — 9,830 — 9,977 — 12,945 — 12,676 ps

1.8-V LVTTL /

LVCMOS

6 mA — 21,800 — 21,787 — 21,185 — 20,916 ps

3 mA — 23,020 — 23,037 — 24,597 — 24,328 ps

1.5-V LVCMOS

4 mA — 39,120 — 39,067 — 34,517 — 34,248 ps

2 mA — 40,670 — 40,617 — 39,717 — 39,448 ps

1.2-V LVCMOS 3 mA — 69,505 — 70,461 — 55,800 — 55,531 ps

3.3-V PCI 20 mA — 6,534 — 6,662 — 35 — 44 ps