3–22 Chapter 3: DC and Switching Characteristics for MAX V Devices

Timing Model and Specifications

MAX V Device Handbook May 2011 Altera Corporation

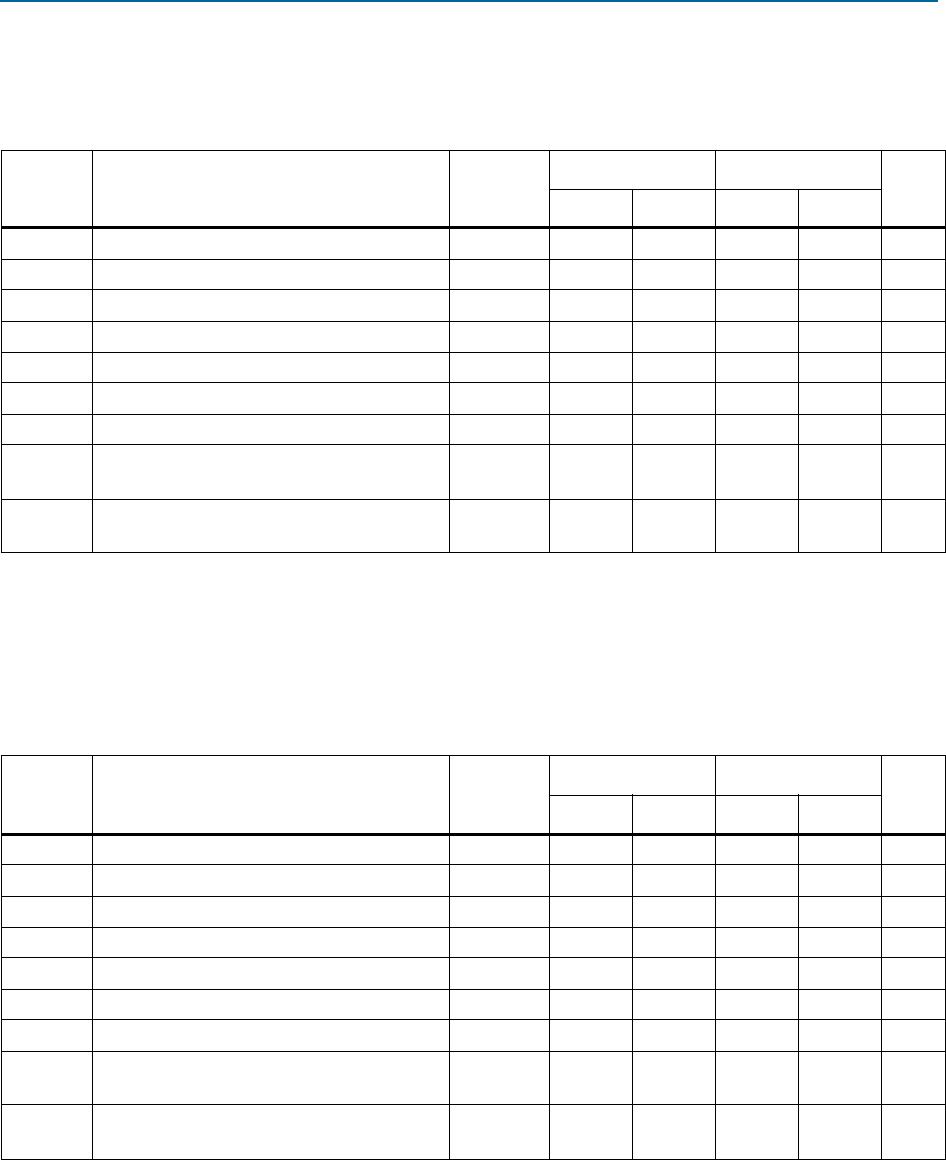

Table 3–30 lists the external I/O timing parameters for the F324 package of the

5M1270Z device.

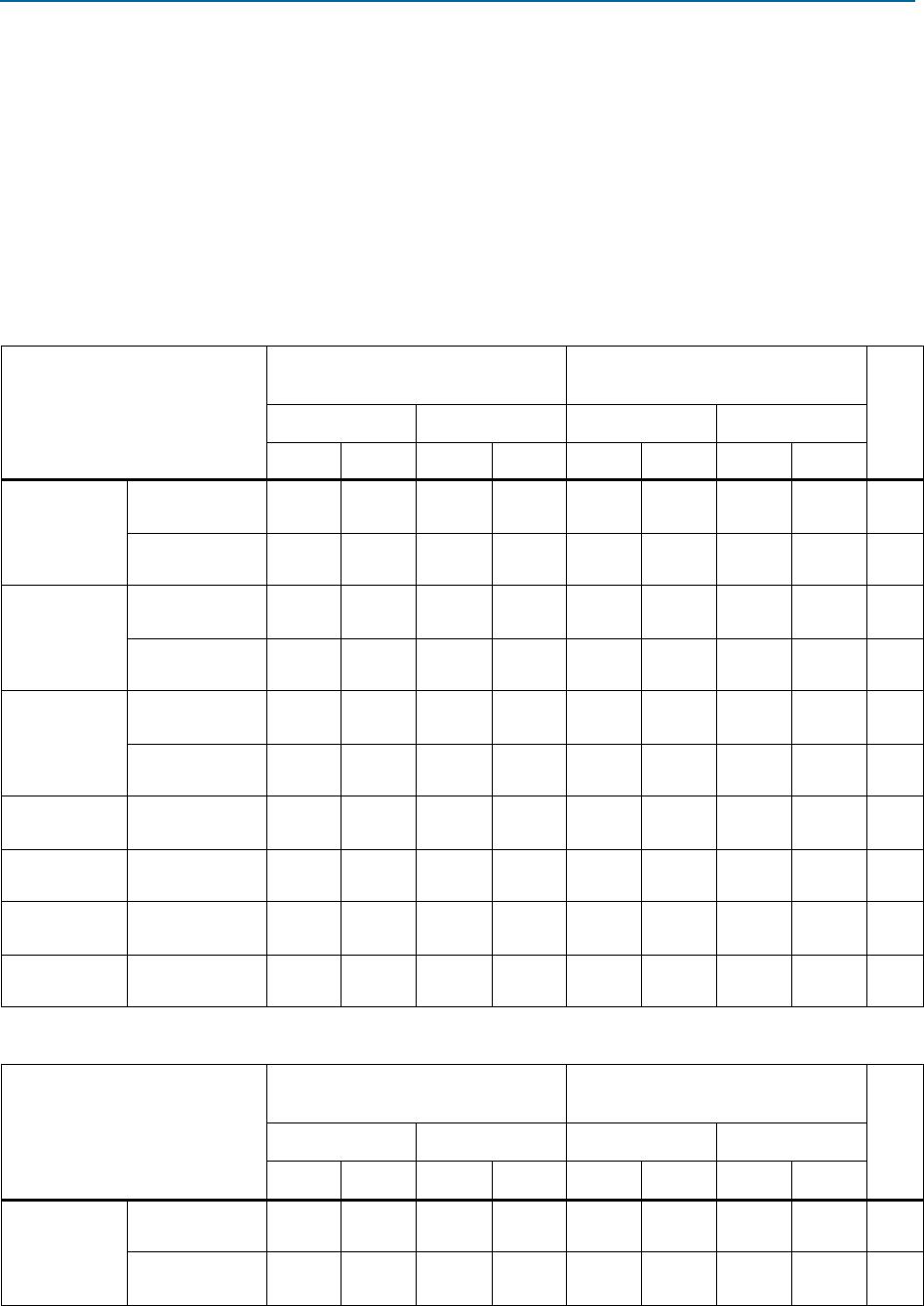

Table 3–31 lists the external I/O timing parameters for the 5M2210Z device.

Table 3–30. Global Clock External I/O Timing Parameters for the 5M1270Z Device (Note 1), (2)

Symbol Parameter Condition

C4 C5, I5

Unit

Min Max Min Max

t

PD1

Worst case pin-to-pin delay through one LUT 10 pF — 9.1 — 11.2 ns

t

PD2

Best case pin-to-pin delay through one LUT 10 pF — 4.8 — 5.9 ns

t

SU

Global clock setup time — 1.5 — 1.9 — ns

t

H

Global clock hold time — 0 — 0 — ns

t

CO

Global clock to output delay 10 pF 2.0 6.0 2.0 7.4 ns

t

CH

Global clock high time — 216 — 266 — ps

t

CL

Global clock low time — 216 — 266 — ps

t

CNT

Minimum global clock period for 16-bit

counter

— 4.0 — 5.0 — ns

f

CNT

Maximum global clock frequency for 16-bit

counter

— — 247.5 — 201.1 MHz

Notes to Table 3–30:

(1) The maximum frequency is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay performs faster than this global

clock input pin maximum frequency.

(2) Only applicable to the F324 package of the 5M1270Z device.

Table 3–31. Global Clock External I/O Timing Parameters for the 5M2210Z Device (Note 1)

Symbol Parameter Condition

C4 C5, I5

Unit

Min Max Min Max

t

PD1

Worst case pin-to-pin delay through one LUT 10 pF — 9.1 — 11.2 ns

t

PD2

Best case pin-to-pin delay through one LUT 10 pF — 4.8 — 5.9 ns

t

SU

Global clock setup time — 1.5 — 1.9 — ns

t

H

Global clock hold time — 0 — 0 — ns

t

CO

Global clock to output delay 10 pF 2.0 6.0 2.0 7.4 ns

t

CH

Global clock high time — 216 — 266 — ps

t

CL

Global clock low time — 216 — 266 — ps

t

CNT

Minimum global clock period for 16-bit

counter

— 4.0 — 5.0 — ns

f

CNT

Maximum global clock frequency for 16-bit

counter

— — 247.5 — 201.1 MHz

Note to Table 3–31:

(1) The maximum frequency is limited by the I/O standard on the clock input pin. The 16-bit counter critical delay performs faster than this global

clock input pin maximum frequency.