3–16 Chapter 3: DC and Switching Characteristics for MAX V Devices

Timing Model and Specifications

MAX V Device Handbook May 2011 Altera Corporation

1 The default slew rate setting for MAX V devices in the Quartus II design software is

“fast”.

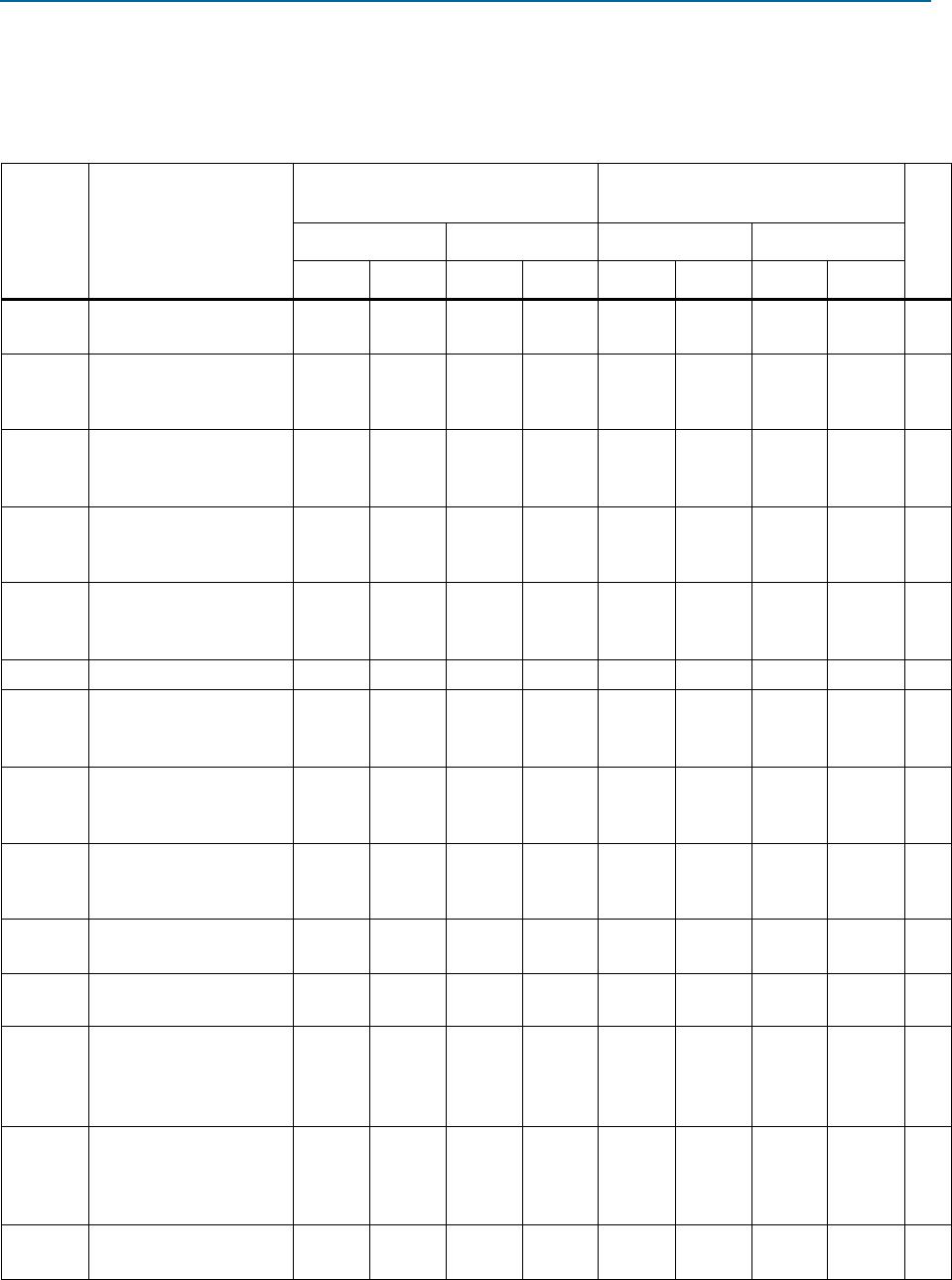

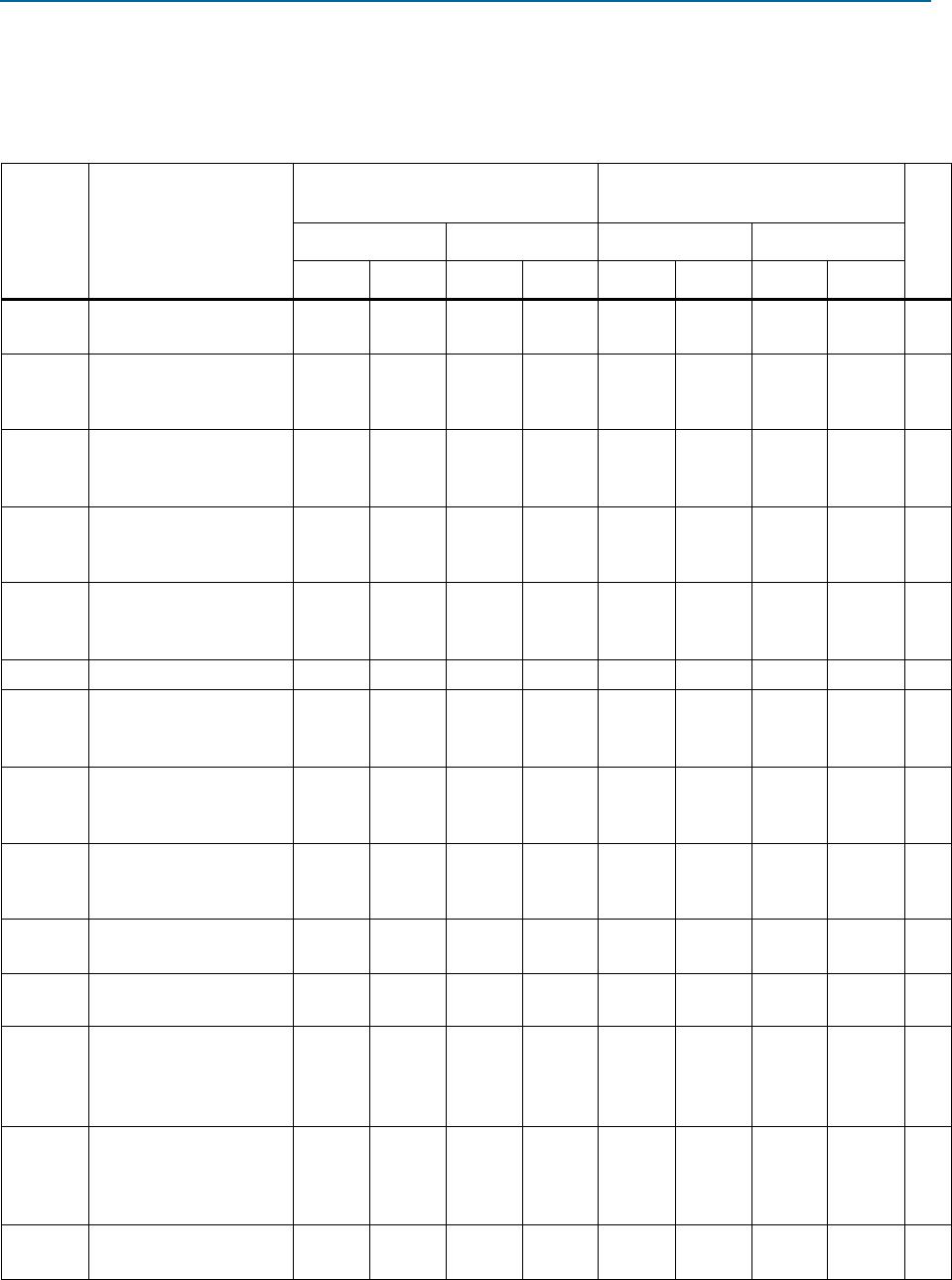

Table 3–24. UFM Block Internal Timing Microparameters for MAX V Devices (Part 1 of 2)

Symbol Parameter

5M40Z/ 5M80Z/ 5M160Z/

5M240Z/ 5M570Z

5M1270Z/ 5M2210Z

Unit

C4 C5, I5 C4 C5, I5

Min Max Min Max Min Max Min Max

t

ACLK

Address register clock

period

100 — 100 — 100 — 100 — ns

t

ASU

Address register shift

signal setup to address

register clock

20—20—20—20—ns

t

AH

Address register shift

signal hold to address

register clock

20—20—20—20—ns

t

ADS

Address register data in

setup to address register

clock

20—20—20—20—ns

t

ADH

Address register data in

hold from address

register clock

20—20—20—20—ns

t

DCLK

Data register clock period 100 — 100 — 100 — 100 — ns

t

DSS

Data register shift signal

setup to data register

clock

60—60—60—60—ns

t

DSH

Data register shift signal

hold from data register

clock

20—20—20—20—ns

t

DDS

Data register data in

setup to data register

clock

20—20—20—20—ns

t

DDH

Data register data in hold

from data register clock

20—20—20—20—ns

t

DP

Program signal to data

clock hold time

0—0—0—0—ns

t

PB

Maximum delay between

program rising edge to

UFM

busy

signal rising

edge

— 960 — 960 — 960 — 960 ns

t

BP

Minimum delay allowed

from UFM

busy

signal

going low to program

signal going low

20—20—20—20—ns

t

PPMX

Maximum length of

busy

pulse during a program

— 100 — 100 — 100 — 100 µs