LTC3300-1

38

33001fb

For more information www.linear.com/LTC3300-1

How to Calculate the CRC

One simple method of computing an n-bit CRC is to perform

arithmetic modulo-2 division of the n+1 bit characteristic

polynomial into the m bit message appended with n ze

-

ros (m+n bits). Arithmetic modulo-2 division resembles

normal long division absent borrows and carries. At each

intermediate step of the long division, if the leading bit

of the

dividend is a 1, a 1 is entered in the quotient and

the dividend is exclusive-ORed bitwise with the divisor. If

the leading bit of the dividend is a 0, a 0 is entered in the

quotient and the dividend is exclusive-ORed bitwise with

n zeros. This process is repeated m times. At the end of

the long division, the quotient is disregarded and the n-

bit remainder is the CRC. This will be more clear in the

example to follow.

For the CRC implementation in the LTC3300-1, n = 4 and

m = 12. The characteristic polynomial employed is x

4

+ x

+ 1, which is shorthand for 1x

4

+ 0x

3

+ 0x

2

+ 1x

1

+ 1x

0

,

resulting in 10011 for the divisor. The message is the first

12 bits of the balance command. Suppose for example the

APPLICATIONS INFORMATION

desired balance command calls for simultaneous charging

of Cell 1 and synchronous discharging of Cell4. The 12-bit

message (MSB first) will be 110000010000. Appending

4 zeros results in 1100000100000000 for the dividend.

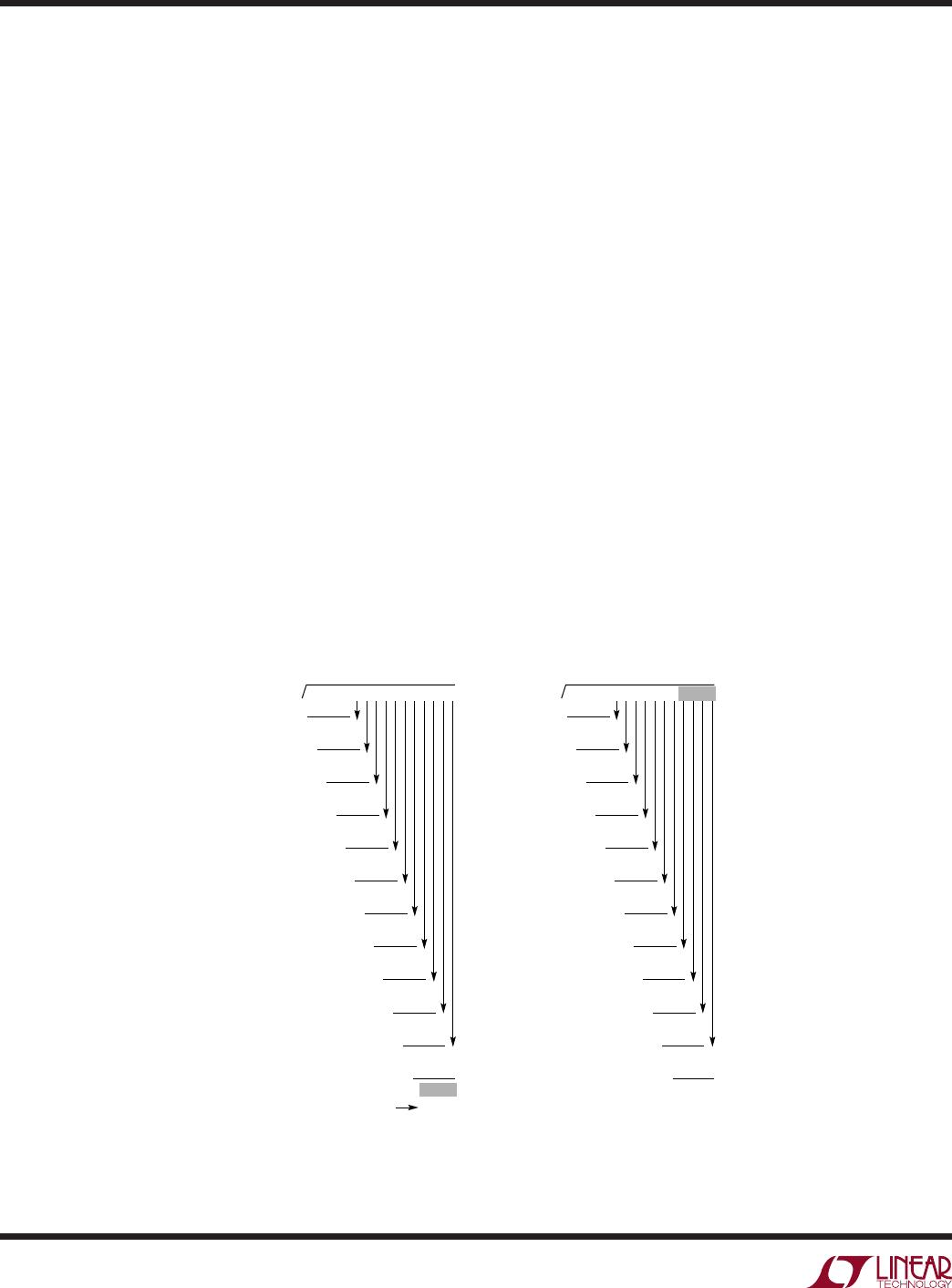

The long division is shown in Figure 16a with a resultant

CRC of 1101. Note that the CRC bits in the write balance

command are inverted. Thus the correct 16-bit balance

command is 1100000100000010. Figure16b shows the

same long division procedure being used to check the

CRC of data (command or status) read back from the

LTC3300-1. In this scenario, the remainder after the long

division must be zero (0000) for the data to be valid. Note

that the readback CRC bits must be inverted in the dividend

before performing the division.

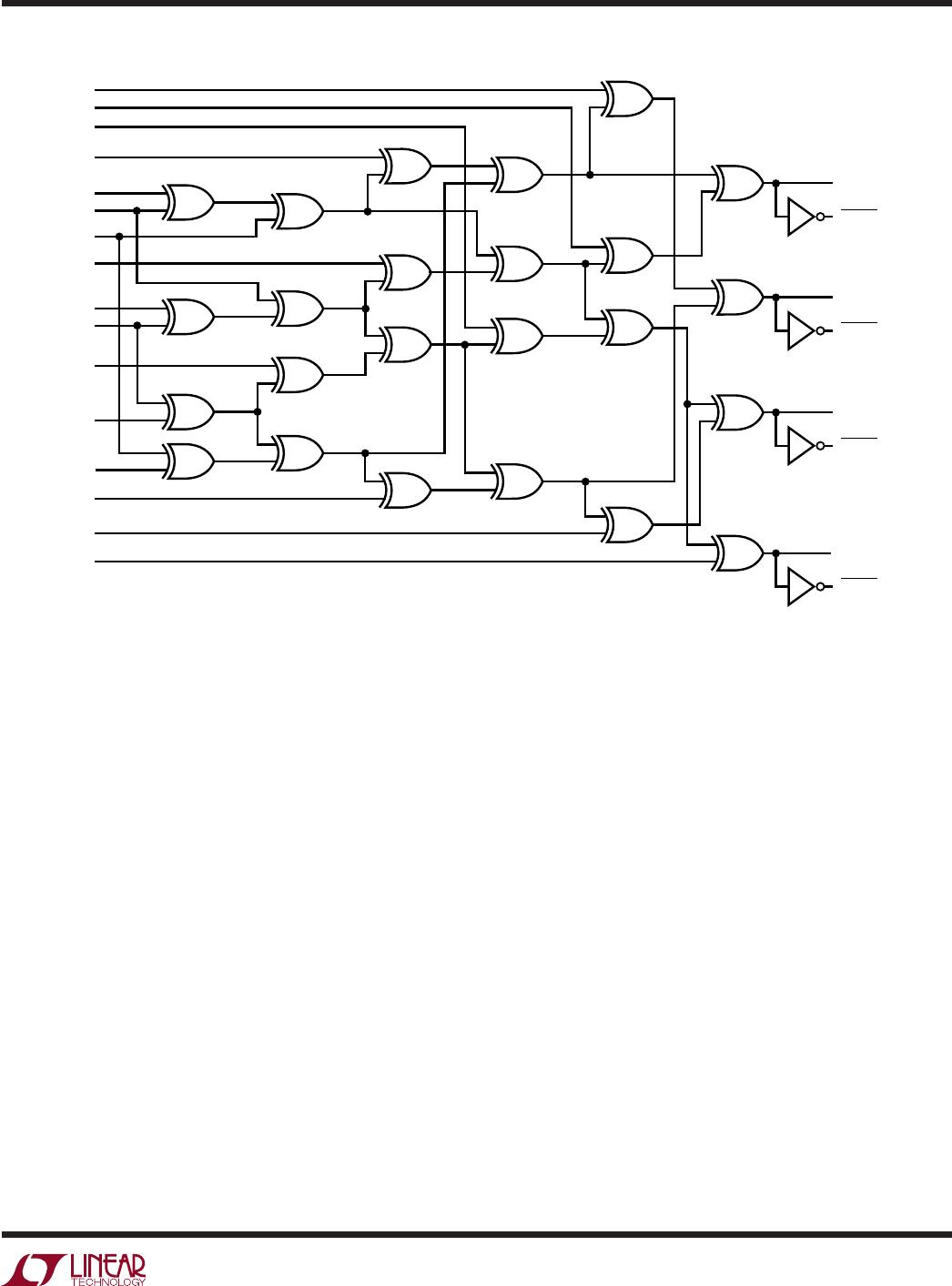

An alternate method to calculate the CRC is shown in

Figure 17 in which the balance command bits are input to

a combinational logic circuit comprised solely of 2-input

exclusive-OR gates. This “brute force” implementation is

easily replicated in a few lines of C code.

Figure 16. (a) Long Division Example to Calculate CRC for

Writes. (b) Long Division Example to Check CRC for Reads

1 1 0 1 0 1 1 0 1 0 1 1

1 0 0 1 1 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0

1 0 0 1 1

1 0 1 1 0

1 0 0 1 1

0 1 0 1 0

0 0 0 0 0

1 0 1 0 1

1 0 0 1 1

0 1 1 0 0

0 0 0 0 0

1 1 0 0 0

1 0 0 1 1

1 0 1 1 0

1 0 0 1 1

0 1 0 1 0

0 0 0 0 0

1 0 1 0 0

1 0 0 1 1

0 1 1 1 0

0 0 0 0 0

1 1 1 0 0

1 0 0 1 1

1 1 1 1 0

1 0 0 1 1

REMAINDER = 1 1 0 1 = 4-BIT CRC

1 1 0 1 0 1 1 0 1 0 1 1

1 0 0 1 1 1 1 0 0 0 0 0 1 0 0 0 0 1 1 0 1

1 0 0 1 1

1 0 1 1 0

1 0 0 1 1

0 1 0 1 0

0 0 0 0 0

1 0 1 0 1

1 0 0 1 1

0 1 1 0 0

0 0 0 0 0

1 1 0 0 0

1 0 0 1 1

1 0 1 1 0

1 0 0 1 1

0 1 0 1 0

0 0 0 0 0

1 0 1 0 1

1 0 0 1 1

0 1 1 0 1

0 0 0 0 0

1 1 0 1 0

1 0 0 1 1

1 0 0 1 1

1 0 0 1 1

REMAINDER = 0

33001 F16

0 0 1 0 = 4-BIT CRC INVERTED

READBACK = 1100000100000010

DIVIDEND = 1100000100001101

(b)(a)