Feature Capability

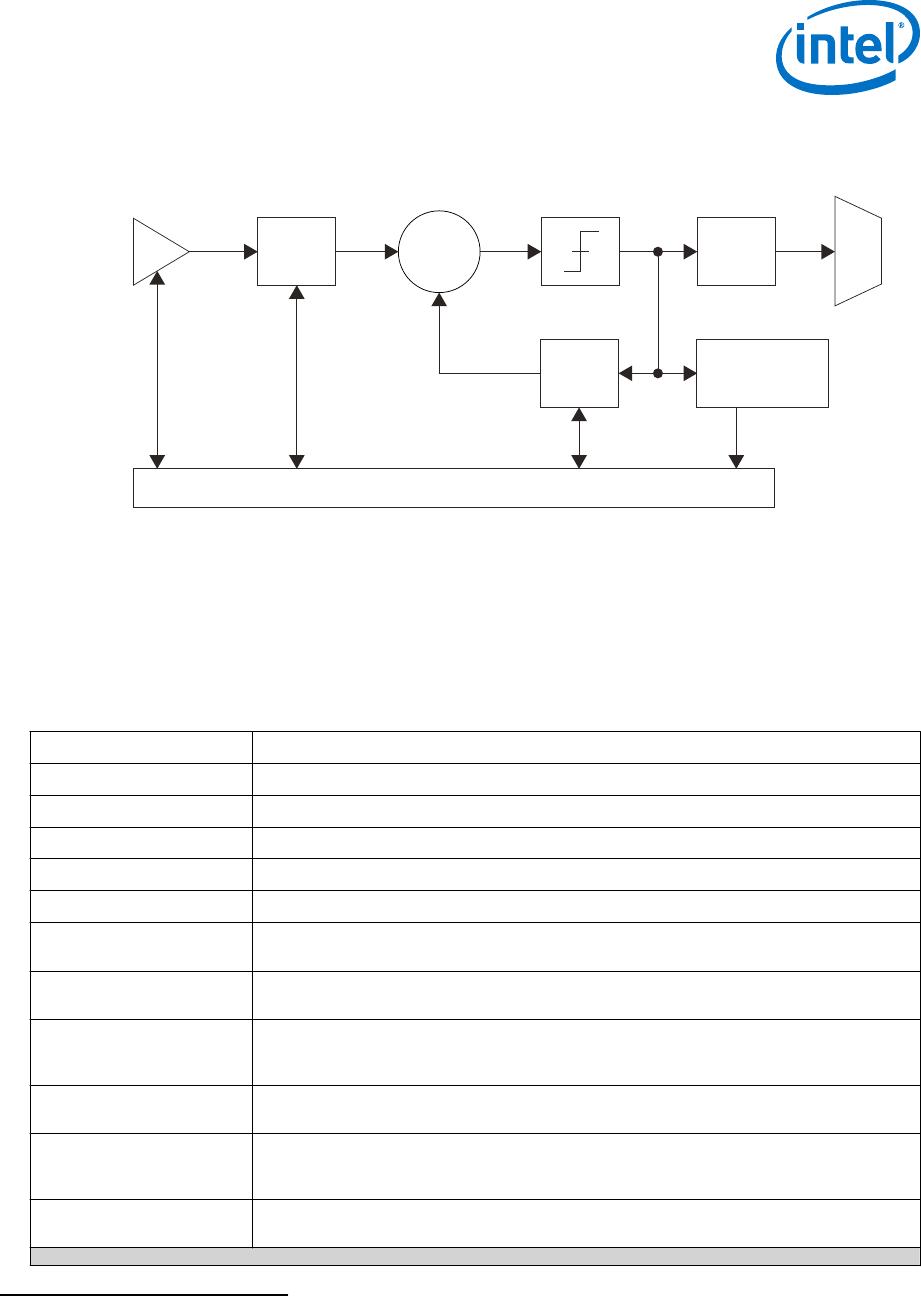

Digitally Assisted Analog

CDR

Superior jitter tolerance with fast lock time

On-Die Instrumentation—

Eye Viewer and Jitter Margin

Tool

Simplify board bring-up, debug, and diagnostics with non-intrusive, high-resolution eye

monitoring (Eye Viewer). Also inject jitter from transmitter to test link margin in system.

Dynamic Reconfiguration Allows for independent control of each transceiver channel Avalon memory-mapped

interface for the most transceiver flexibility.

Multiple PCS-PMA and PCS-

Core to FPGA fabric interface

widths

8-, 10-, 16-, 20-, 32-, 40-, or 64-bit interface widths for flexibility of deserialization width,

encoding, and reduced latency

1.8.2. PCS Features

Intel Stratix 10 PMA channels interface with core logic through configurable and

bypassable PCS interface layers.

The PCS contains multiple gearbox implementations to decouple the PMA and PCS

interface widths. This feature provides the flexibility to implement a wide range of

applications with 8, 10, 16, 20, 32, 40, or 64-bit interface width between each

transceiver and the core logic.

The PCS also contains hard IP to support a variety of standard and proprietary

protocols across a wide range of data rates and encoding schemes. The Standard PCS

mode provides support for 8B/10B encoded applications up to 12.5 Gbps. The

Enhanced PCS mode supports 64B/66B and 64B/67B encoded applications up to 17.4

Gbps. The enhanced PCS mode also includes an integrated 10GBASE-KR/40GBASE-

KR4 Forward Error Correction (FEC) circuit. For highly customized implementations, a

PCS Direct mode provides an interface up to 64 bits wide to allow for custom encoding

and support for data rates up to 28.3 Gbps.

For more information about the PCS-Core interface or the double rate transfer mode,

refer to the Intel Stratix 10 L- and H-Tile Transceiver PHY User Guide, and the Intel

Stratix 10 E-Tile Transceiver PHY User Guide.

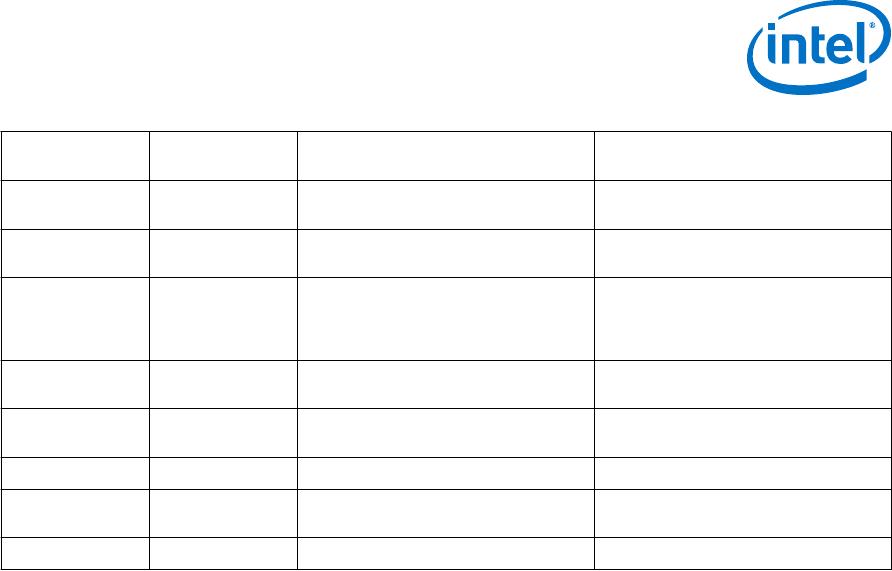

Table 9. Transceiver PCS Features

PCS Protocol

Support

Data Rate (Gbps) Transmitter Data Path Receiver Data Path

Standard PCS 1 to 12.5 Phase compensation FIFO, byte

serializer, 8B/10B encoder, bit-slipper,

channel bonding

Rate match FIFO, word-aligner, 8B/10B

decoder, byte deserializer, byte

ordering

PCI Express

Gen1/Gen2 x1,

x2, x4, x8, x16

2.5 and 5.0 Same as Standard PCS plus PIPE 2.0

interface to core

Same as Standard PCS plus PIPE 2.0

interface to core

PCI Express Gen3

x1, x2, x4, x8,

x16

8.0 Phase compensation FIFO, byte

serializer, encoder, scrambler, bit-

slipper, gear box, channel bonding, and

PIPE 3.0 interface to core, auto speed

negotiation

Rate match FIFO (0-600 ppm mode),

word-aligner, decoder, descrambler,

phase compensation FIFO, block sync,

byte deserializer, byte ordering, PIPE

3.0 interface to core, auto speed

negotiation

CPRI 0.6144 to 9.8 Same as Standard PCS plus

deterministic latency serialization

Same as Standard PCS plus

deterministic latency deserialization

continued...

1. Intel

®

Stratix

®

10 GX/SX Device Overview

S10-OVERVIEW | 2018.08.08

Stratix 10 GX/SX Device Overview

20