14

INDUSTRIAL TEMPERATURE RANGE

IDT5V9885T

3.3V EEPROM PROGRAMMABLE CLOCK GENERATOR

GIN2 Pin GIN1 Pin GIN0 Pin PLL0 Configuration Selection (Mode 1)

0 0 0 Configuration 0

0 0 1 Configuration 1

0 1 0 Configuration 2

0 1 1 Configuration 3

1 0 0 Configuration 4

1 0 1 Configuration 5

1 1 0 Configuration 6

1 1 1 Configuration 7

CONFIGURING THE MULTI-PURPOSE I/Os

The 5V9885T can operate in four distinct modes. These modes are controlled by the MFC bit (0x04) and the I

2

C/JTAG pin. The general purpose I/O pins

(GIN0, GIN1, GIN2, GIN3, GIN4, GIN5) have different uses depending on the mode of operation. The four available modes of operation are:

1) Manual Frequency Control (MFC) Mode for PLL0 Only

2) Manual Frequency Control (MFC) Mode for all three PLLs

3) I

2

C Programming Mode

4) JTAG Programming Mode

Along with the GINx pins are also GOUTx output pins that can take up a different function depending on the mode of operation. See table below for description.

Each PLL's programming registers can store up to four different Dx and Mx configurations in combination with two different P configurations in MFC modes.

The post-divider should never be disabled in any of the two P configurations unless the output bank will never be used during normal operation. The PLL's

loop filter settings also has four different configurations to store and select from. This will be explained in the MODE1 and MODE2 sections. The use of the GINx

pins in MFC mode control the selection of these configurations.

MODE1 - Manual Frequency Control (MFC=1) Mode for PLL0 Only

In this mode, only 8 configurations of PLL0 can be changed during operation. The GIN0, GIN1 and GIN2 pins control the selection of eight different

configurations (D, M, Rz, Cz, Cp and Ip) of PLL0. GIN3 becomes PLL SUSPEND pin, GIN4 is not available to users, and GIN5 becomes CLK_SEL pin.

The output GOUT0 will become an indicator for loss of PLL lock (LOSS_LOCK). GOUT1 pin will become an indicator for loss of the primary clock

(LOSS_CLKIN).

The PLL0 has 4 sets of dedicated registers for D, M, Rz, Cz, Cp, Ip and ODIV. For additional 4 sets of registers, the PLL0 uses registers from CONFIG2

and CONFIG3 of PLL1 and PLL2. The PLL1 and PLL2 will still be fully operational, but have only one fixed configuration in this mode, and the default

configuration will be set to CONFIG0 of PLL1 and CONFIG0 of PLL2. (Please see page 18 for register location.)

The output banks will each have two P configurations that can be associated with each of the PLL configurations. Each of the two P configurations has its

own set of PM bits (See the PRE-SCALERS, FEEDBACK-DIVIDERS, POST-DIVIDERS section for more detail on the PM bits). Use the ODIV bit to

choose which post-divider configuration to associate with a specific PLL configuration.

To enter this mode, users must set MFC bit to “1”, and I2C/JTAG pin must be left floating.

NOTE:

1. Please see detail description in Loss of Lock and Input Clock section.

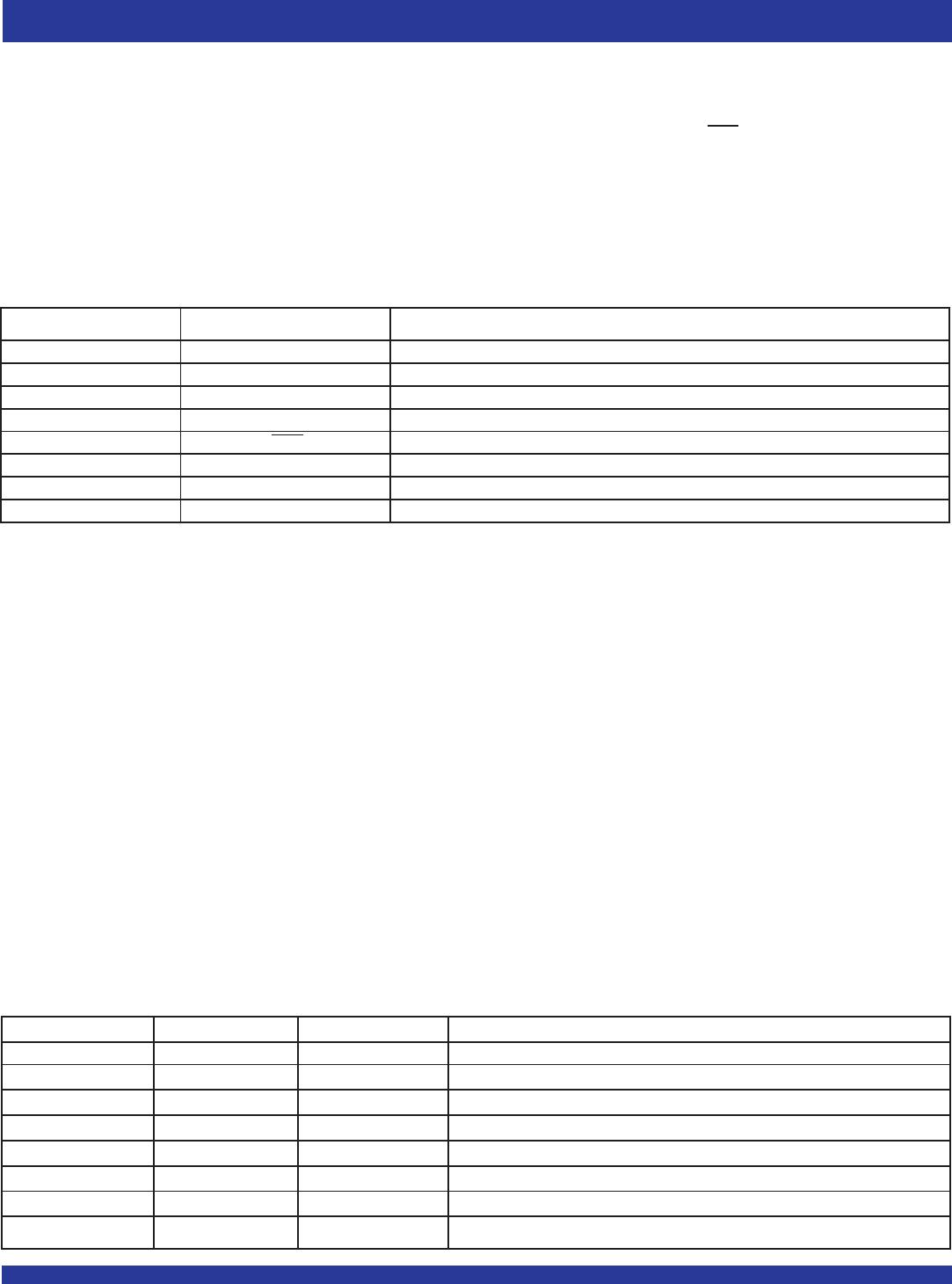

Multi-Purpose Pins Other Signal Functions Signal Description

GIN0 SDAT / TDI I

2

C serial data input / JTAG serial data input

GIN1 SCLK / TCK I

2

C clock input / JTAG clock input

GIN2 TMS JTAG control signal to the TAP controller state machine

GIN3 SUSPEND Suspends all outputs of PLL (Active High)

GIN4 TRST JTAG active LOW input to asynchronously reset the BST

GIN5 CLK_SEL Reference clock select between XTALIN/REFIN and CLKIN

GOUT0 TDO / LOSS_LOCK JTAG serial data output / Detects loss of PLL lock

(1)

GOUT1 LOSS_CLKIN Detects loss of the primary clock source

(1)