26

INDUSTRIAL TEMPERATURE RANGE

IDT5V9885T

3.3V EEPROM PROGRAMMABLE CLOCK GENERATOR

I

2

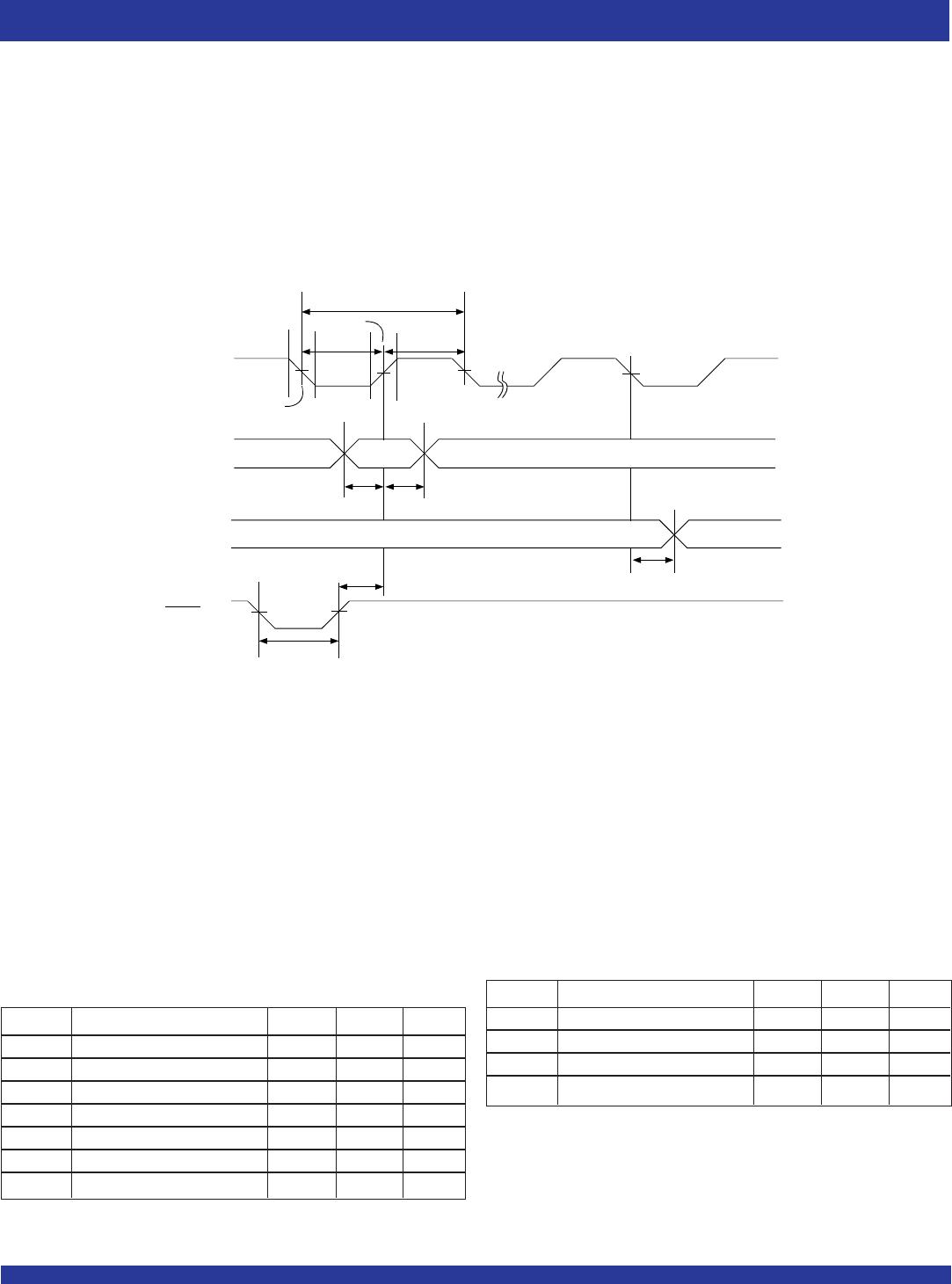

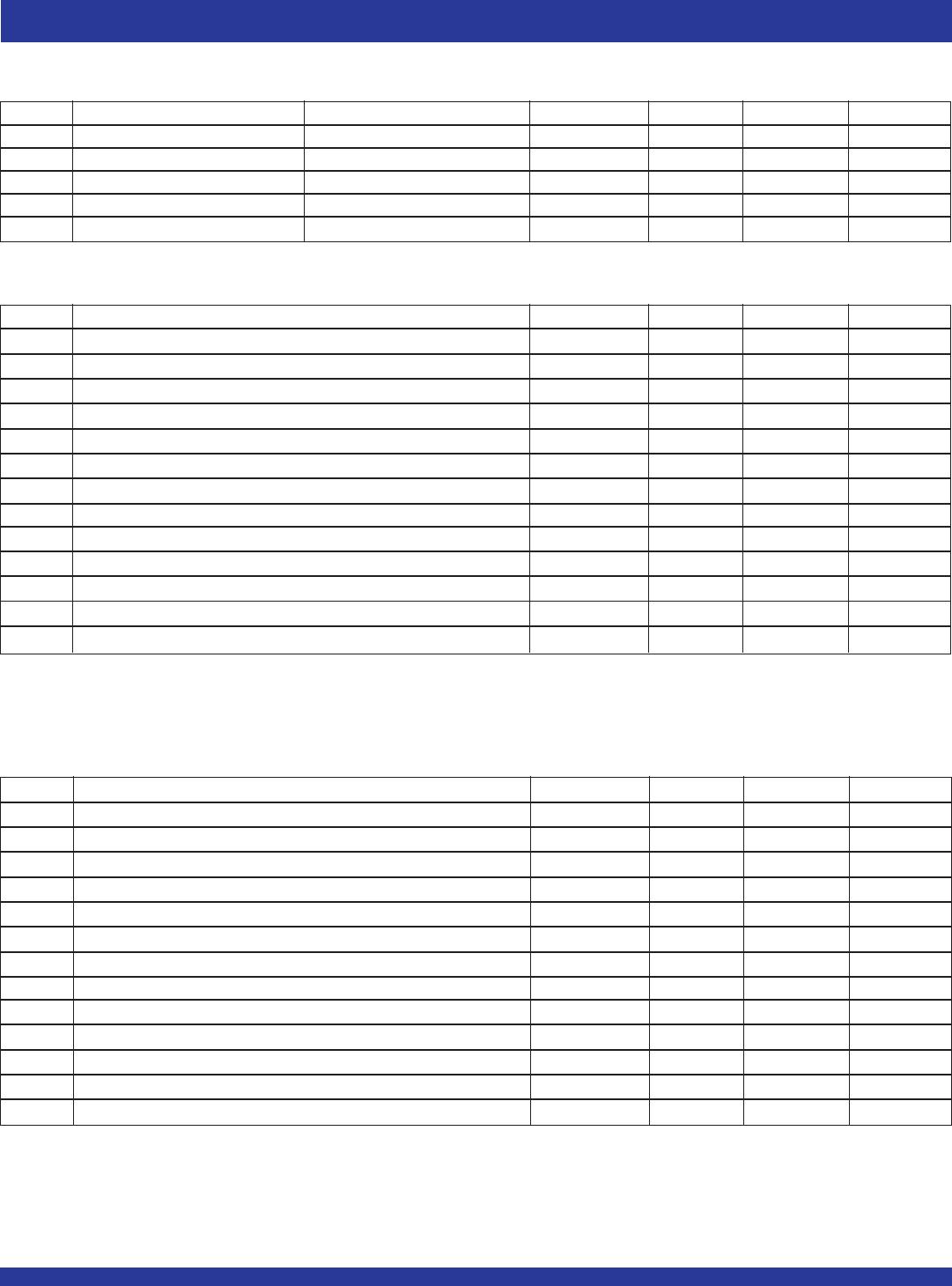

C BUS DC CHARACTERISTICS

Symbol Parameter Conditions Min Typ Max Unit

VIH Input HIGH Level 0.7 * VDD V

VIL Input LOW Level 0.3 * VDD V

VHYS Hysteresis of Inputs 0.05 * VDD V

IIN Input Leakage Current ±1.0 μA

VOL Output LOW Voltage IOL = 3 mA 0.4 V

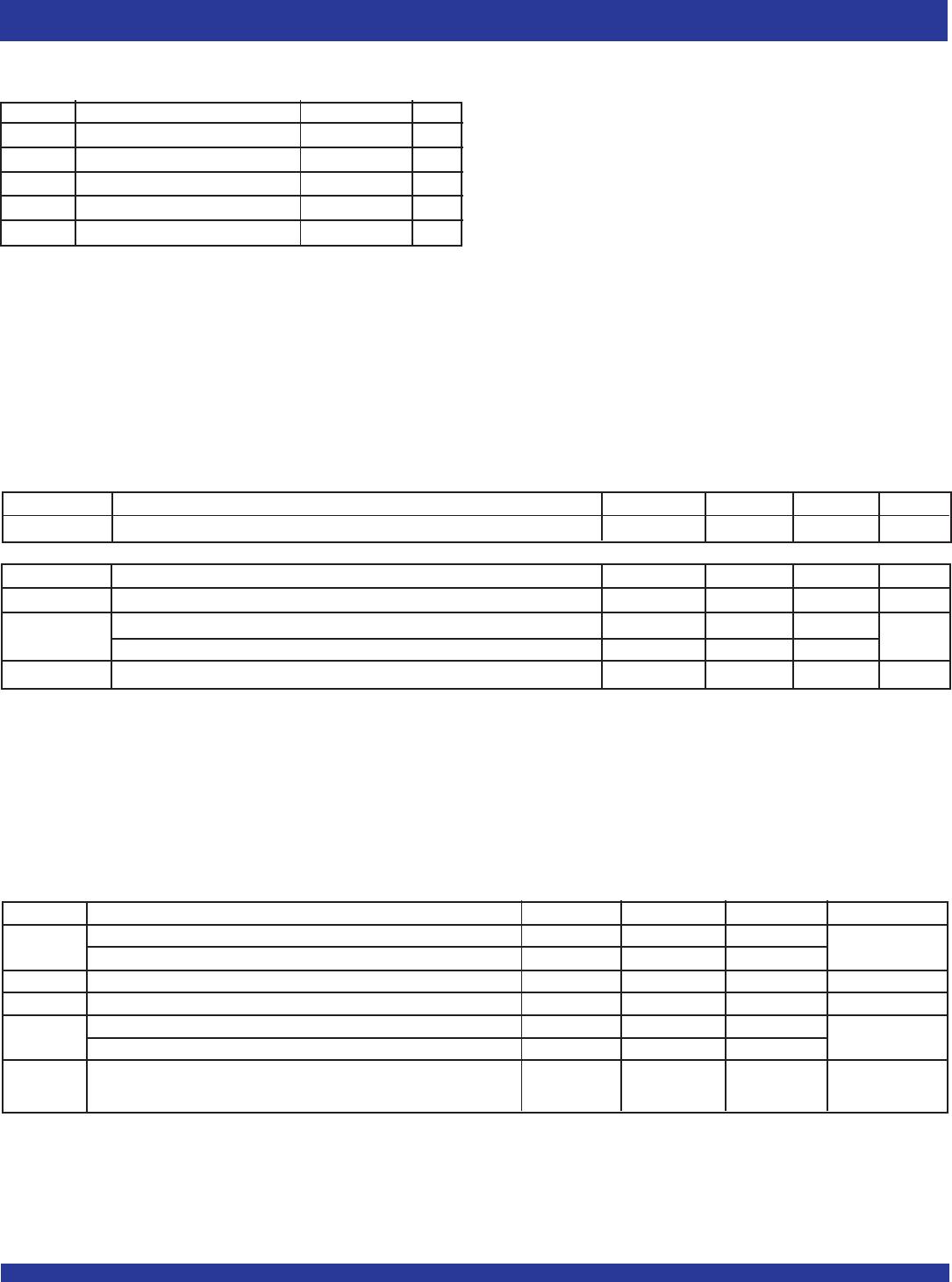

I

2

C BUS AC CHARACTERISTICS FOR STANDARD MODE

Symbol Parameter Min Typ Max Unit

FSCLK Serial Clock Frequency (SCLK) 0 100 KHz

tBUF Bus free time between STOP and START 4.7 μs

tSU:START Setup Time, START 4.7 μs

tHD:START Hold Time, START 4 μs

tSU:DATA Setup Time, data input (SDAT) 250 ns

tHD:DATA Hold Time, data input (SDAT)

(1)

0 μs

tOVD Output data valid from clock 3.45 μs

CB Capacitive Load for Each Bus Line 400 pF

tR Rise Time, data and clock (SDAT, SCLK) 1000 ns

tF Fall Time, data and clock (SDAT, SCLK) 300 ns

tHIGH HIGH Time, clock (SCLK) 4 μs

tLOW LOW Time, clock (SCLK) 4.7 μs

t

SU:STOP Setup Time, STOP 4 μs

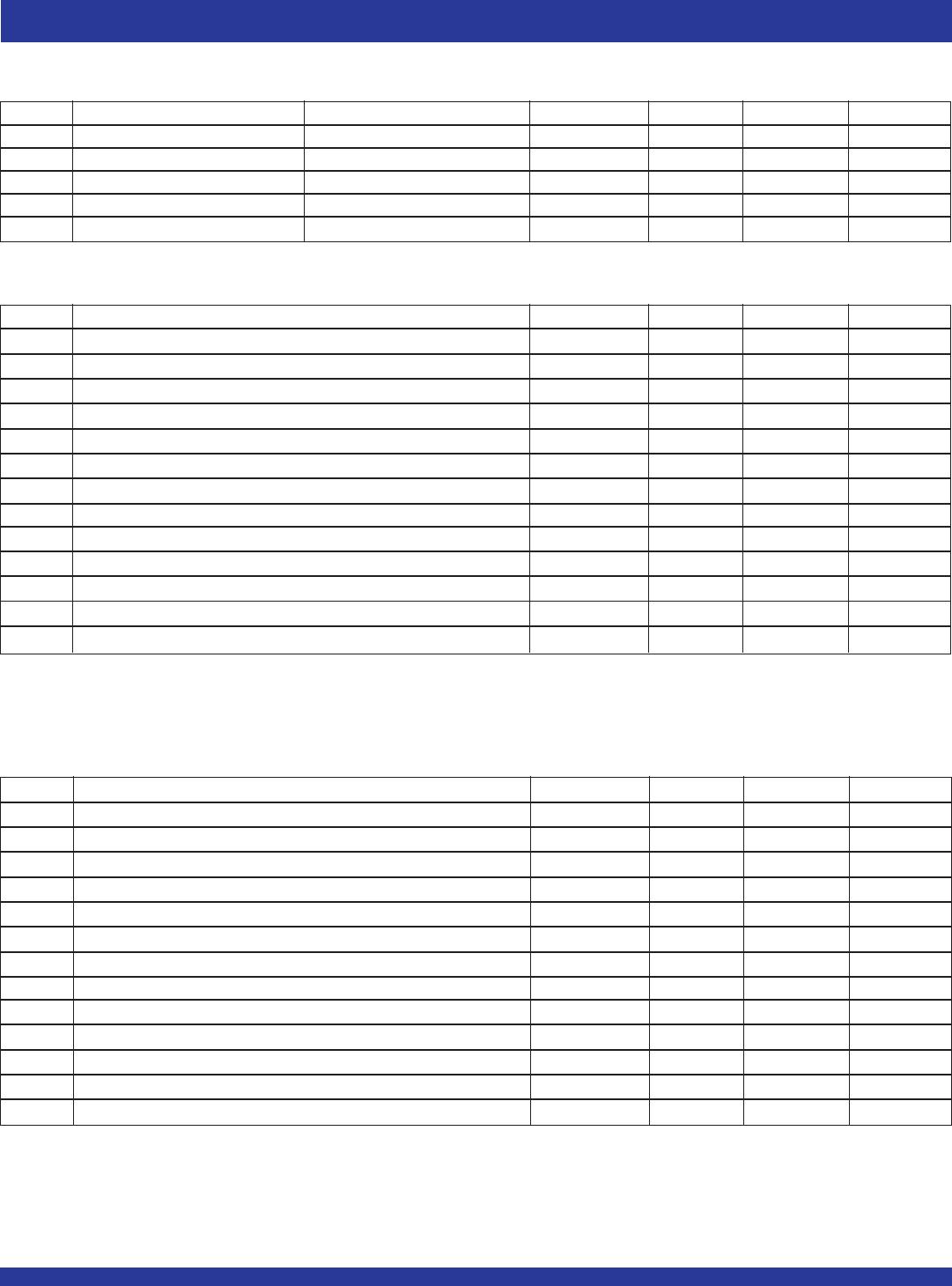

I

2

C BUS AC CHARACTERISTICS FOR FAST MODE

Symbol Parameter Min Typ Max Unit

FSCLK Serial Clock Frequency (SCLK) 0 400 KHz

tBUF Bus free time between STOP and START 1.3 μs

tSU:START Setup Time, START 0.6 μs

tHD:START Hold Time, START 0.6 μs

tSU:DATA Setup Time, data input (SDAT) 100 ns

tHD:DATA Hold Time, data input (SDAT)

(1)

0 μs

tOVD Output data valid from clock 0.9 μs

CB Capacitive Load for Each Bus Line 400 pF

tR Rise Time, data and clock (SDAT, SCLK) 20 + 0.1 * CB 300 ns

tF Fall Time, data and clock (SDAT, SCLK) 20 + 0.1 * CB 300 ns

tHIGH HIGH Time, clock (SCLK) 0.6 μs

tLOW LOW Time, clock (SCLK) 1.3 μs

t

SU:STOP Setup Time, STOP 0.6 μs

NOTE:

1. A device must internally provide a hold time of at least 300ns for the SDAT signal (referred to the VIHMIN of the SCLK signal) to bridge the undefined region of the falling edge

of SCLK.

NOTE:

1. A device must internally provide a hold time of at least 300ns for the SDAT signal (referred to the VIHMIN of the SCLK signal) to bridge the undefined region of the falling edge

of SCLK.