30

INDUSTRIAL TEMPERATURE RANGE

IDT5V9885T

3.3V EEPROM PROGRAMMABLE CLOCK GENERATOR

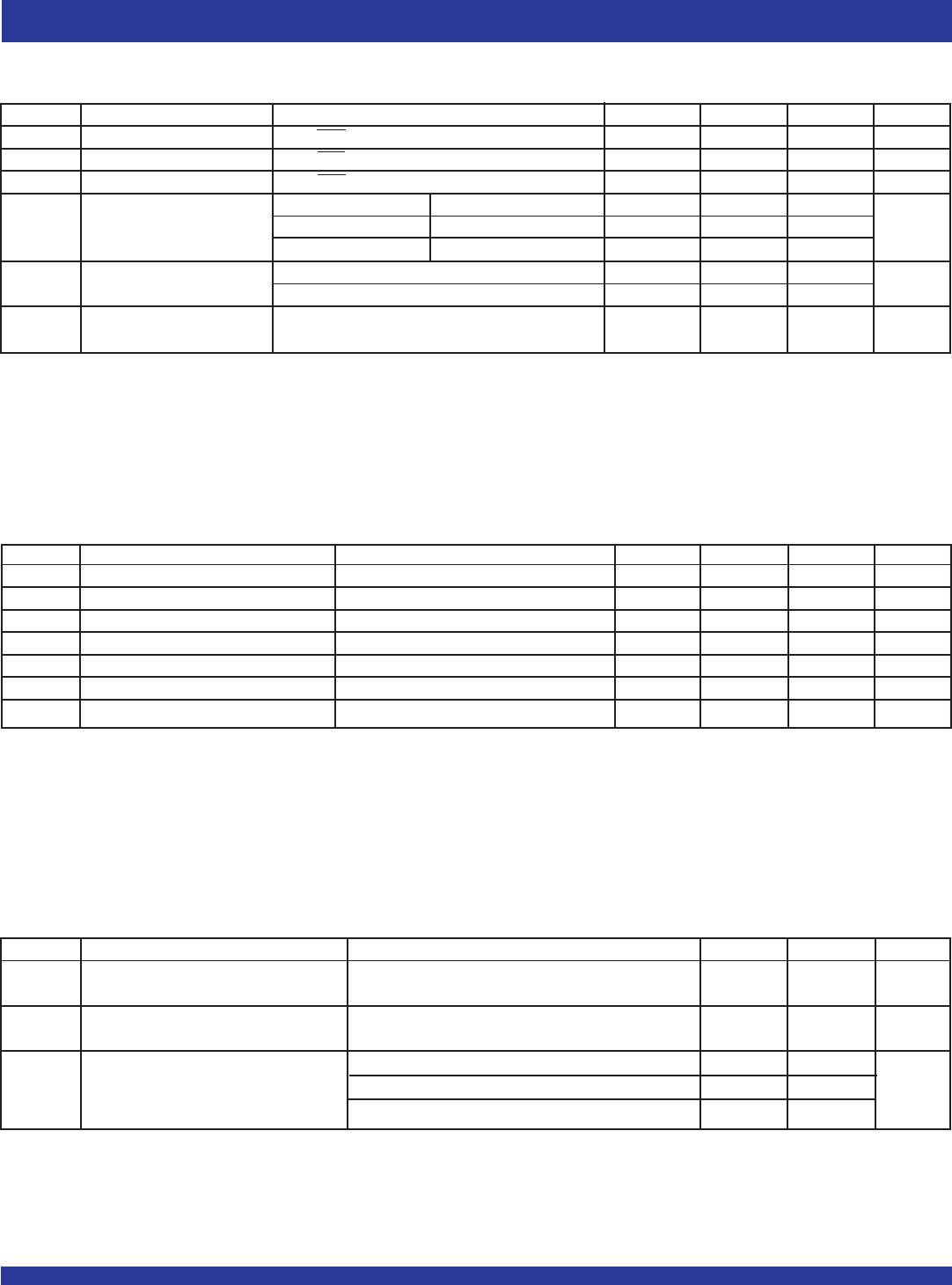

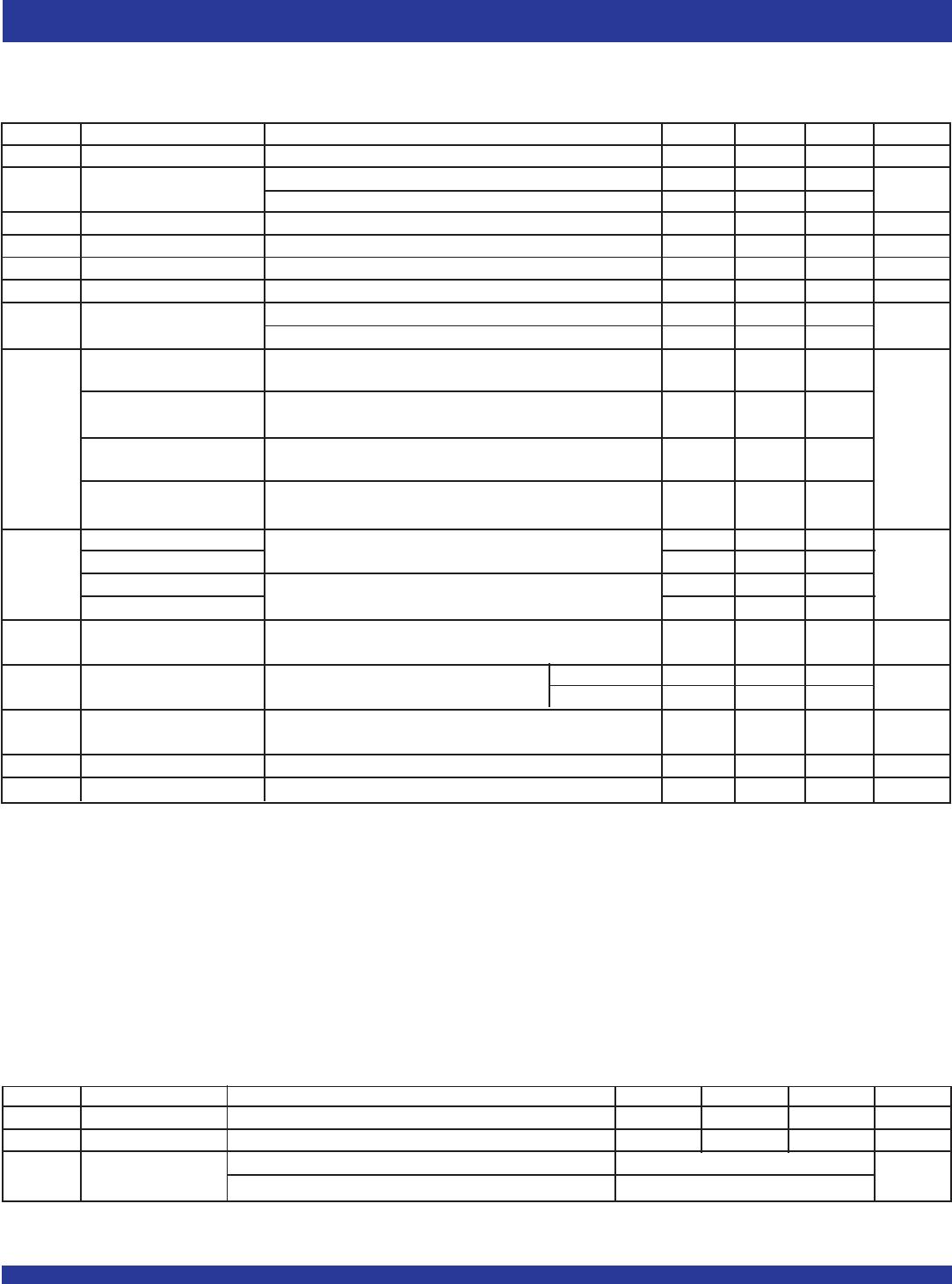

AC TIMING ELECTRICAL CHARACTERISTICS

(SPREAD SPECTRUM GENERATION = OFF)

Symbol Parameter Test Conditions Min. Typ. Max Unit

fIN Input Frequency Input Frequency Limit 1

(1)

— 400 MH z

1/t1 Output Frequency Single Ended Clock output limit (LVTTL) 0.0049 — 200 MHz

Differential Clock output limit (LVPECL/ LVDS) 0.0049 — 500

fVCO VCO Frequency VCO operating Frequency Range 10 — 1200 MHz

fPFD PFD Frequency PFD operating Frequency Range 0.4

(1)

— 400 MH z

fBW Loop Bandwidth Based on loop filter resistor and capacitor values 0.03 — 40 MHz

t2 Input Duty Cycle Duty Cycle for Input 40 — 60 %

t3 Output Duty Cycle Measured at V

DD/2, FOUT ≤ 200MHz 45 — 55 %

Measured at VDD/2, FOUT > 200MHz 40 — 60

Slew Rate Single-Ended Output clock rise and fall time, — 2.75 —

SLEWx(bits) = 00 20% to 80% of V

DD (Output Load = 15pf)

Slew Rate Single-Ended Output clock rise and fall time, — 2 —

t4

(2)

SLEWx(bits) = 01 20% to 80% of VDD (Output Load = 15pf) V/ns

Slew Rate Single-Ended Output clock rise and fall time, — 1.25 —

SLEWx(bits) = 10 20% to 80% of VDD (Output Load = 15pf)

Slew Rate Single-Ended Output clock rise and fall time, — 0.75 —

SLEWx(bits) = 11 20% to 80% of VDD (Output Load = 15pf)

Rise Times LVDS, 20% to 80% — 850 —

t5 Fall Times — 850 — ps

Rise Times LVPECL, 20% to 80% — 500 —

Fall Times — 500 —

t6 Output three-state Timing Time for output to enter or leave three-state mode — — 150 + ns

after SHUTDOWN/OE switches 1/FOUTX

t7 Clock Jitter

(3,7)

Peak-to-peak period jitter, fPFD > 20MHz — — 150 ps

CLK outputs measured at VDD/2 fPFD < 20MHz — 200 —

t8 Output Skew Skew between output to output on the same bank — — 150 ps

(bank 4 and bank 5 only)

(4, 5)

t9 Lock Time PLL Lock Time from Power-up

(6)

—1020ms

t10 Lock time

(8)

PLL Lock time from shutdown mode — 20 100 μs

NOTES:

1. Practical lower input frequency is determined by loop filter settings.

2. A slew rate of 2V/ns or greater should be selected for output frequencies of 100MHz and higher.

3. Input frequency is the same as the output with all output banks running at the same frequency.

4. Skew measured between all in-phase outputs in the same bank.

5. Skew measured between the cross points of all differential output pairs under identical input and output interfaces, transitions and load conditions on any one device.

6. Includes loading the configuration bits from EEPROM to PLL registers. It does not include EEPROM programming/write time.

7. Guaranteed by design but not production tested. Actual jitter performance may vary depending on the configuration.

8. Actual PLL lock time depends on the loop configuration.

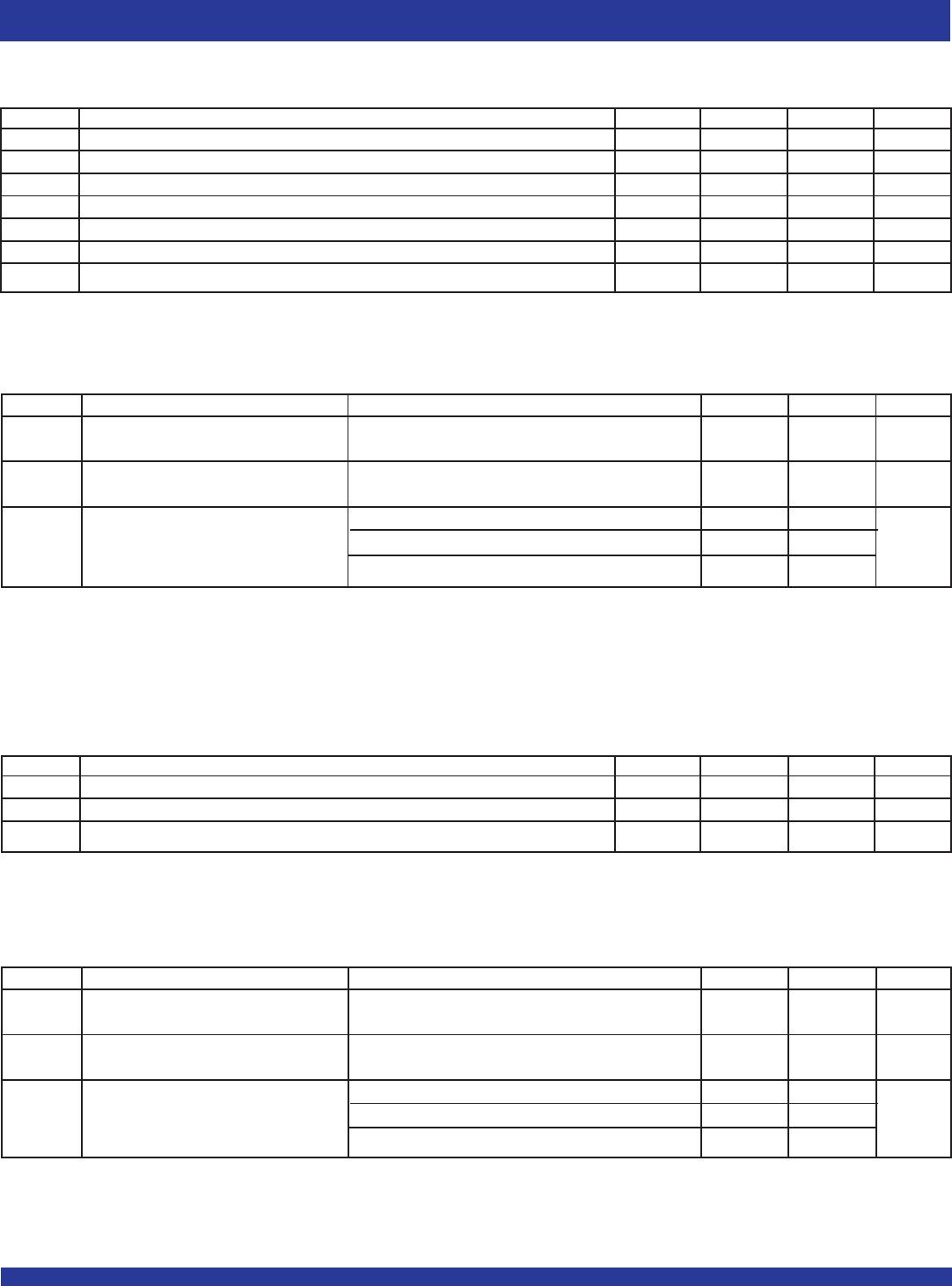

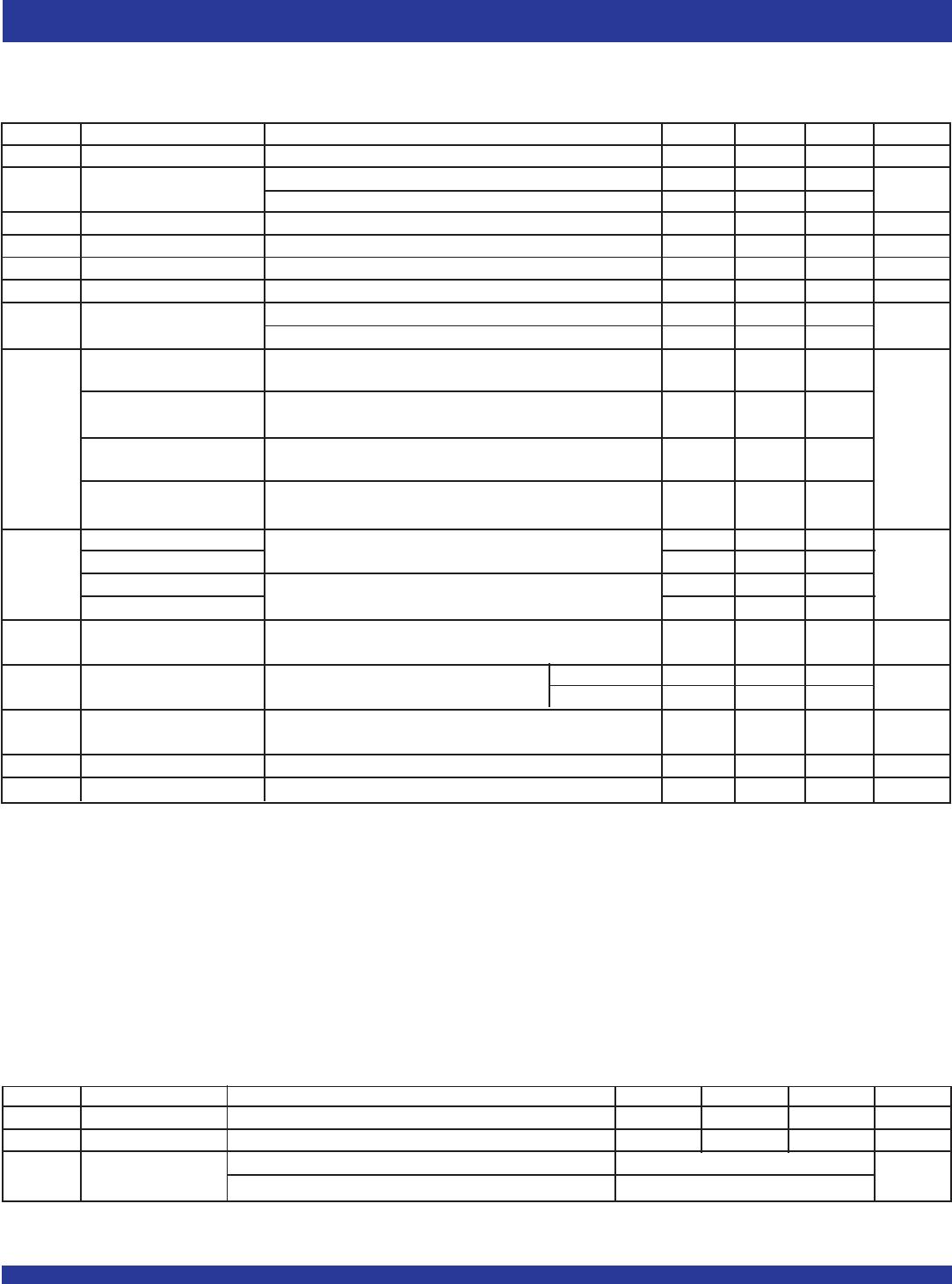

SPREAD SPECTRUM GENERATION SPECIFICATIONS

Symbol Parameter Description Min. Typ. Max Unit

fIN Input Frequency Input Frequency Limit 1

(1)

— 400 MHz

fMOD Mod Freq Modulation Frequency — 33 — k Hz

f

SPREAD Spread Value Amount of Spread Value (Programmable) - Down Spread -0.5, -1, -2.5, -3.5, -4 %fOUT

Amount of Spread Value (Programmable) - Center Spread -2.0 to +2.0

NOTE:

1. Practical lower input frequency is determined by loop filter settings.