WM8737L Production Data

w

PD, Rev 4.4, January 2012

10

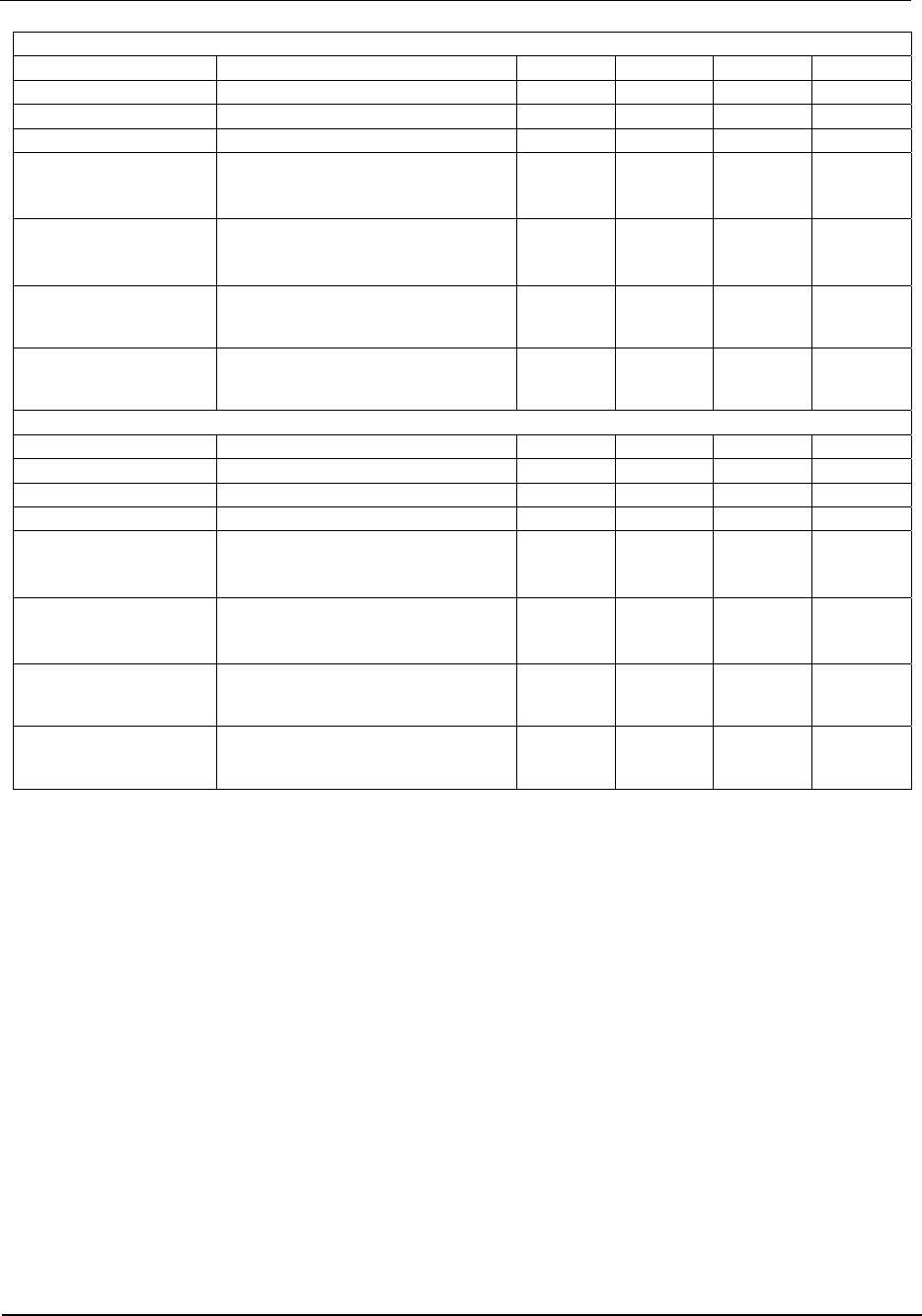

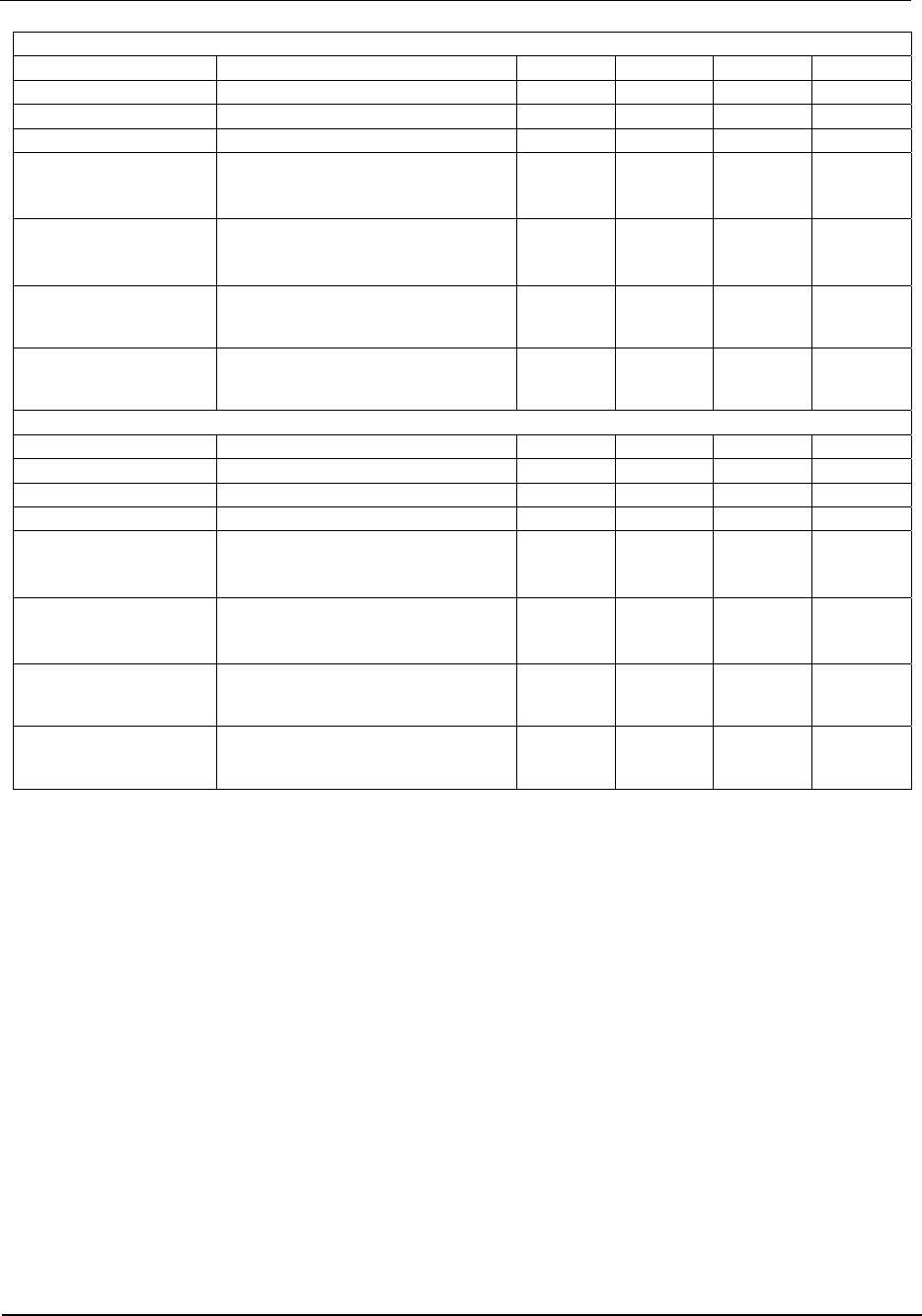

MVDD = 1.8V, AVDD = 1.8V, DBVDD = 1.8V, DCVDD = 1.5V, Normal Power Mode, no MICBIAS or mic preamps

OFF 000000000

0.000 0.000 0.007 0.011

Standby 110000000

0.698 0.004 0.069 1.367

Mono (L/R) 111101000 / 111010100

3.453 0.010 1.910 9.098

Stereo / Digital Mono Mix 111111100

6.109 0.017 1.955 13.959

Analogue mono mix

(without dc monitoring via

Right ADC)

111111000

4.574 0.010 1.910 11.116

Analogue mono mix

(with continuous dc

monitoring via Right ADC)

111111100

6.109 0.017 1.940 13.937

Using MICBIAS in 0.9 X

AVDD mode in addition to

any of the above

Set appropriate MICBIAS[1:0] bits in

power management register

+0.252 - - +0.454

Using microphone boost

preamplifiers in addition to

any of the above

Set appropriate MBCTRL[1:0] bits in

register 09h and set LMBE and/or RMBE

bits in registers 02h and 03h

+0.738 - - +1.328

MVDD = 3.3V, AVDD = 3.3V, DBVDD = 3.3V, DCVDD = 1.5V, Normal Power Mode, no MICBIAS or mic preamps

OFF 000000000

0.001 0.000 0.007 0.014

Standby 110000000

1.288 0.007 0.064 4.371

Mono (L/R) 111101000 / 111010100

4.632 0.020 1.905 18.210

Stereo / Digital Mono Mix 111111100

7.750 0.032 1.950 28.606

Analogue mono mix

(without dc monitoring via

Right ADC)

111111000

5.996 0.020 1.890 22.688

Analogue mono mix

(with continuous dc

monitoring via Right ADC)

111111100

7.750 0.033 1.960 28.624

Using MICBIAS in 0.9 X

AVDD mode in addition to

any of the above

Set appropriate MICBIAS[1:0] bits in

power management register

+0.446 - - +1.472

Using microphone boost

preamplifiers in addition to

any of the above

Set appropriate MBCTRL[1:0] bits in

register 09h and set LMBE and/or RMBE

bits in registers 02h and 03h

+1.406 - - +4.640

Table 1 Supply Current Consumption (see also “Power Management” section)

Notes:

1. T

A

= +25

o

C, Slave Mode, fs = 48kHz, MCLK = 12.288 MHz (256fs), 24-bit data

2. All figures are quiescent, with no signal.