Production Data WM8737L

w

PD, Rev 4.4, January 2012

19

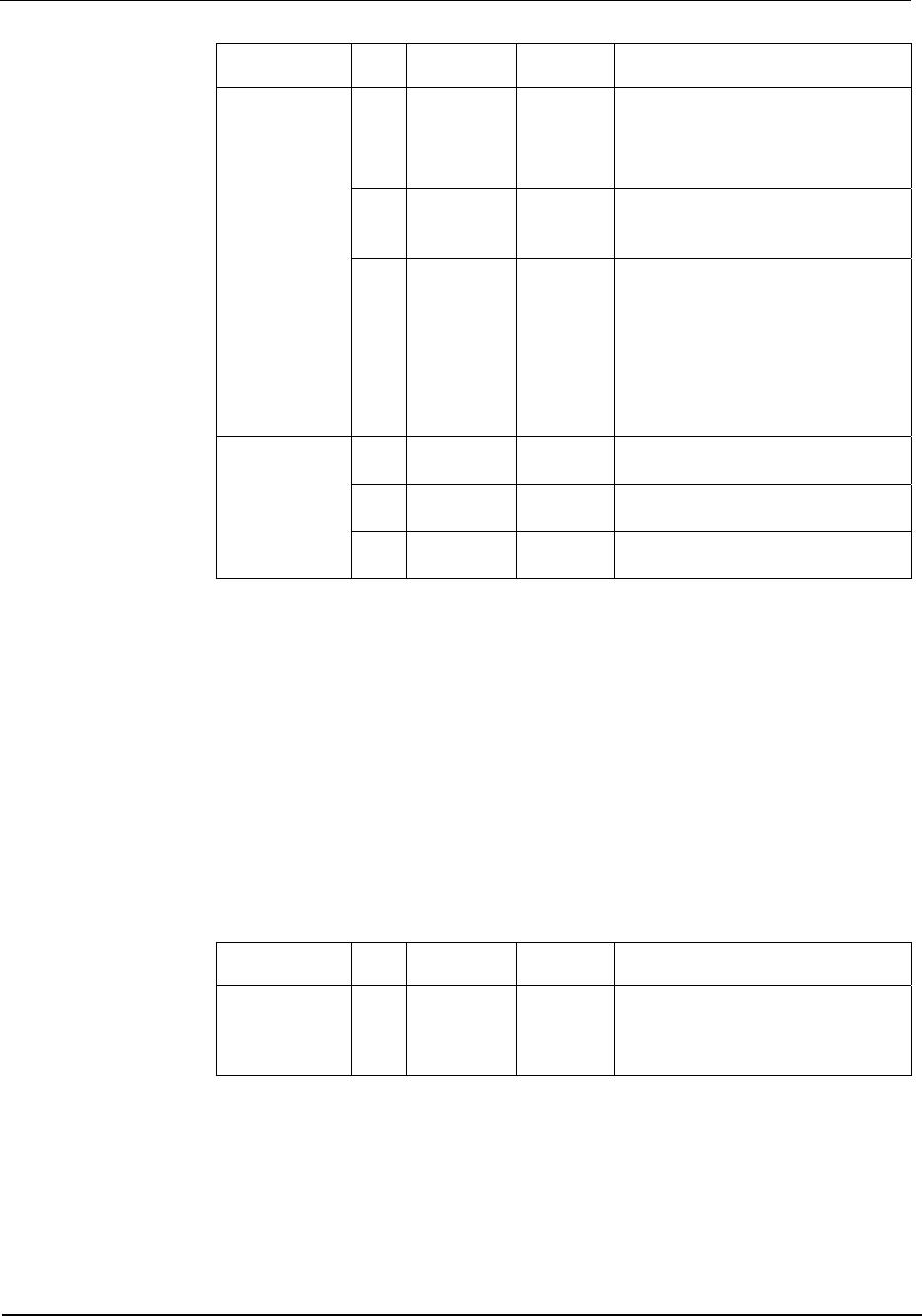

REGISTER

ADDRESS

BIT LABEL DEFAULT DESCRIPTION

R2 (02h)

Audio Path Left

3

LMZC None (first

gain

change

would

overwrite!)

Left Mic preamp Zero-Cross Enable

0: Change gain immediately

1: Change gain on zero crossing only

2

LPZC 1 Left PGA Zero-Cross Enable

0: Change gain immediately

1: Change gain on zero crossing only

1:0

LZCTO[1:0] 11 Left Zero-Cross Time-Out

00: 256/fs

01: 512/fs

10: 1024/fs

11: 2048/fs (42.67ms at 48kHz)

This timeout applies to both the PGA

and mic preamp zero-cross watchdog

timers.

R3 (03h)

Audio Path

Right

3

RMZC None Right Mic preamp Zero-Cross Enable

Same as LMZC but for right channel

2

RPZC 1 Right PGA Zero-Cross Enable

Same as LMZC but for right channel

1:0

RZCTO[1:0] 11 Right Zero-Cross Time-Out

Same as LMZC but for right channel

Table 8 Zero-Cross Detection Control

ANALOGUE TO DIGITAL CONVERTER (ADC)

The WM8737L uses a multi-bit, oversampled sigma-delta ADC for each channel. The use of multi-bit

feedback and high oversampling rates reduces the effects of jitter and high frequency noise. The ADC

full-scale input level is proportional to AVDD. With a 3.3V supply voltage the full scale level is 1.0 Volt

rms (+/-1.414 Volts peak). Any voltage greater than full-scale will overload the ADC and cause

distortion.

ADC THD+N VERSUS POWER CONTROL

The ADCs can be operated in ‘normal mode’, which offers best THD+N performance at the cost of

highest power dissipation, or in ‘low power mode’ which offers significant power savings at the cost of

slightly reduced THD+N performance. The ADCs operating mode is controlled by the LP bit in register

R5. USB mode is not compatible with low power mode, so the LP bit must be set to 0 if USB mode is

selected.

See the ‘Power Consumption’ section for power requirements in both modes.

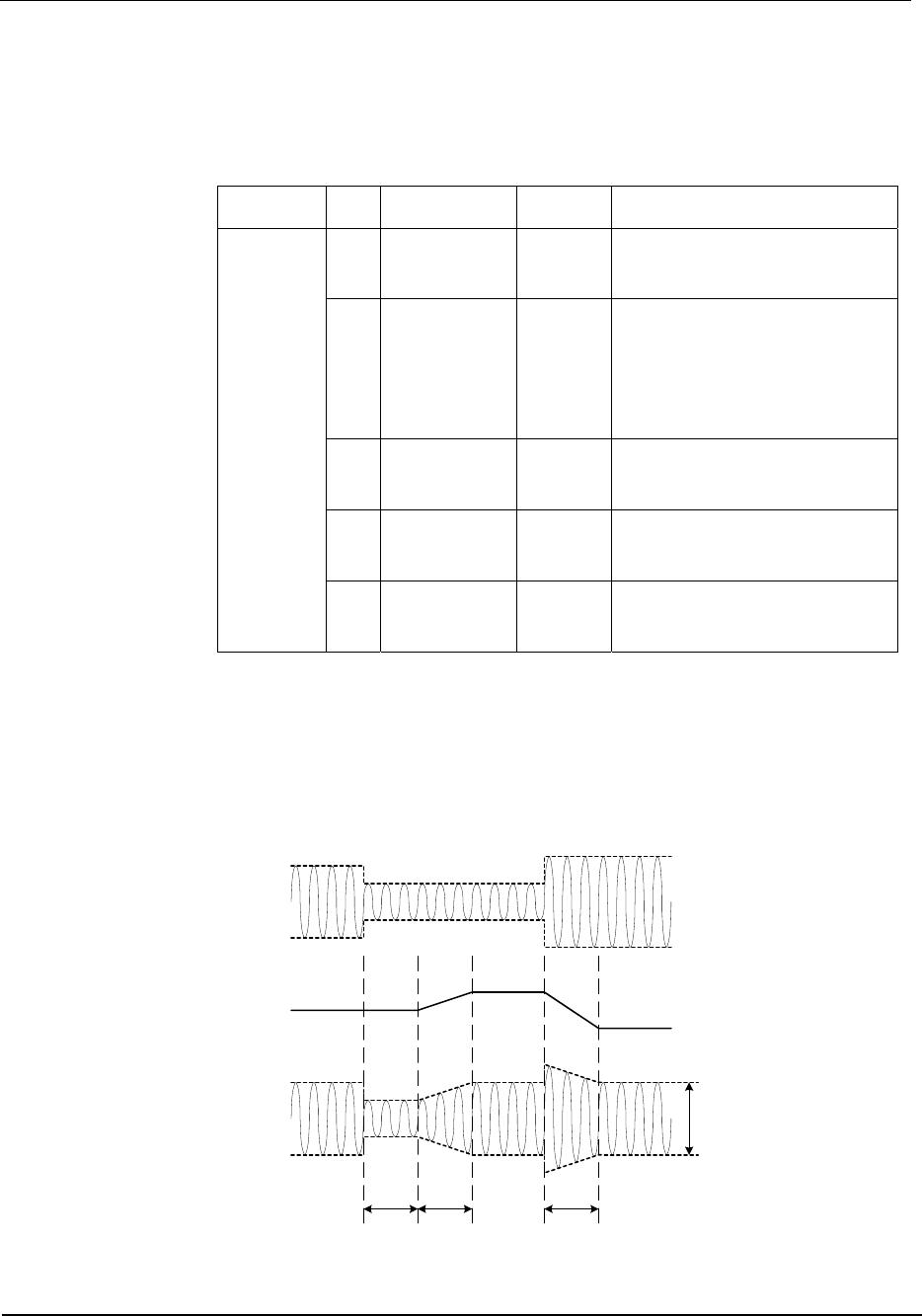

REGISTER

ADDRESS

BIT LABEL DEFAULT DESCRIPTION

R5 (05h)

ADC Control

2

LP 0 ADC power mode control

0: Both ADCs in normal mode (best

THD+N)

1: Both ADCs in low power mode

Table 9 ADC Power Control

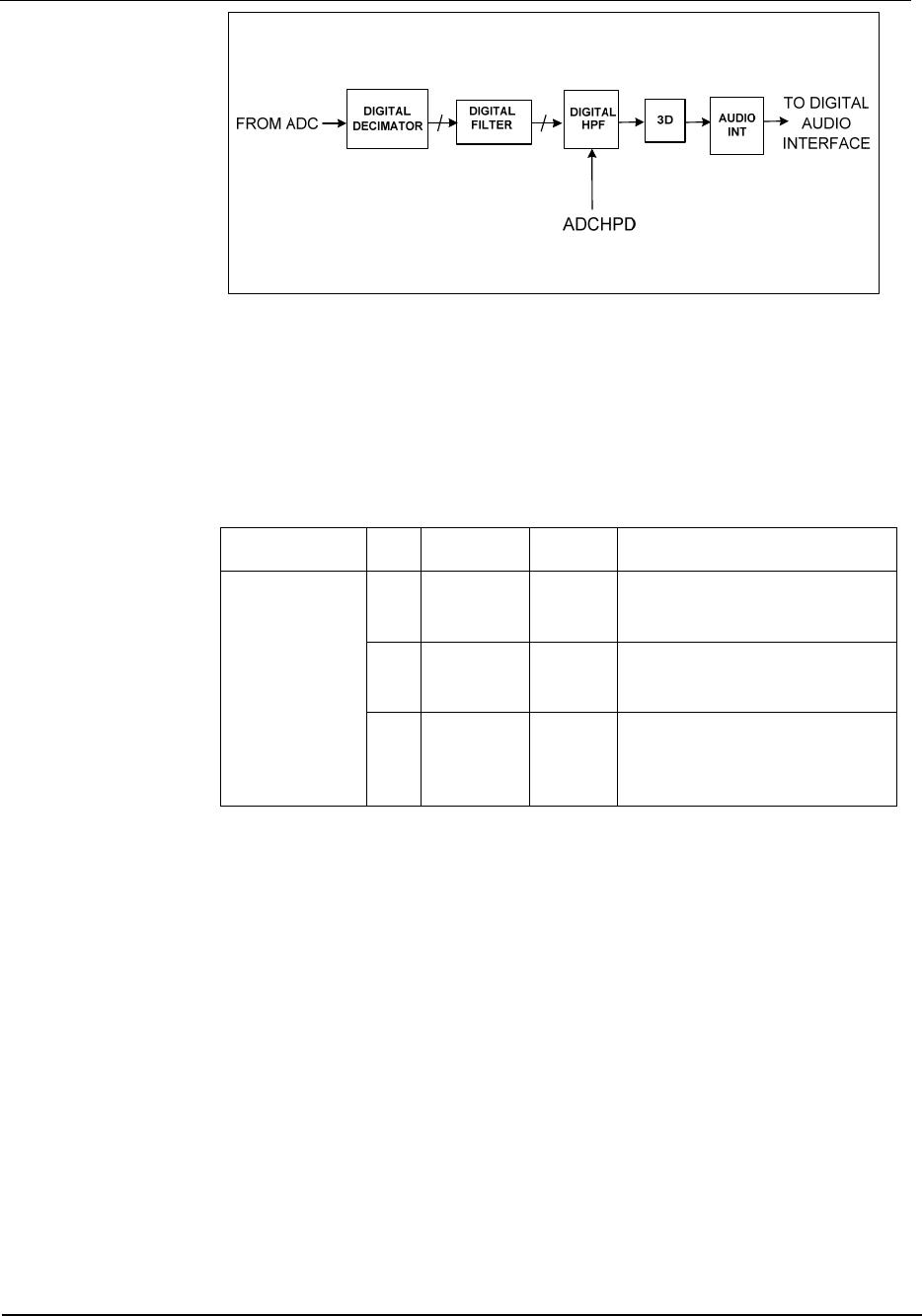

ADC DIGITAL FILTER

The ADC filters perform true 24 bit signal processing to convert the raw multi-bit oversampled data

from the ADC to the correct sampling frequency to be output on the digital audio interface. The digital

filter path is illustrated below.