WM8737L Production Data

w

PD, Rev 4.4, January 2012

16

MICROPHONE PREAMPLIFER BYPASS AND BIAS CONTROL

When the Left or Right microphone preamplifier is disabled the user has two options for driving the

corresponding Left or Right PGA.

Default operation is to close a preamplifier bypass switch that connects the PGA input directly to the

L/RINPUT1/2/3 multiplexer output.

If the application has only a single left or right line level signal source and hence does not require the

multiplexer or microphone preamplifier, then better PGA gain accuracy and THD+N performance are

obtained by disabling the multiplexer and bypass switch and driving the PGA directly via the L/RACIN

pin. The multiplexer and switch are disabled by setting to zero the appropriate L/RBYPEN bit in

register R9. The L/RINPUT1/2/3 pads remain biased to VREF. These bits should be set to 1 if the

multiplexer is required (always required when the microphone preamplifier is enabled).

The user can also adjust the microphone preamplifier bias settings to optimise THD+N versus supply

current consumption for their application. Default is full bias for best THD+N performance, but the

user can reduce the bias to 75%, 50% or 25% of default by programming MBCTRL[1:0] in register R9.

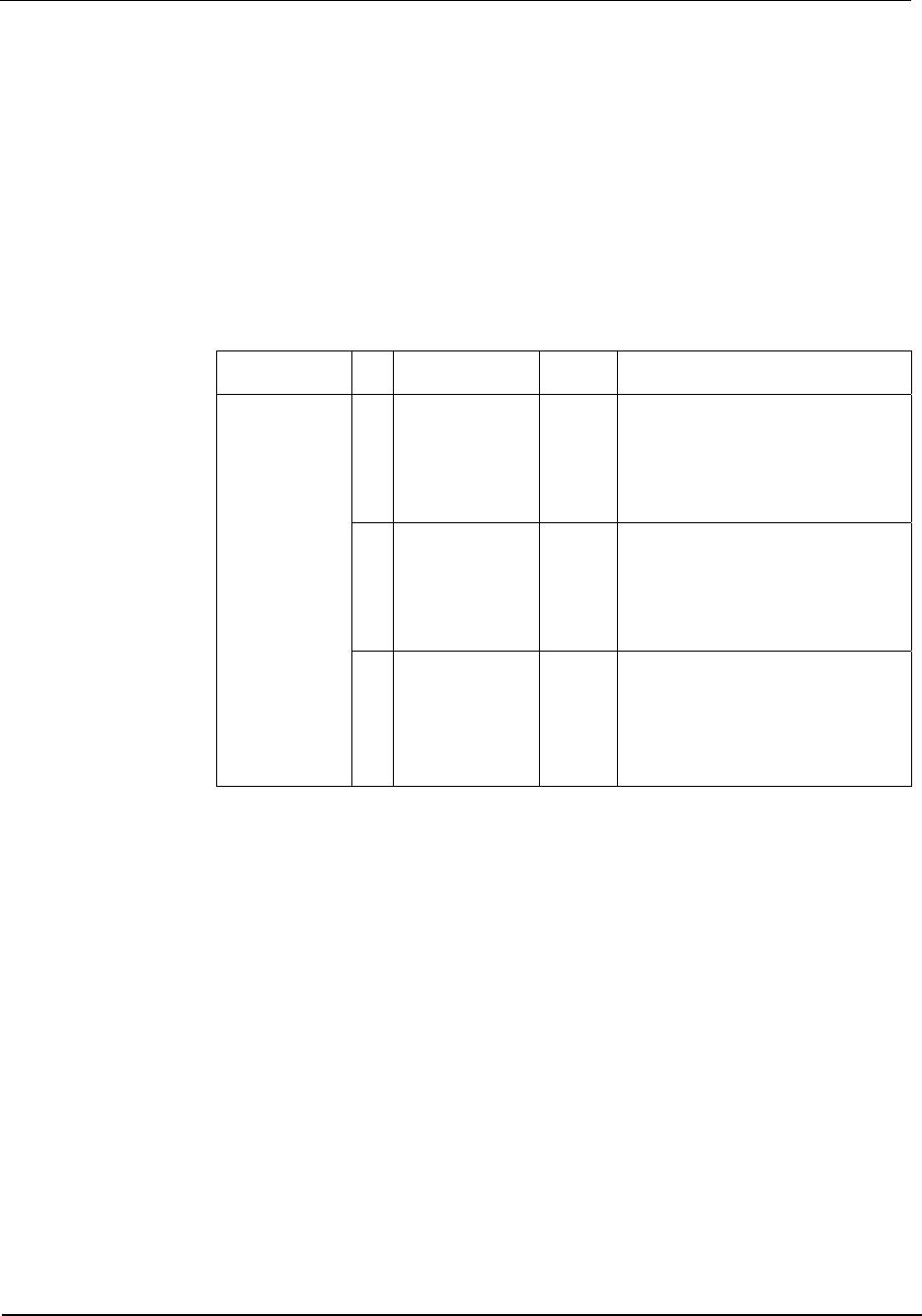

REGISTER

ADDRESS

BIT LABEL DEFAULT DESCRIPTION

R9 (09h)

Microphone

Preamplifiers

Control

3

RBYPEN 1 Right channel bypass enable

0: Bypass switch is always open.

RINPUT1/2/3 high-impedance biased to

AVDD/2. RPGA input is RACIN pin.

1: Close bypass switch when right mic

preamp is disabled.

2

LBYPEN 1 Left channel bypass enable

0: Bypass switch is always open.

LINPUT1/2/3 high-impedance biased to

AVDD/2. LPGA input is LACIN pin.

1: Close bypass switch when left mic

preamp is disabled.

1:0

MBCTRL[1:0] 11 Bias control for left and right

microphone preamplifiers

00: bias 25%

01: bias 50%

10: bias 75%

11: nominal (100%) bias

Table 4 Microphone Preamplifier Control

MONO-MIXING

The WM8737L can operate as a stereo or mono device, or the two channels can be mixed to mono in

either the analogue domain (before the ADC) or in the digital domain (after the ADC). In all mono and

mono-mix modes unused circuitry can be switched off to save power (see “Power Management”

section). 3D stereo enhancement (See “3D Stereo Enhancement” section) is automatically disabled in

all mono and mono-mix modes.

In analogue mono-mix mode, the signals are mixed in the Left ADC and the Right ADC automatically

switches to dc measurement mode on pin RINPUT1. If dc measurement mode is not required then

the Right ADC can be powered down by setting bit 2 (ADCR) in the power management register R6.

Note that the high pass filter must be disabled if d.c. measurements are required.

In stereo and mono modes the Left/Right ADC data appear at the corresponding Left/Right Channel

outputs. In digital mono-mix mode the mixed data appears on both the Left and Right Channel

outputs. In analogue mono-mix mode the MONOUT bit controls whether the Right channel output

presents the data from the Right ADC (dc measurement) or a copy of the Left Channel (mixed)

output.