WM8737L Production Data

w

PD, Rev 4.4, January 2012

22

The ALC function is enabled using the ALCSEL[1:0] control bits in register R12. When enabled, the

recording volume can be programmed between -3dB and -18dB (relative to ADC full scale) using the

ALCL[3:0] register bits in register R12.

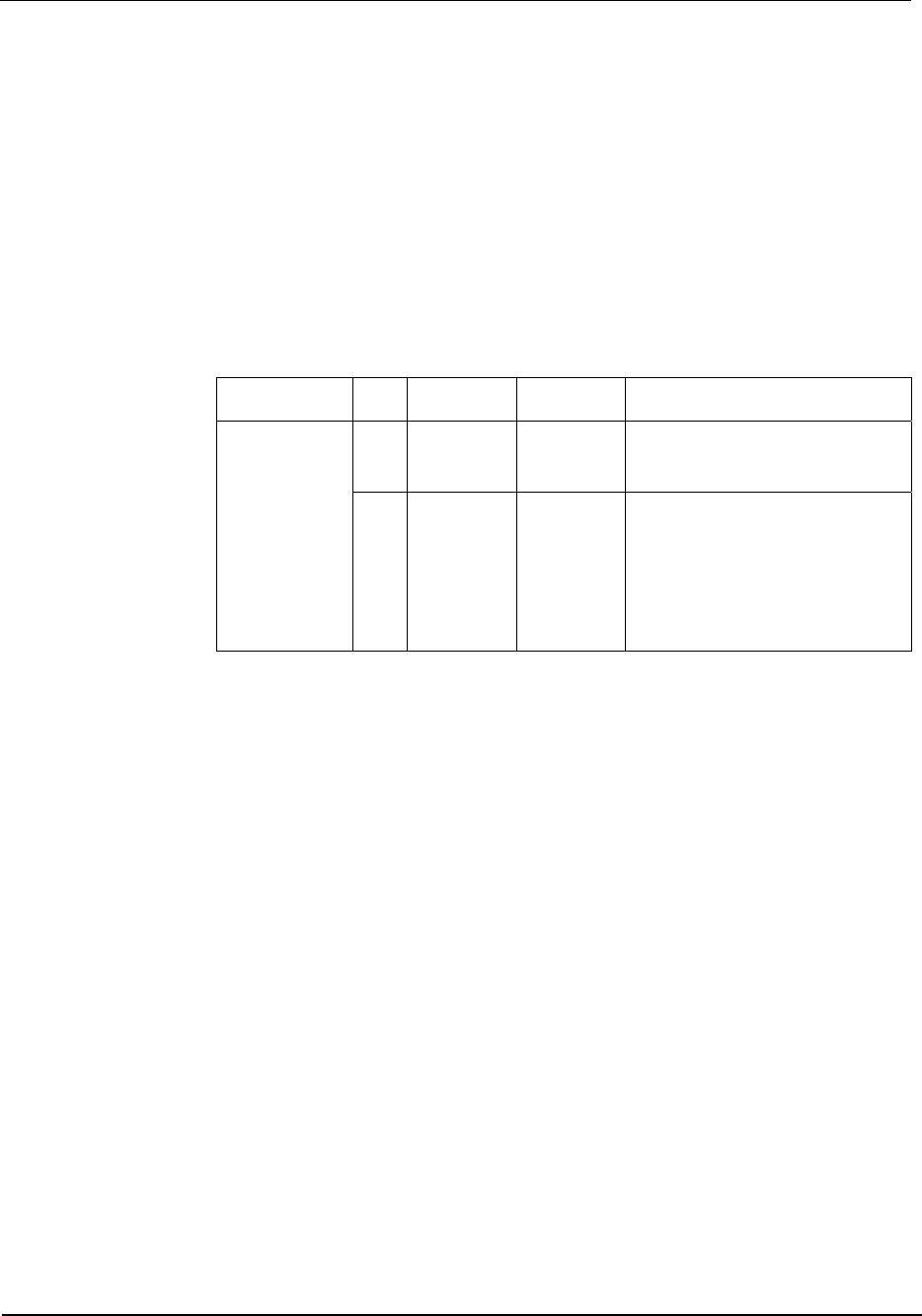

R13 and R14 bits HLD[3:0], DCY[3:0] and ATK[3:0] control the hold, decay and attack times,

respectively:

Hold time is the time delay between the peak level detected being below target and the PGA gain

beginning to ramp up. It can be programmed in power-of-two (2

n

) steps, e.g. 2.67ms, 5.33ms,

10.67ms etc. up to 43.7ms. Alternatively, the hold time can also be set to zero. The hold time only

applies to gain ramp-up, there is no delay before ramping the gain down when the signal level is

above target.

Decay time (Gain Ramp-Up) is the time that it takes for the PGA gain to ramp up across 90% of its

range (e.g. from –15dB up to 25.5 dB). The time it takes for the recording level to return to its target

value therefore depends on both the decay time and on the gain adjustment required. If the gain

adjustment is small, it will be shorter than the decay time. The decay time can be programmed in

power-of-two (2

n

) steps, from 33.6ms, 67.2ms, 134.4ms etc. to 34.41s.

Attack time (Gain Ramp-Down) is the time that it takes for the PGA gain to ramp down across 90% of

its range (e.g. from 25.5dB down to -15dB gain). The time it takes for the recording level to return to

its target value therefore depends on both the attack time and on the gain adjustment required. If the

gain adjustment is small, it will be shorter than the attack time. The attack time can be programmed in

power-of-two (2

n

) steps, from 8.4ms, 16.8ms, 33.6ms etc. to 8.6s.

When operating in stereo, the peak detector takes the maximum of left and right channel peak values,

and any new gain setting is applied to both left and right PGAs, so that the stereo image is preserved.

However, the ALC function can also be enabled on one channel only. In this case, only one PGA is

controlled by the ALC mechanism, while the other channel runs independently with its PGA gain set

through the control register.

When one ADC channel is unused or used for dc measurement, the peak detector disregards that

channel. The ALC function can operate in digital mono mix mode (MONOMIX = 10), but not in

analogue mono mix mode (MONOMIX = 01).