LTC6803-2/LTC6803-4

28

680324fa

APPLICATIONS INFORMATION

DIFFERENCE BETWEEN THE LTC6803-2 AND LTC6803-4

The only difference between the LTC6803-2 and the

LTC6803-4 is the bonding of the V

–

and C0 pins. The

V

–

and C0 are separate signals on every LTC6803 die.

In the LTC6803-2 package, the V

–

and C0 signals are

shorted together by bonding these signals to the same

pin. In the LTC6803-4 package, V

–

and C0 are separate

pins. Therefore, the LTC6803-2 is pin compatible with the

LTC6802-2. For new designs the LTC6803-4 pinout allows

a Kelvin connection to C0 (Figure 22).

CELL VOLTAGE FILTERING

The LTC6803 employs a sampling system to perform its

analog-to-digital conversions and provides a conversion

result that is essentially an average over the 0.5ms con-

version window, provided there isn’t noise aliasing with

respect to the delta-sigma modulator rate of 512kHz. This

indicates that a lowpass filter with 30dB attenuation at

500kHz may be beneficial. Since the delta-sigma integra-

tion bandwidth is about 1kHz, the filter corner need not

be lower than this to assure accurate conversions.

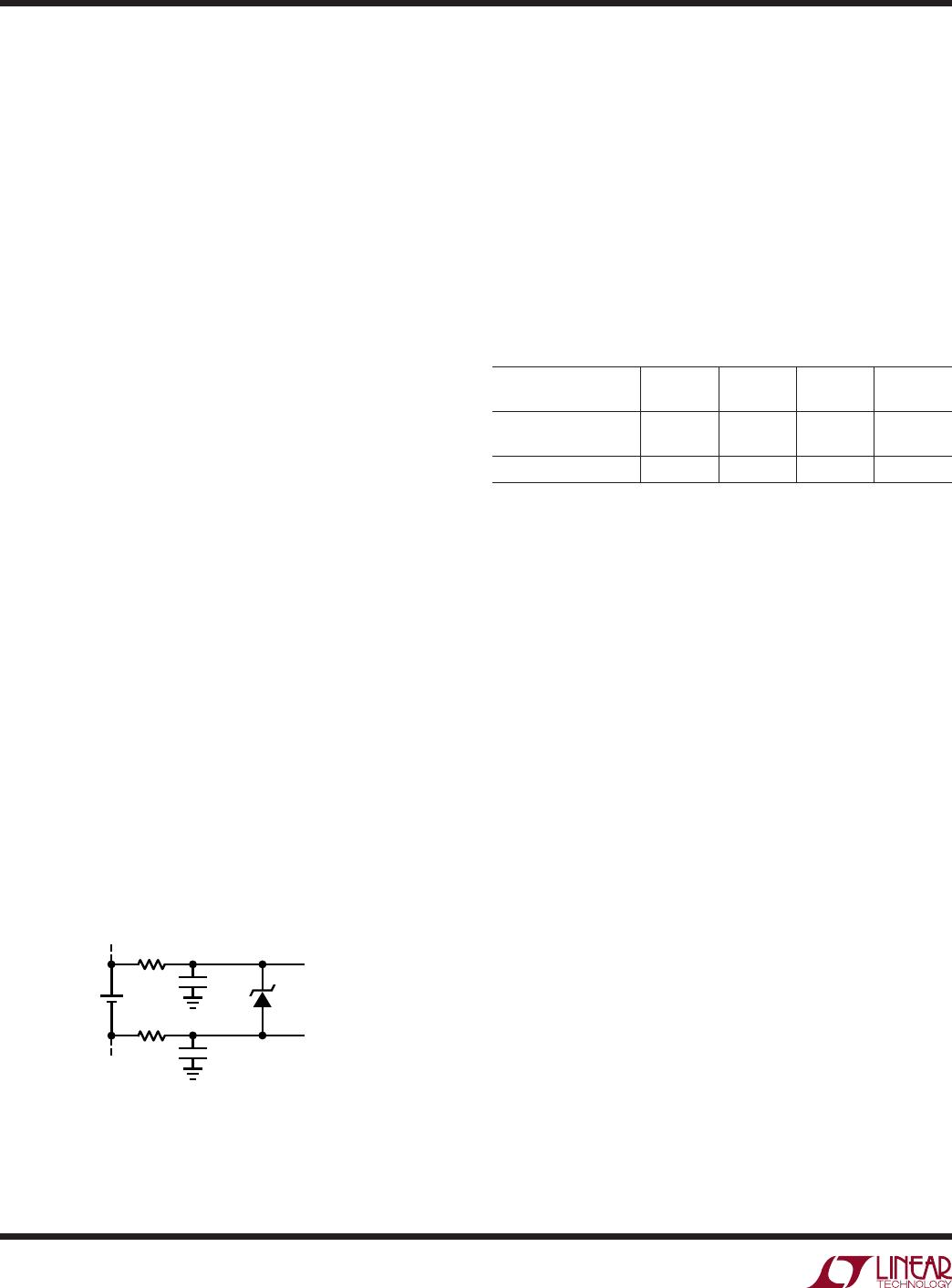

Series resistors of 100Ω may be inserted in the input

paths without introducing meaningful measurement er-

ror. Shunt capacitors may be added from the cell inputs

to V

–

, creating RC filtering as shown in Figure 8. The cell

balancing MOSFET in Figure 11 can cause a small transient

when it switches on and off. Keeping the cutoff frequency

of the RC filter relatively high will allow adequate settling

prior to the actual conversion. A delay of about 500µs is

provided in the ADC timing, so a 16kHz LPF is optimal

(100Ω, 0.1µF) and offers about 30dB of noise rejection.

Larger series resistors and shunt capacitors can be used

to lower the filter bandwidth. The measurement error due

to the larger component values is a complex function of

the component values. The error also depends on how

often measurements are made. Table 17 is an example. In

each example a 3.6V cell is being measured and the error

is displayed in millivolts. There is a RC filter in series with

inputs C1 through C12. There is no filter in series with

C0. There is an interaction between cells. This is why the

errors for C1 and C12 differ from C2 through C11.

Table 17. Cell Measurement Errors vs Input RC Values

R = 100Ω,

C = 0.1µF

R = 1k,

C = 0.1µF

R = 1k,

C = 1µF

R = 10k,

C = 3.3µF

Cell 1 Error

(mV, LTC6803-2)

0.1 4.5 1.5 1.5

Cell 2 to Cell 12 (mV) 1 9 3 0.5

For the LTC6803-2, no resistor should be placed in series

with the V

–

pin. Because the supply current flows from

the V

–

pin, any resistance on this pin could generate a

significant conversion error for cell 1, and the error of

cell 1 caused by the RC filter differs from errors of cell 2

to cell 2.

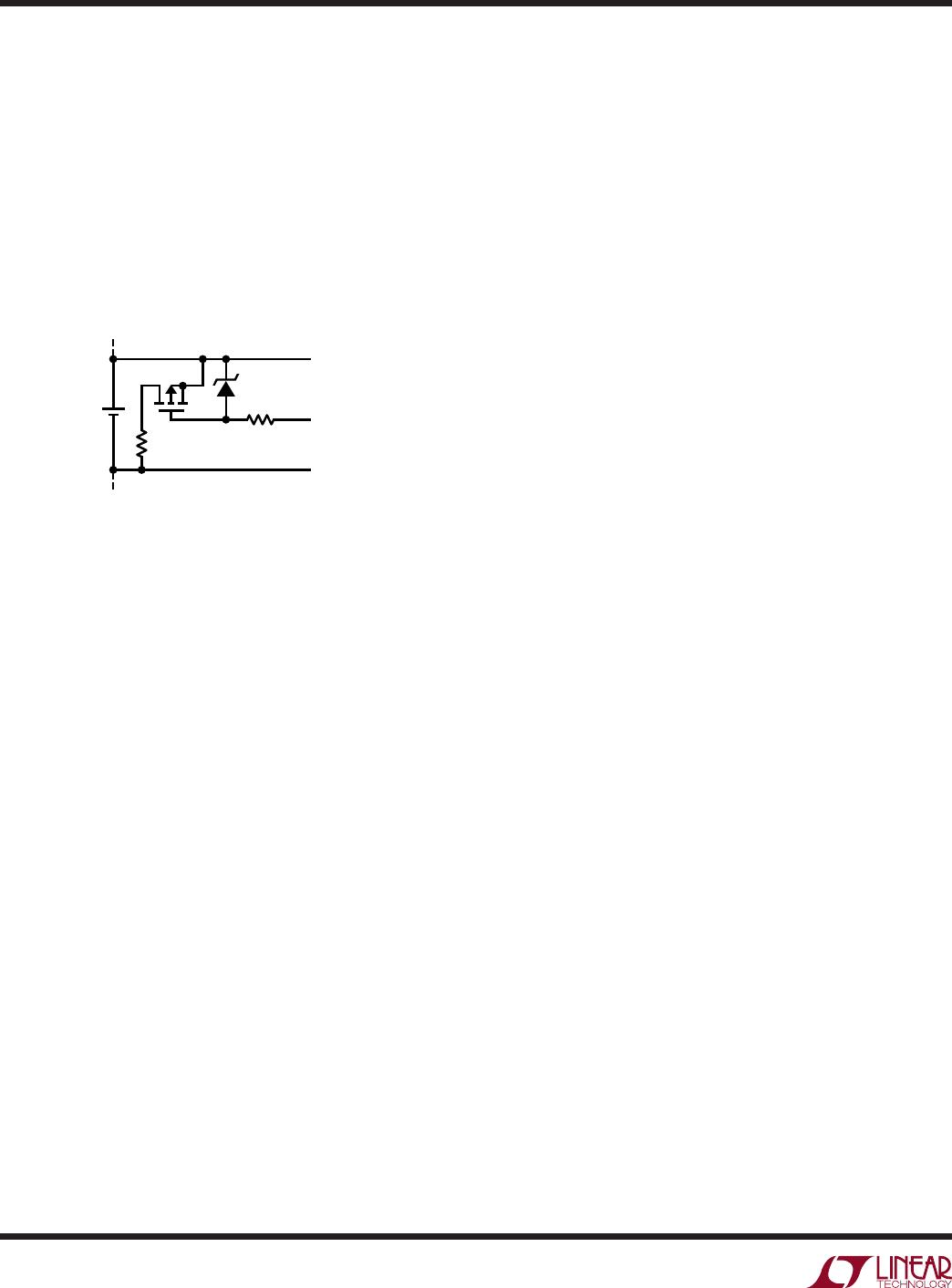

OPEN-CONNECTION DETECTION

When a cell input (C pin) is open, it affects two cell mea-

surements. Figure 9 shows an open connection to C3,

in an application without external filtering between the C

pins and the cells. During normal ADC conversions (that

is, using the STCVAD command), the LTC6803 will give

near zero readings for B3 and B4 when C3 is open. The

zero reading for B3 occurs because during the measure-

ment of B3, the ADC input resistance will pull C3 to the

C2 potential. Similarly, during the measurement of B4, the

ADC input resistance pulls C3 to the C4 potential.

Figure 10 shows an open connection at the same point in

the cell stack as Figure 9, but this time there is an external

filtering network still connected to C3. Depending on the

value of the capacitor remaining on C3, a normal measure-

ment of B3 and B4 may not give near-zero readings, since

the C3 pin is not truly open. In fact, with a large external

capacitance on C3, the C3 voltage will be charged midway

Figure 8. Adding RC Filtering to the Cell Inputs

(One Cell Connection Shown)

+

100nF

100nF

680324 F08

7.5V

Cn

C(n – 1)

100Ω

100Ω