MT9V024/D

www.onsemi.com

22

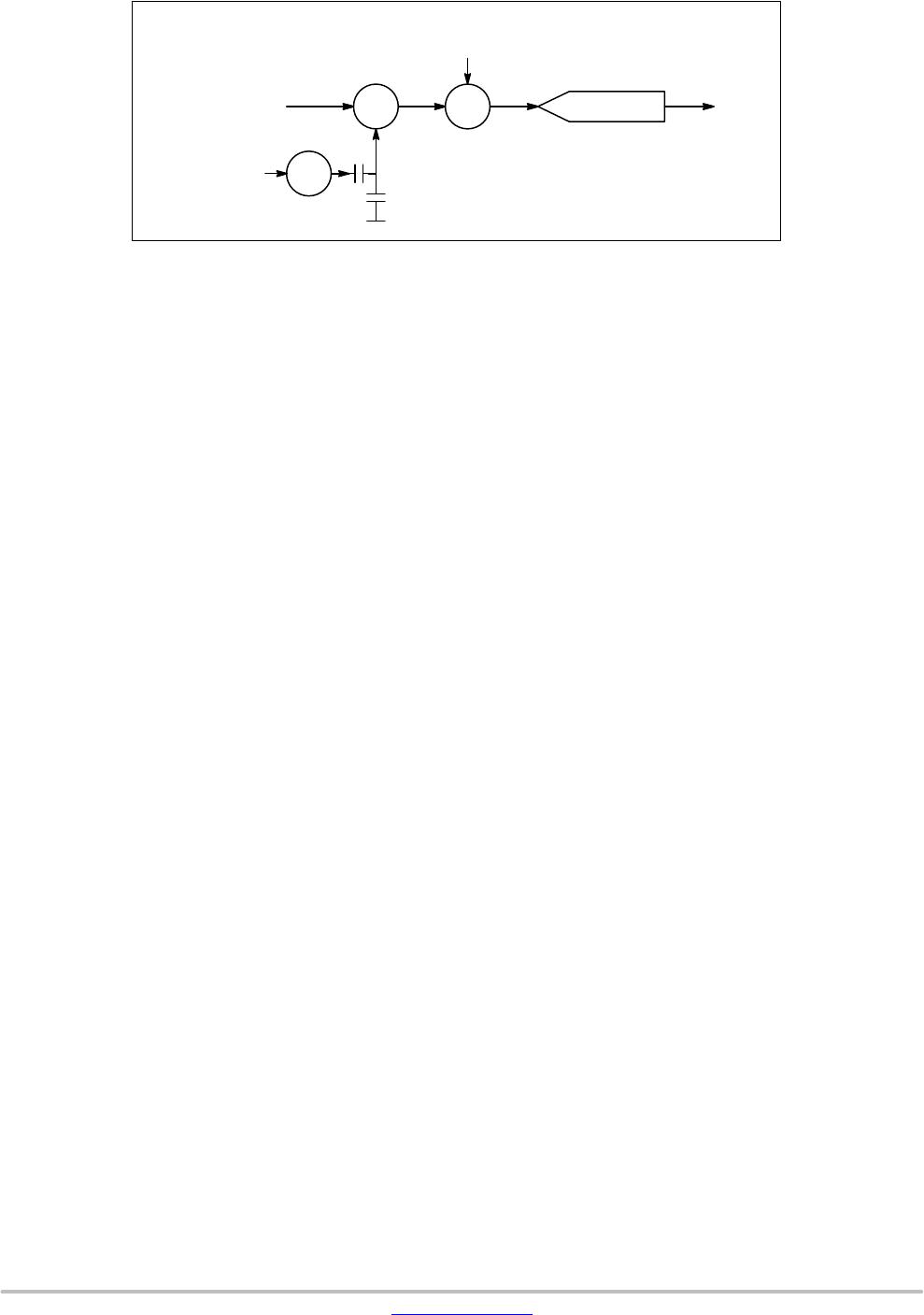

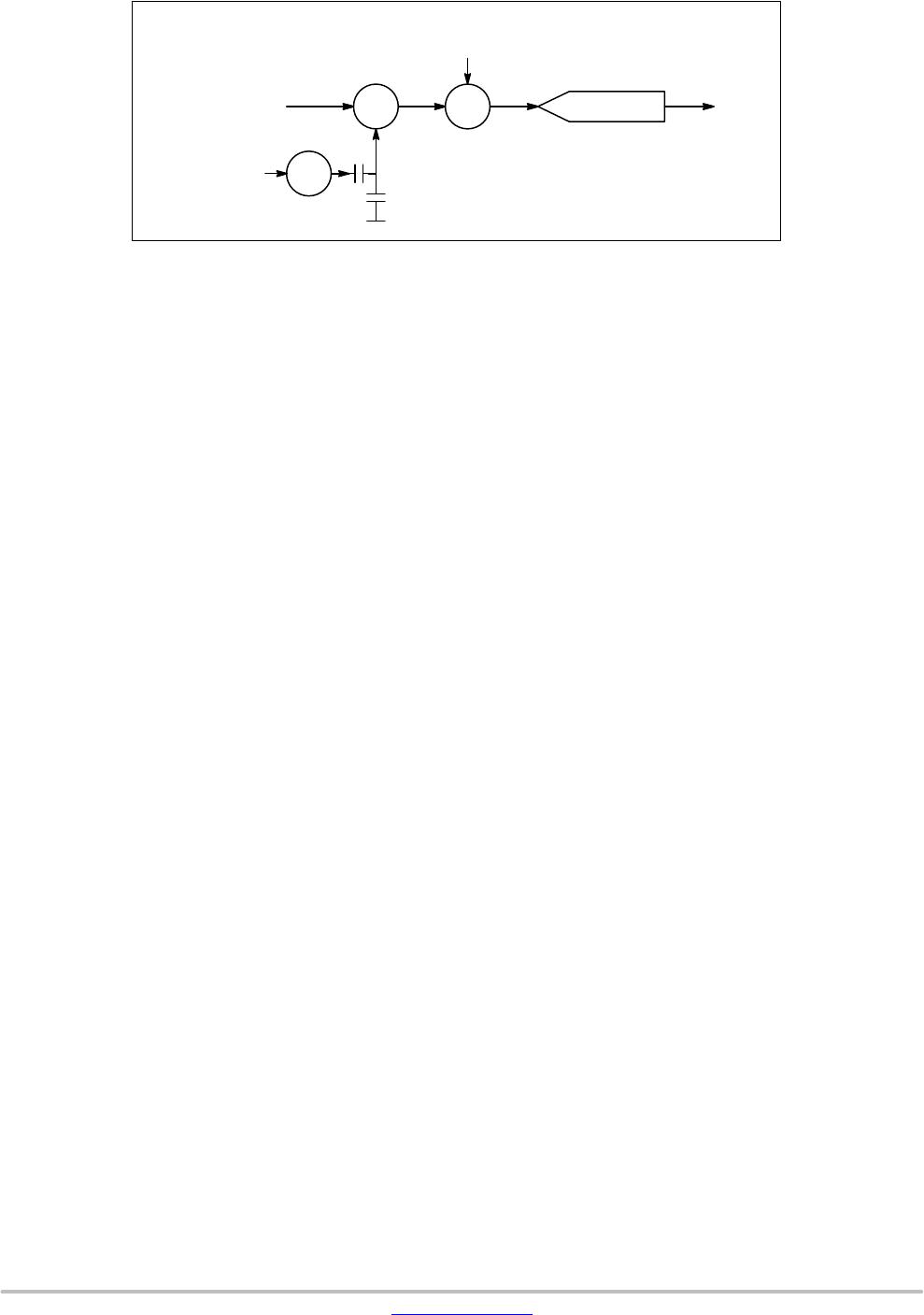

Figure 28. Black Level Calibration Flow Chart

Pixel Output

(reset minus signal)

Offset Correction

Voltage (R0x48 or

result of BLC)

Gain Selection

(R0x35 or R0x36 or

result of AGC)

ADC Data

(9:0)

10 (12) bit ADC

C1

C2

+

Σ

×

V

REF

(R0x2C)

The automatic black level calibration measures the

average value of pixels from 2 dark rows (1 dark row if row

bin 4 is enabled) of the chip. (The pixels are averaged as if

they were light−sensitive and passed through the appropriate

gain.)

This row average is then digitally low−pass filtered over

many frames (R0x47, bits 7:5) to remove temporal noise and

random instabilities associated with this measurement.

Then, the new filtered average is compared to a minimum

acceptable level, low threshold, and a maximum acceptable

level, high threshold.

If the average is lower than the minimum acceptable level,

the offset correction voltage is increased by a programmable

offset LSB in R0x4C. (Default step size is 2 LSB Offset =

1 ADC LSB at analog gain = 1X.)

If it is above the maximum level, the offset correction

voltage is decreased by 2 LSB (default).

To avoid oscillation of the black level from below to

above, the region the thresholds should be programmed so

the difference is at least two times the offset DAC step size.

In normal operation, the black level calibration

value/offset correction value is calculated at the beginning

of each frame and can be read through the two−wire serial

inter−face from R0x48. This register is an 8−bit signed two’s

complement value.

However, if R0x47, bit 0 is set to “1,” the calibration value

in R0x48 is used rather than the automatic black level

calculation result. This feature can be used in conjunction

with the “show dark rows” feature (R0x0D[6]) if using an

external black level calibration circuit.

The offset correction voltage is generated according to the

following formulas:

OffsetCorrectionVoltage + (8 * bit signed twoȀs complement calibration value, 127 0.25mV

(eq. 18)

ADC input voltage + (Pixel Output Voltage) * Analog Gain ) Offset Correction Voltage (AnalogGain ) 1)

(eq. 19)

Defective Pixel Correction

Defective pixel correction is intended to compensate for

defective pixels by replacing their value with a value based

on the surrounding pixels, making the defect less notice−

able to the human eye. The locations of defective pixels are

stored in a ROM on chip during the manufacturing process;

the maximum number of defects stored is 32. There is no

provision for later augmenting the table of programmed

defects. In the defect correction block, bad pixels will be

substituted by either the average of its neighboring pixels, or

its nearest−neighbor pixel, depending on pixel location.

Defective Pixel Correction is enabled by R0x07[9]. By

default, correction is enabled, and pixels mapped in internal

ROM are replaced with corrected values. This might be

unacceptable to some applications, in which case pixel

correction should be disabled (R0x07[9] = 0).

For complete details on using Defective Pixel Correction,

refer to AND9554/D, “Defective Pixel Correction −

Description and Usage”.

Row−wise Noise Correction

Row−wise noise correction is controlled by the following

registers:

• R0x70 Row Noise Control

• R0x72 Row Noise Constant

Row−wise noise cancellation is performed by calculating

a row average from a set of optically black pixels at the start

of each row and then applying each average to all the active

pixels of the row. Read Dark Columns register bit and Row

Noise Correction Enable register bit must both be set to

enable row−wise noise cancellation to be performed. The

behavior when Read Dark Columns register bit = 0 and Row

Noise Correction Enable register bit = 1 is undefined.

The algorithm works as follows:

Logical columns 755−790 in the pixel array provide 36

optically black pixel values. Of the 36 values, two smallest

value and two largest values are discarded. The remaining

32 values are averaged by summing them and discarding the