MT9V024/D

www.onsemi.com

28

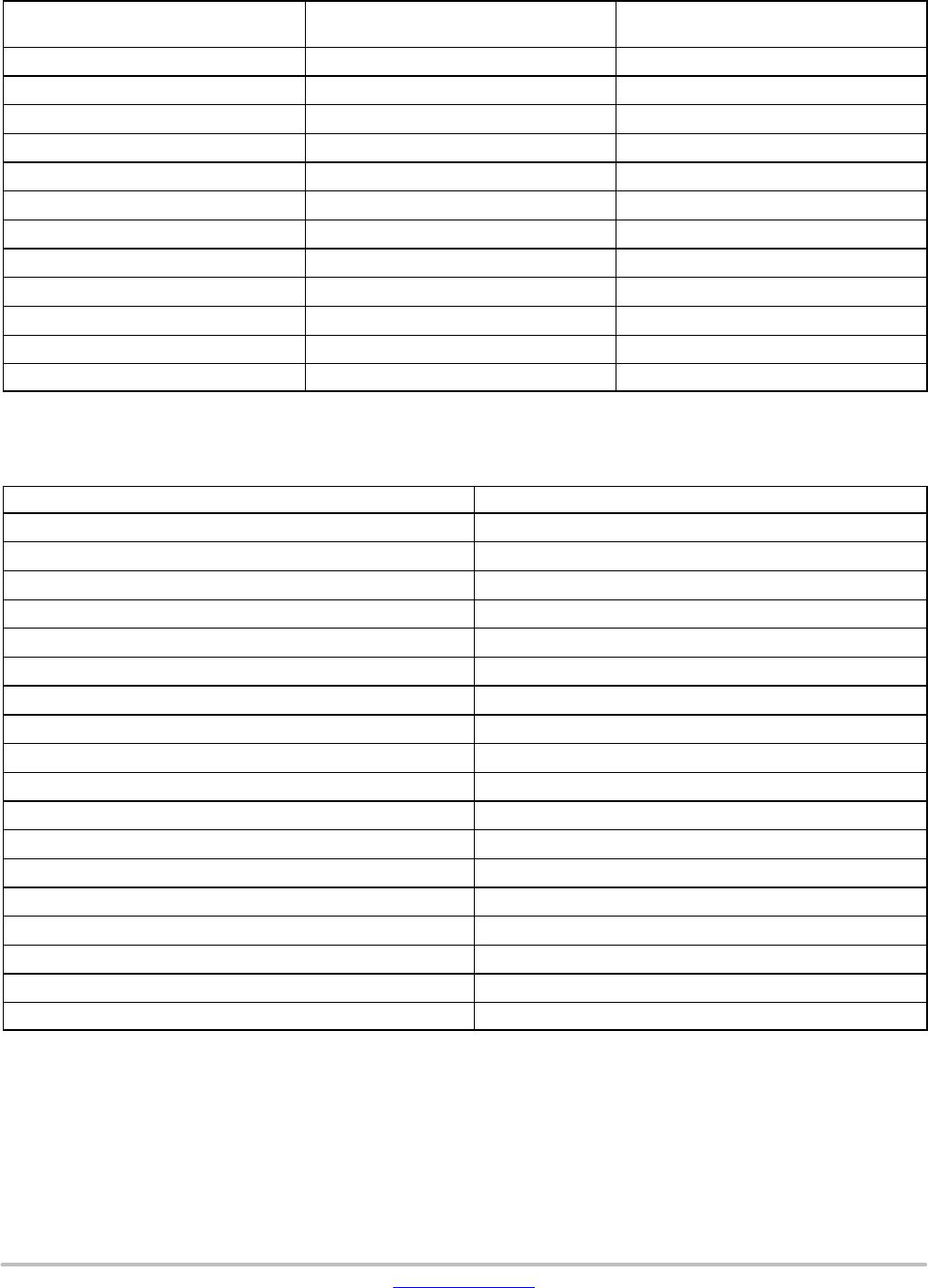

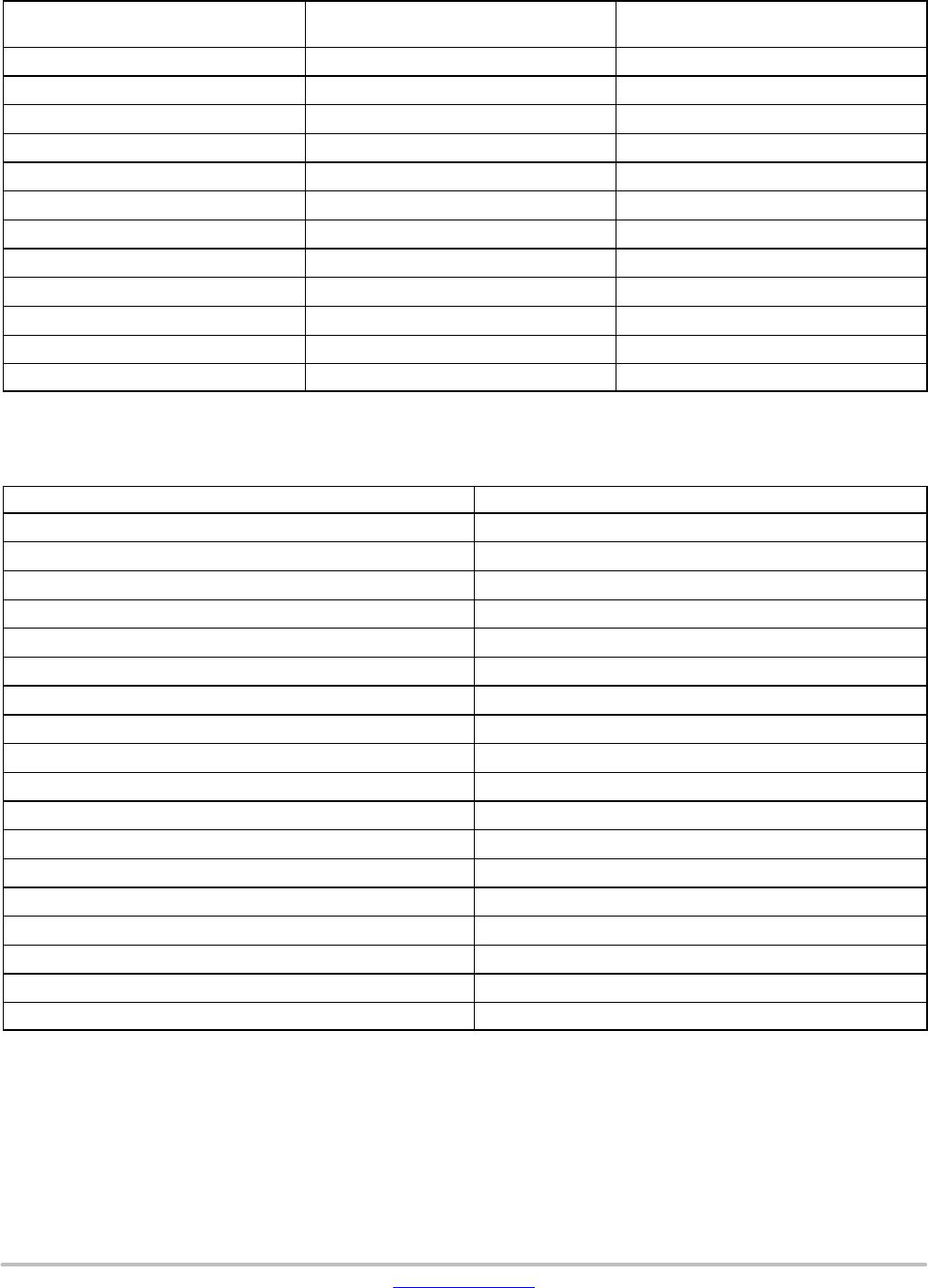

Table 10. LVDS PACKET FORMAT IN STAND−ALONE MODE (Stereoscopy Mode Bit De−Asserted)

12 Bit Packet

Use_10−bit_pixels Bit De−Asserted

(8−Bit Mode)

Use_10−bit_pixels Bit Asserted

(10−Bit Mode)

Bit [0] 1’b1(Start bit) 1’b1(Start bit)

Bit [1] Pixel Data [2] Pixel Data [0]

Bit [2] Pixel Data [3] Pixel Data [1]

Bit [3] Pixel Data [4] Pixel Data [2]

Bit [4] Pixel Data [5] Pixel Data [3]

Bit [5] Pixel Data [6] Pixel Data [4]

Bit [6] Pixel Data [7] Pixel Data [5]

Bit [7] Pixel Data [8] Pixel Data [6]

Bit [8] Pixel Data [9] Pixel Data [7]

Bit [9] Line_Valid Pixel Data [8]

Bit [10] Frame_Valid Pixel Data [9]

Bit [11] 1’b0(Stop bit) 1’b0(Stop bit)

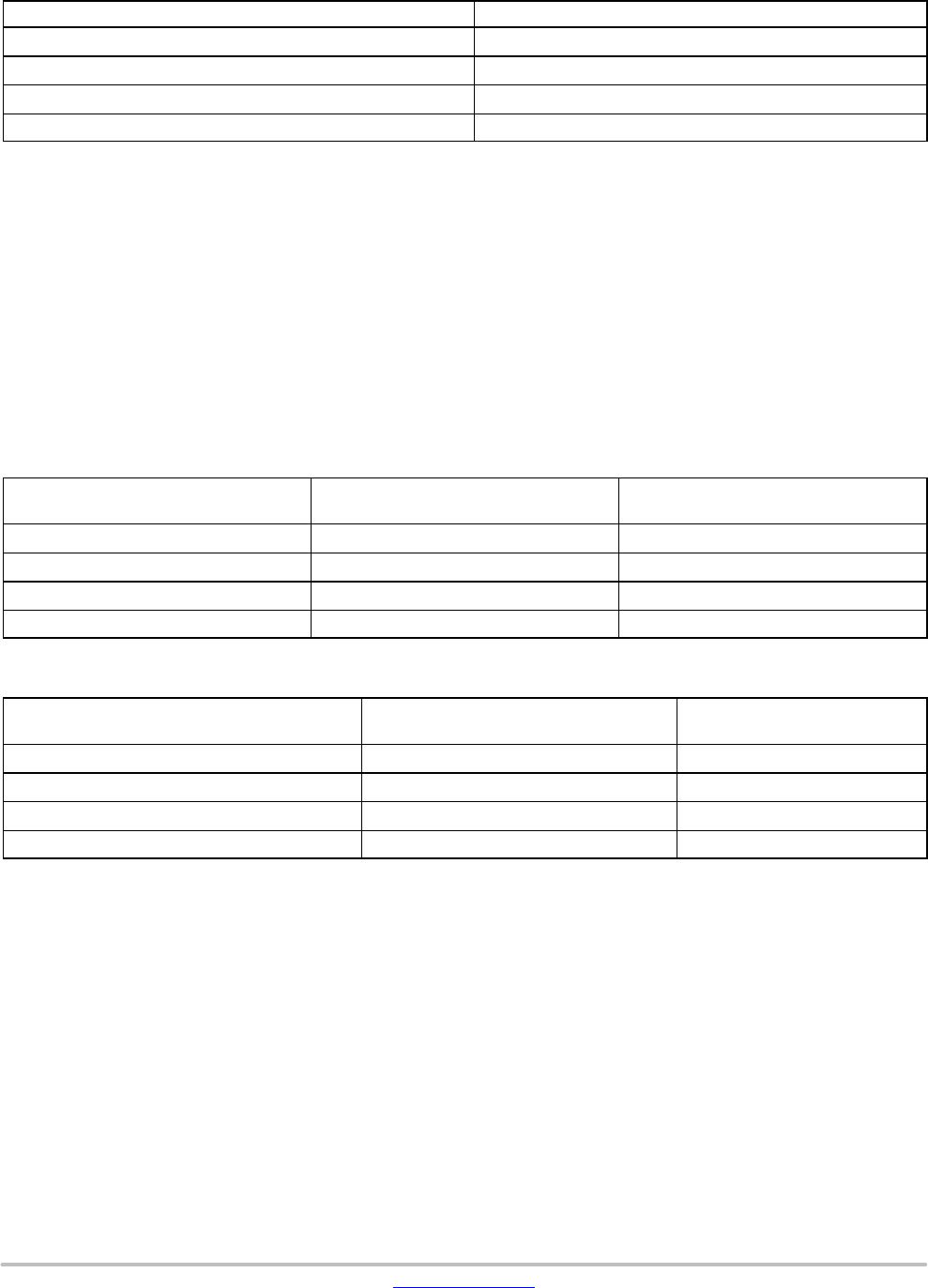

5. In stereoscopic mode, the packet size is 18 bits (2 frame bits and 16 payload bits). The packet consists of a start bit, the master pixel byte

(with sync codes), the slave byte (with sync codes), and the stop bit.)

Table 11. LVDS PACKET FORMAT IN STEREOSCOPY MODE (Stereoscopy Mode Bit Asserted)

18−bit Packet

Function

Bit [0] 1’b1 (Start bit)

Bit [1] Master Sensor Pixel Data [2]

Bit [2] Master Sensor Pixel Data [3]

Bit [3] Master Sensor Pixel Data [4]

Bit [4] Master Sensor Pixel Data [5]

Bit [5] Master Sensor Pixel Data [6]

Bit [6] Master Sensor Pixel Data [7]

Bit [7] Master Sensor Pixel Data [8]

Bit [8] Master Sensor Pixel Data [9]

Bit [9] Slave Sensor Pixel Data [2]

Bit [10] Slave Sensor Pixel Data [3]

Bit [11] Slave Sensor Pixel Data [4]

Bit [12] Slave Sensor Pixel Data [5]

Bit [13] Slave Sensor Pixel Data [6]

Bit [14] Slave Sensor Pixel Data [7]

Bit [15] Slave Sensor Pixel Data [8]

Bit [16] Slave Sensor Pixel Data [9]

Bit [17] 1’b0 (Stop bit)

Control signals LV and FV can be reconstructed from their

respective preceding and succeeding flags that are always

embedded within the pixel data in the form of reserved

words.