MT9V024/D

www.onsemi.com

9

For Simultaneous mode, if the exposure time registers

(coarse shutter width total plus Fine Shutter Width Total)

exceed the total readout time, then the vertical blanking time

is internally extended automatically to adjust for the

additional integration time required. This extended value is

not written back to the vertical blanking registers. The

vertical blank register can be used to adjust frame−to−frame

readout time. This register does not affect the exposure time

but it may extend the readout time.

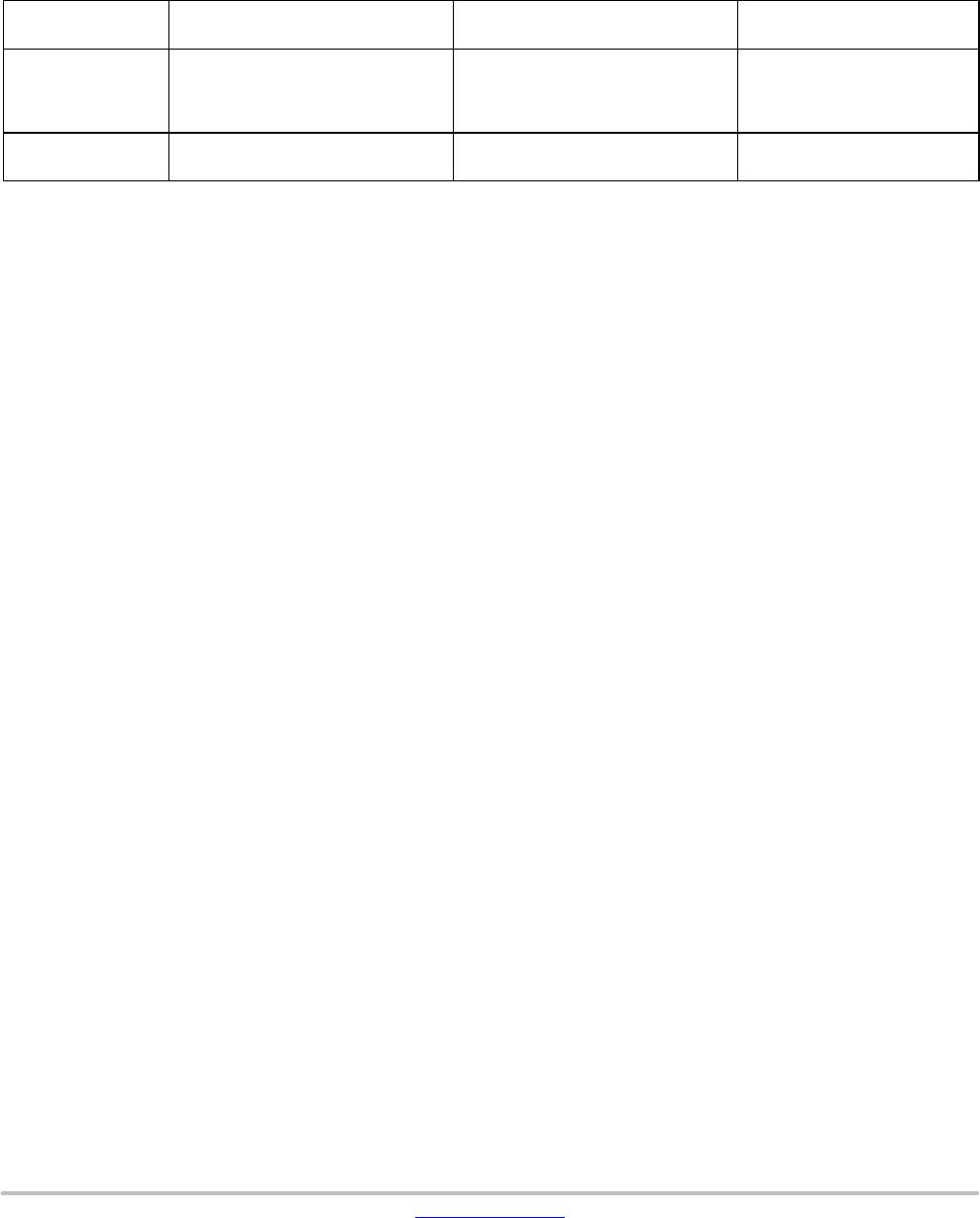

Table 5. FRAME TIME − LONG INTEGRATION TIME

Parameter Name

Equation

(Number of Master Clock Cycles)

Default Timing at 26.66 MHz

V’ Vertical blanking (long integration

time)

Context A: (R0x0B + 2 − R0x03) ×

(A + Q) + R0xD5 + 4

Context B: (R0xD2 + 2 − R0xCB) ×

(A + Q) + R0xD8 + 4

38,074 pixel clocks

= 38,074 master = 1.43ms

F” Total frame time (long integration

exposure time)

(R0x0B + 2) × (A + Q) + 4 444,154 pixel clocks

= 444,154 master = 16.66ms

4. The MT9V024 uses column parallel analog−digital converters; thus short row timing is not possible. The minimum total row time is 704

columns (horizontal width + horizontal blanking). The minimum horizontal blanking is 61 for normal mode, 71 for column bin 2 mode, and 91

for column bin 4 mode. When the window width is set below 643, horizontal blanking must be increased. In binning mode, the minimum row

time is R0x04+R0x05 = 704.

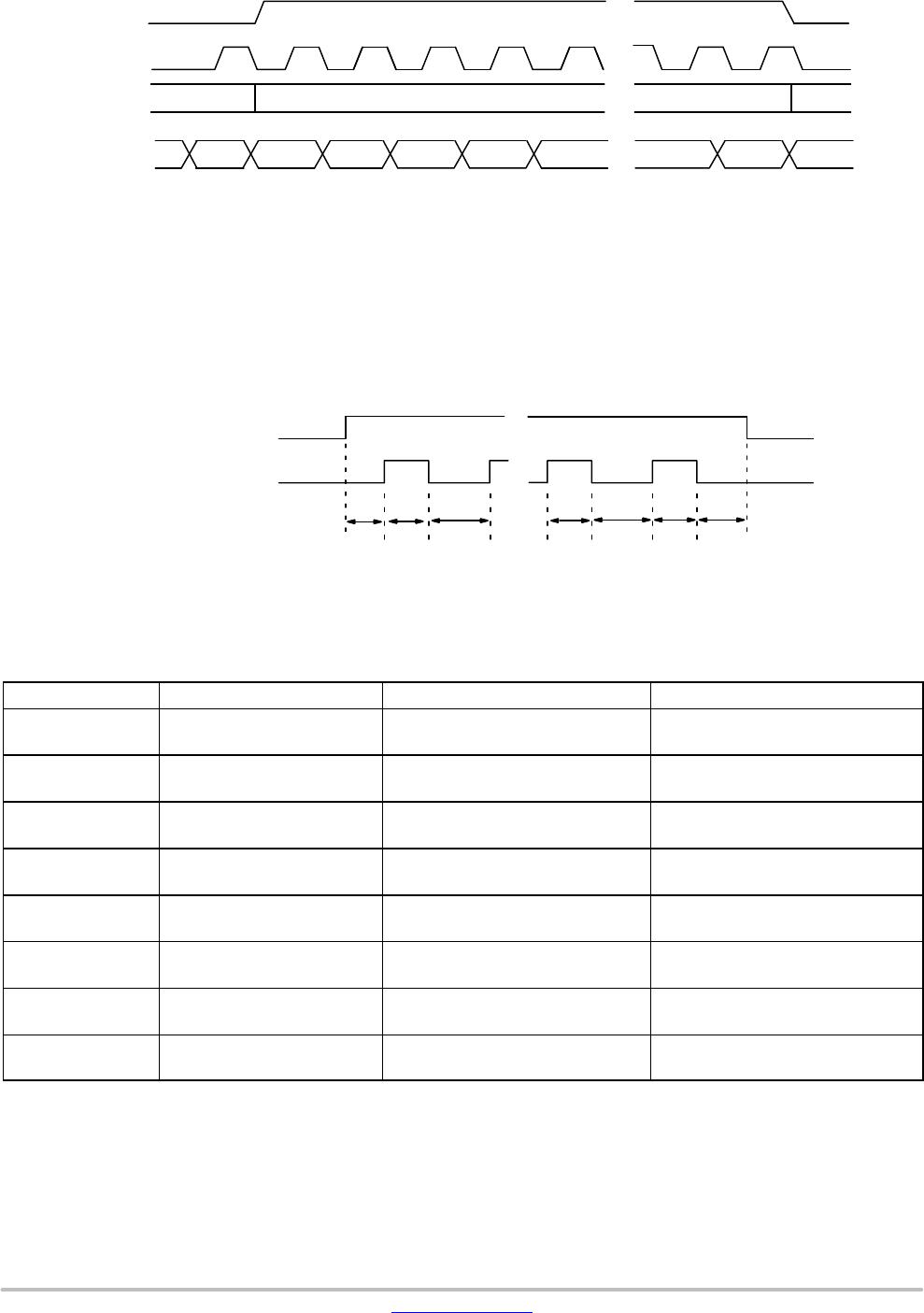

SERIAL BUS DESCRIPTION

Registers are written to and read from the MT9V024

through the two−wire serial inter−face bus. The MT9V024

is a serial interface slave with four possible IDs (0x90, 0x98,

0xB0 and 0xB8) determined by the S_CTRL_ADR0 and

S_CTRL_ADR1 input pins. Data is transferred into the

MT9V024 and out through the serial data (S

DATA) line. The

S

DATA line is pulled up to VDD off−chip by a 1.5 k resistor.

Either the slave or master device can pull the S

DATA line

down−the serial interface protocol determines which device

is allowed to pull the S

DATA line down at any given time. The

registers are 16−bit wide, and can be accessed through 16−or

8−bit two−wire serial interface sequences.

Protocol

1. a start bit

2. the slave device 8−bit address

3. a(n) (no) acknowledge bit

4. an 8−bit message

5. a stop bit

Start Bit

The start bit is defined as a HIGH−to−LOW transition of

the data line while the clock line is HIGH.

Slave Address

The 8−bit address of a two−wire serial interface device

consists of 7 bits of address and

1 bit of direction. A “0” in the LSB of the address indicates

write mode, and a “1” indicates read mode. As indicated

above, the MT9V024 allows four possible slave addresses

determined by the two input pins, S_CTRL_ADR0 and

S_CTRL_ADR1.

Acknowledge Bit

The master generates the acknowledge clock pulse. The

transmitter (which is the master when writing, or the slave

when reading) releases the data line, and the receiver

indicates an acknowledge bit by pulling the data line LOW

during the acknowledge clock pulse.

No−Acknowledge Bit

The no−acknowledge bit is generated when the data line

is not pulled down by the receiver during the acknowledge

clock pulse. A no−acknowledge bit is used to terminate

a read sequence.

Stop Bit

The stop bit is defined as a LOW−to−HIGH transition of

the data line while the clock line is HIGH.

Sequence

A typical READ or WRITE sequence begins by the

master sending a start bit. After the start bit, the master sends

the slave device’s 8−bit address. The last bit of the address

determines if the request is a read or a write, where a “0”

indicates a WRITE and a “1” indicates a READ. The slave

device acknowledges its address by sending an

acknowledge bit back to the master.

If the request was a WRITE, the master then transfers the

8−bit register address to which a WRITE should take place.

The slave sends an acknowledge bit to indicate that the

register address has been received. The master then transfers

the data 8 bits at a time, with the slave sending an

acknowledge bit after each 8 bits. The MT9V024 uses

16−bit data for its internal registers, thus requiring two 8−bit

transfers to write to one register. After 16 bits are transferred,

the register address is automatically incremented, so that the

next 16 bits are written to the next register address. The

master stops writing by sending a start or stop bit.

A typical READ sequence is executed as follows. First the

master sends the write mode slave address and 8−bit register

address, just as in the write request. The master then sends

a start bit and the read mode slave address. The master then