MT9V024/D

www.onsemi.com

27

LVDS Serial (Stand−Alone/Stereo) Output

The LVDS interface allows for the streaming of sensor

data serially to a standard off−the−shelf deserializer up to

eight meters away from the sensor. The pixels (and controls)

are packeted−12−bit packets for stand−alone mode and

18−bit packets for stereoscopy mode. All serial signaling

(CLK and data) is LVDS. The LVDS serial output could

either be data from a single sensor (stand−alone) or

stream−merged data from two sensors (self and its

stereoscopic slave pair). The appendices describe in detail

the topologies for both stand−alone and stereoscopic modes.

There are two standard deserializers that can be used. One

for a stand−alone sensor stream and the other from

a stereoscopic stream. The deserializer attached to a stand−

alone sensor is able to reproduce the standard parallel output

(8−bit pixel data, LV, FV, and PIXCLK). The deserializer

attached to a stereoscopic sensor is able to reproduce 8− bit

pixel data from each sensor (with embedded LV and FV )

and pixel−clk. An additional (simple) piece of logic is

required to extract LV and FV from the 8−bit pixel data.

Irrespective of the mode (stereoscopy/stand−alone), LV and

FV are always embedded in the pixel data.

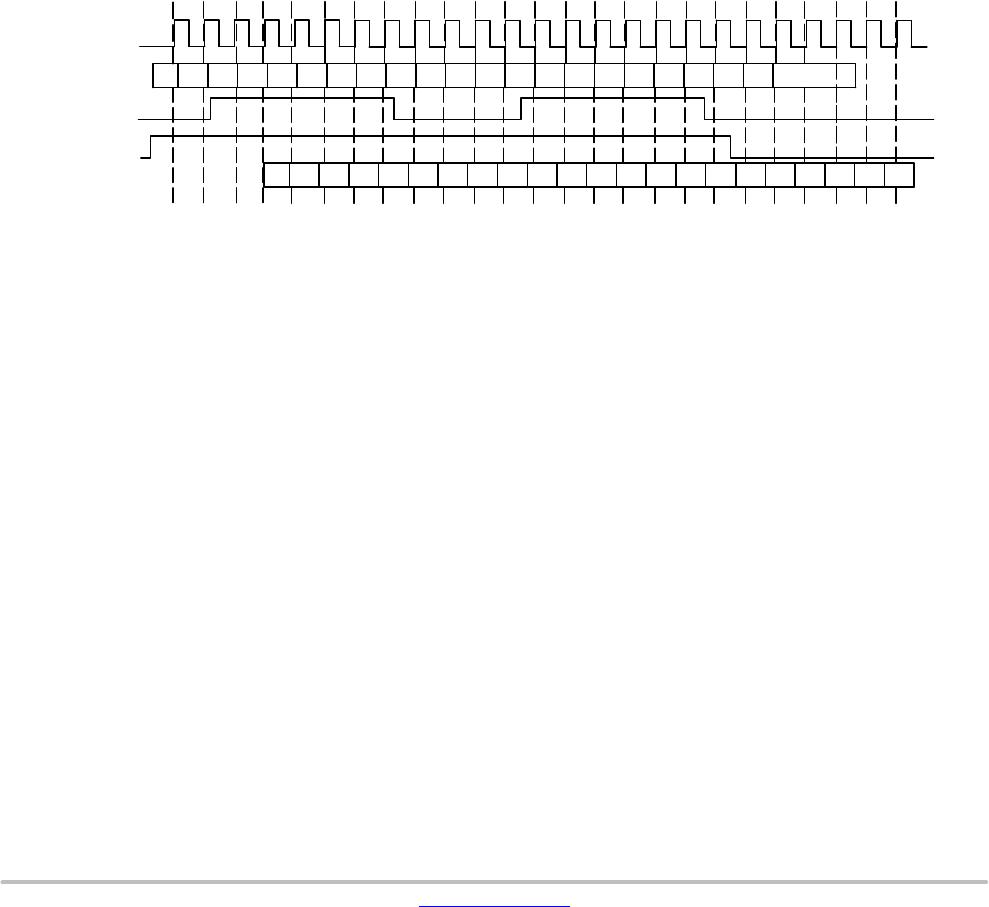

In stereoscopic mode, the two sensors run in lock−step,

implying all state machines are in the same state at any given

time. This is ensured by the sensor−pair getting their

sys−clks and sys−resets in the same instance. Configuration

writes through the two−wire serial interface are done in such

a way that both sensors can get their configuration updates

at once. The inter−sensor serial link is designed in such

a way that once the slave PLL locks and the data−dly,

shft−clk−dly and stream−latency−sel are configured, the

master sensor streams valid stereo content irrespective of

any variation voltage and/or temperature as long as it is

within specification. The configuration values of data−dly,

shft−clk

−dly and stream−latency−sel are either

predetermined from the board−layout or can be empirically

determined by reading back the stereo−error flag. This flag

is asserted when the two sensor streams are not in sync when

merged. The combo_reg is used for out−of−sync diagnosis.

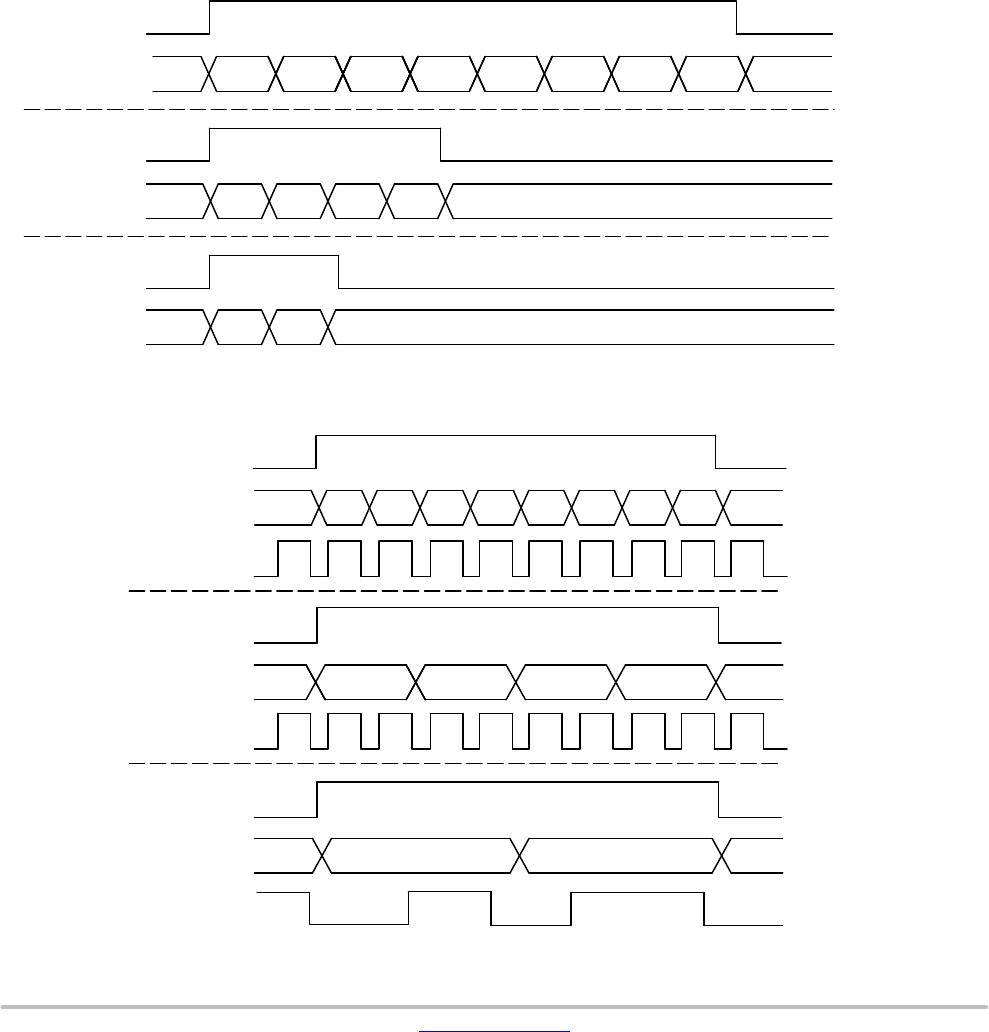

Figure 36. Serial Output Format for 6x2 Frame

Internal

PIXCLK

Internal

Parallel

Data

Internal

Line_Valid

Internal

Frame_Valid

External

Serial

Data Out

NOTES: 1. External pixel values of 0, 1, 2, 3, are reserved (they only convey control information).

Any raw pixel of value 0, 1, 2 and 3 will be substituted with 4.

2. The external pixel sequence 1023, 0 1023 is a reserved sequence (conveys control

information). Any raw pixel sequence of 1023, 0, 1023 will be substituted with 1023, 4, 1023.

P42P41 P43 P44 P45 P46 P52 P53 P54 P56

P55

P51

1023 0 1023 1 P41 P42 P43 P44 P45 P46 2 1 P51 P52 P53 P54 P55 P56 3

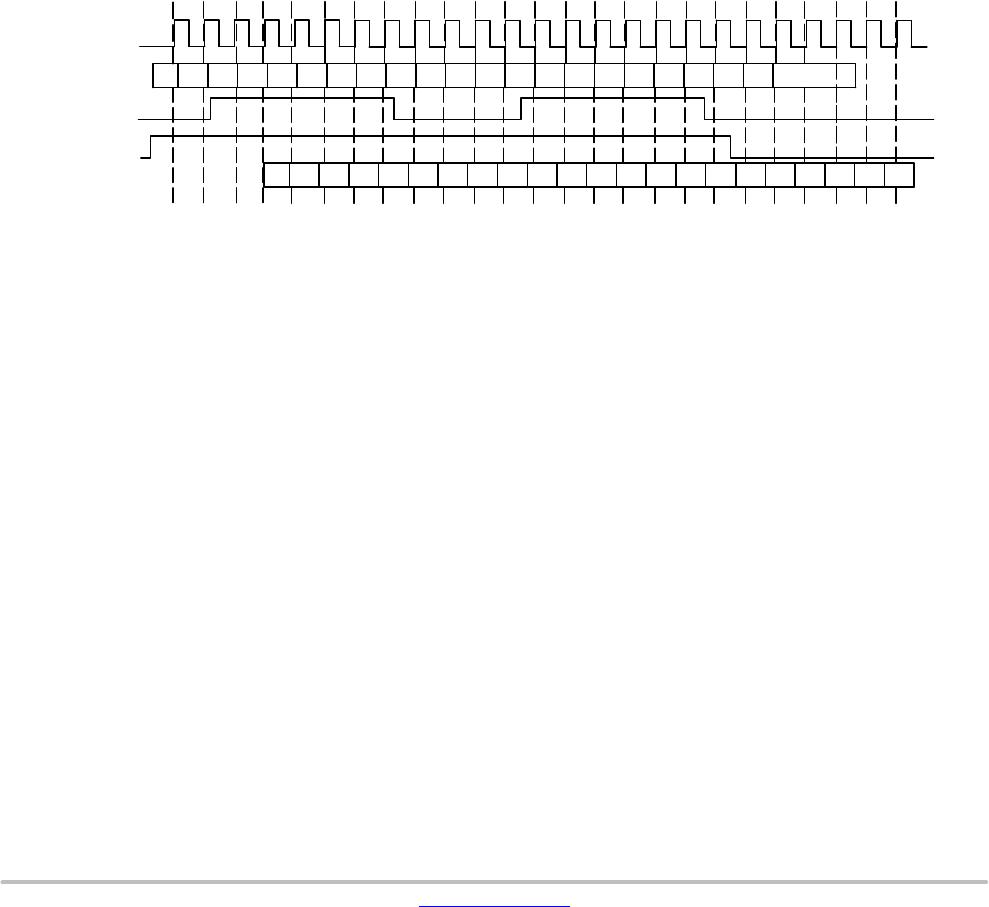

LVDS Output Format

In stand−alone mode, the packet size is 12 bits (2 frame

bits and 10 payload bits); 10−bit pixels or 8−bit pixels can be

selected. In 8−bit pixel mode (R0xB6[0] = 0), the packet

consists of a start bit, 8−bit pixel data (with sync codes), the

line valid bit, the frame valid bit and the stop bit. For 10−bit

pixel mode (R0xB6[0] = 1), the packet consists of a start bit,

10−bit pixel data, and the stop bit.