TC58NVG1S3ETAI0

2012-09-01C

32

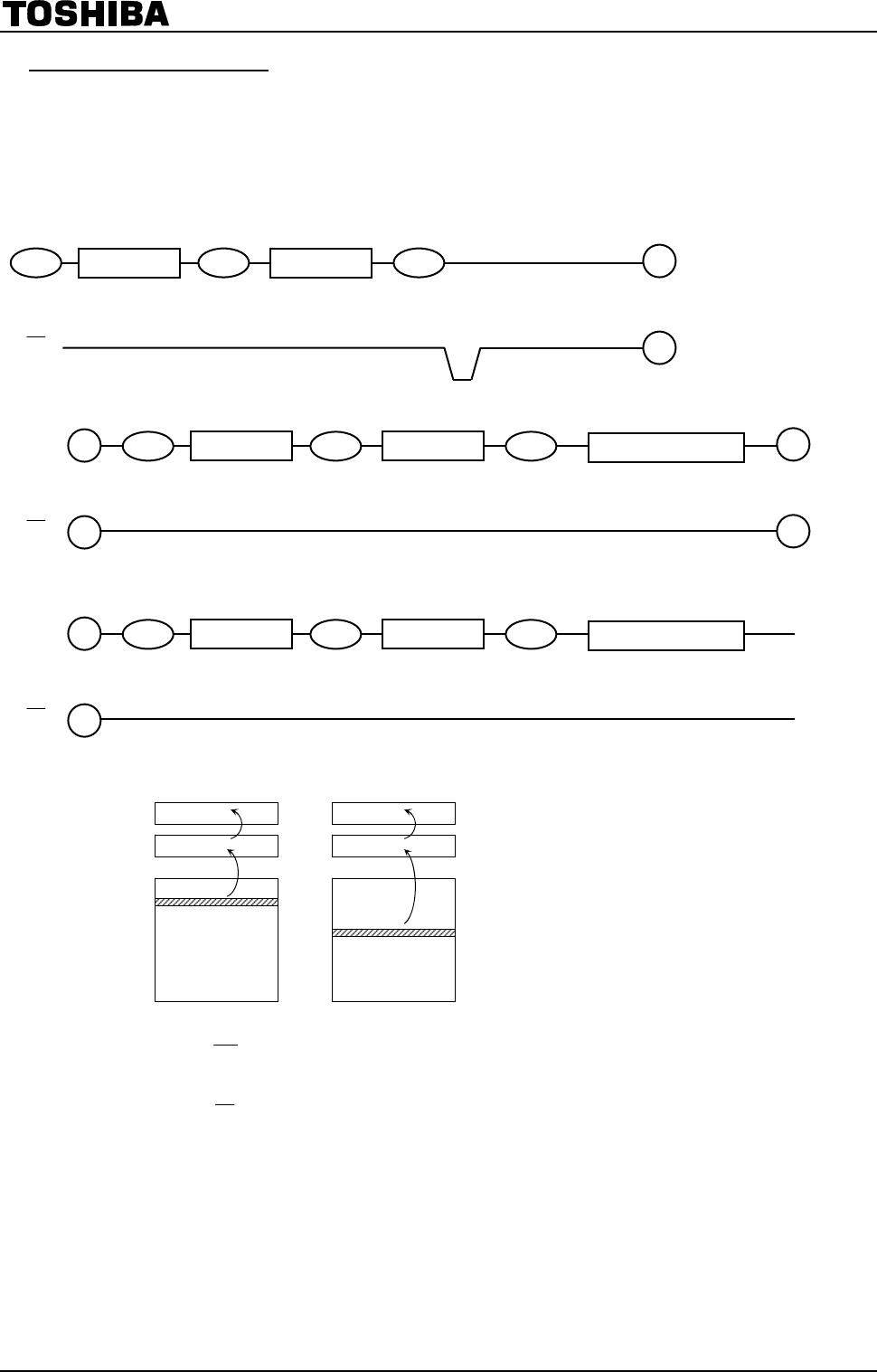

Read Operation with Read Cache

The device has a Read operation with Data Cache that enables the high speed read operation shown below. When the block address changes, this sequence has to be

started from the beginning.

Page N + 2

If the 31h command is issued to the device, the data content of the next page is transferred to the Page Buffer during serial data out from the Data Cache, and therefore the tR (Data transfer from memory

cell to data register) will be reduced.

1 Normal read. Data is transferred from Page N to Data Cache through Page Buffer. During this time period, the device outputs Busy state for tR max.

2 After the Ready/Busy returns to Ready, 31h command is issued and data is transferred to Data Cache from Page Buffer again. This data transfer takes tDCBSYR1 max and the completion of this time

period can be detected by Ready/Busy signal.

3 Data of Page N

+ 1 is transferred to Page Buffer from cell while the data of Page N in Data cache can be read out by /RE clock simultaneously.

4 The 31h command makes data of Page N

+ 1 transfer to Data Cache from Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for tDCBSYR1 max..

This Busy period depends on the combination of the internal data transfer time from cell to Page buffer and the serial data out time.

5 Data of Page N

+ 2 is transferred to Page Buffer from cell while the data of Page N + 1 in Data cache can be read out by /RE clock simultaneously

6 The 3Fh command makes the data of Page N

+ 2 transfer to the Data Cache from the Page Buffer after the completion of the transfer from cell to Page Buffer. The device outputs Busy state for

tDCBSYR1 max.. This Busy period depends on the combination of the internal data transfer time from cell to Page buffer and the serial data out time.

7 Data of Page N

+ 2 in Data Cache can be read out, but since the 3Fh command does not transfer the data from the memory cell to Page Buffer, the device can accept new command input immediately

after the completion of serial data out.

BY/RY

WE

CLE

00h

CE

ALE

I/O

t

R

30h

Col. M Page N

0

1

23

31h 31h

0

1

23

Page Address N

Column 0

2111

Page Address N + 1

2111 0

1

23

Page Address N + 2

2111

3Fh

Data Cache

Page Buffer

Cell Array

1

2

3

3

4

5

5

1

6

7

Page N

Page N

Page N + 1

Page N

30h 31h &

RE clock

Page N + 1

Page N + 2

Page N

+ 1

31h &

RE clock

Page N + 2

3Fh & RE clock

1 2 4

3 5

6

7

t

DCBSYR1

t

DCBSYR1

t

DCBSYR1

RE