XR16C864

10

2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO

REV. 2.2.0

2.2 5-Volt Tolerant Inputs

For devices that have top mark date code "F2 YYWW" and newer, the 864 can accept a voltage of up to 5.5V

on any of its inputs (except XTAL1) when operating from 2.97V to 5.5V. XTAL1 is not 5 volt tolerant. Devices

that have top mark date code "DC YYWW" and older do not have 5V tolerant inputs.

2.3 Device Reset

The RESET input resets the internal registers and the serial interface outputs in all four channels to their

default state (see Table 19). An active high pulse of longer than 40 ns duration will be required to activate the

reset function in the device. Following a power-on reset or an external reset, the 864 is software compatible

with previous generation of UARTs, 16C454 and 16C554 and 16C654.

2.4 Device Identification and Revision

The XR16C864 provides a Device Identification code and a Device Revision code to distinguish the part from

other devices and revisions. To read the identification code from the part, it is required to set the baud rate

generator registers DLL and DLM both to 0x00. Now reading the content of the DLM will provide 0x14 for the

XR16C864 and reading the content of DLL will provide the revision of the part; for example, a reading of 0x01

means revision A.

2.5 Channel Selection

The UART provides the user with the capability to bi-directionally transfer information between an external

CPU and an external serial communication device. During Intel Bus Mode (16/68# pin is connected to VCC), a

logic 0 on chip select pins, CSA#, CSB#, CSC# or CSD# allows the user to select UART channel A, B, C or D

to configure, send transmit data and/or unload receive data to/from the UART. Selecting all four UARTs can be

useful during power up initialization to write to the same internal registers, but do not attempt to read from all

four uarts simultaneously. Individual channel select functions are shown in Table 1.

During Motorola Bus Mode (16/68# pin is connected to GND), the package interface pins are configured for

connection with Motorola, and other popular microprocessor bus types. In this mode the 864 decodes two

additional addresses, A3 and A4, to select one of the four UART ports. The A3 and A4 address decode

function is used only when in the Motorola Bus Mode. See Table 2.

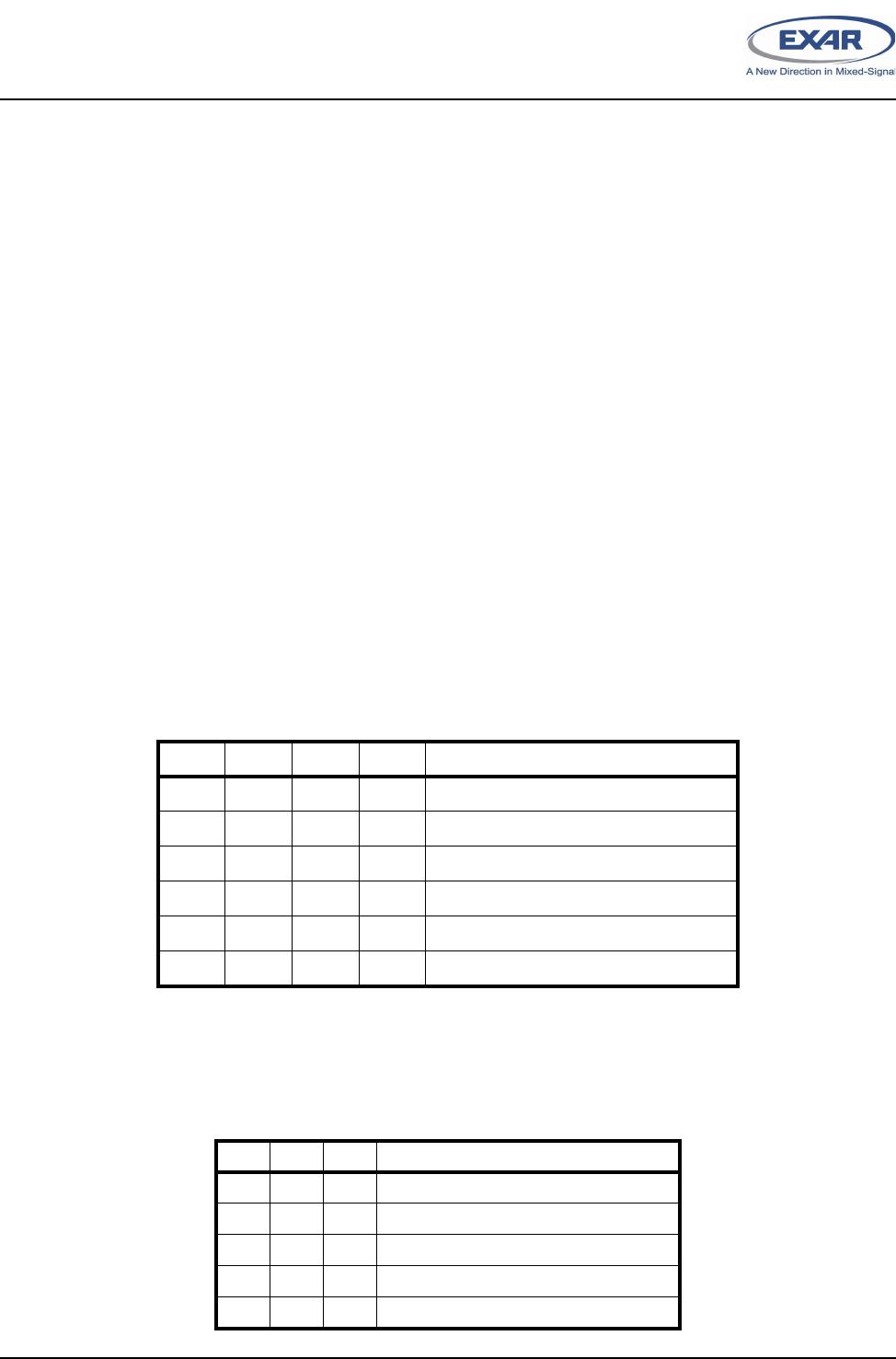

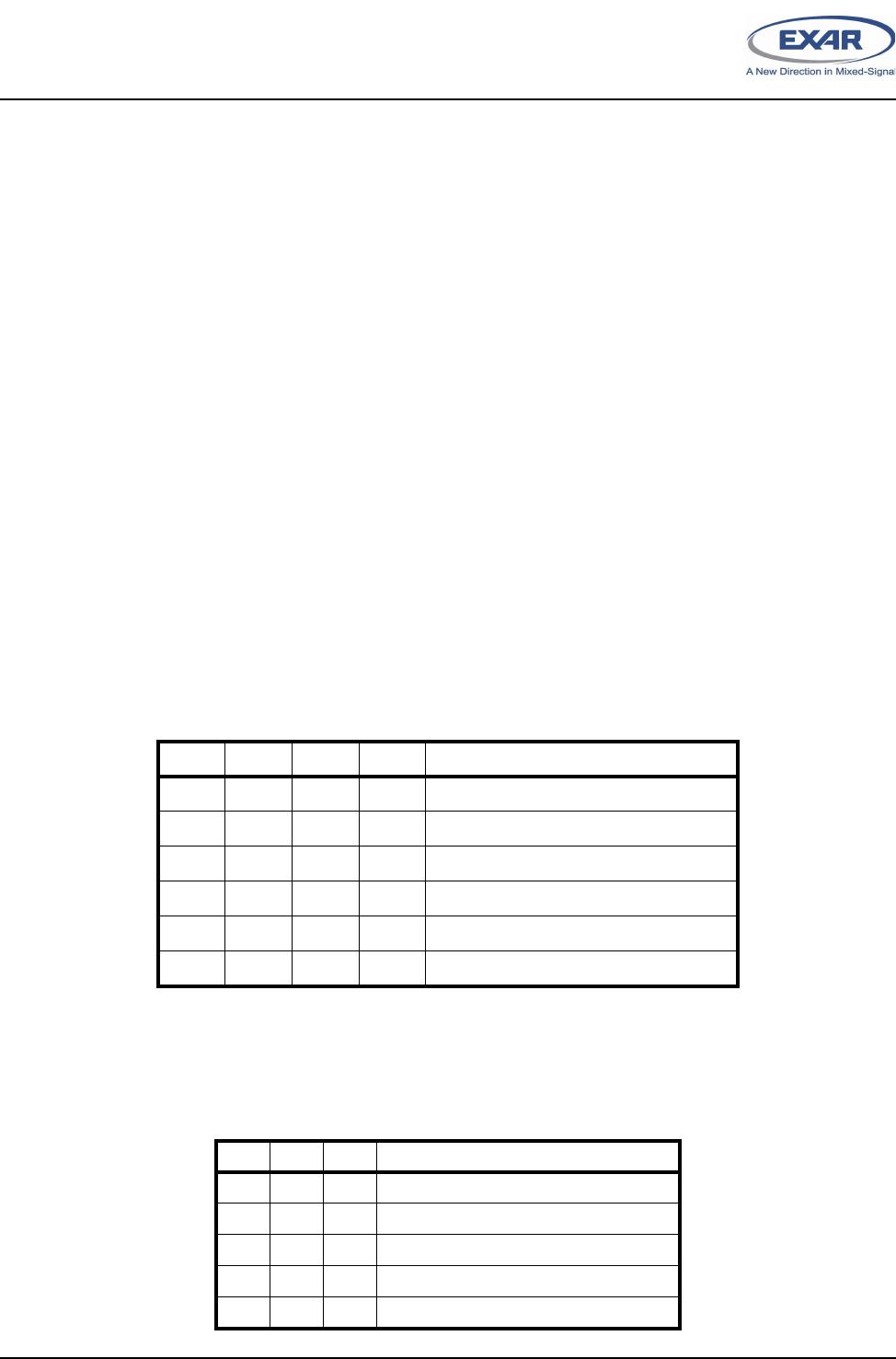

T

ABLE

1: C

HANNEL

A-D S

ELECT

IN

16 M

ODE

CSA# CSB# CSC# CSD# F

UNCTION

1 1 1 1 UART de-selected

0 1 1 1 Channel A selected

1 0 1 1 Channel B selected

1 1 0 1 Channel C selected

1 1 1 0 Channel D selected

0 0 0 0 Channels A-D selected

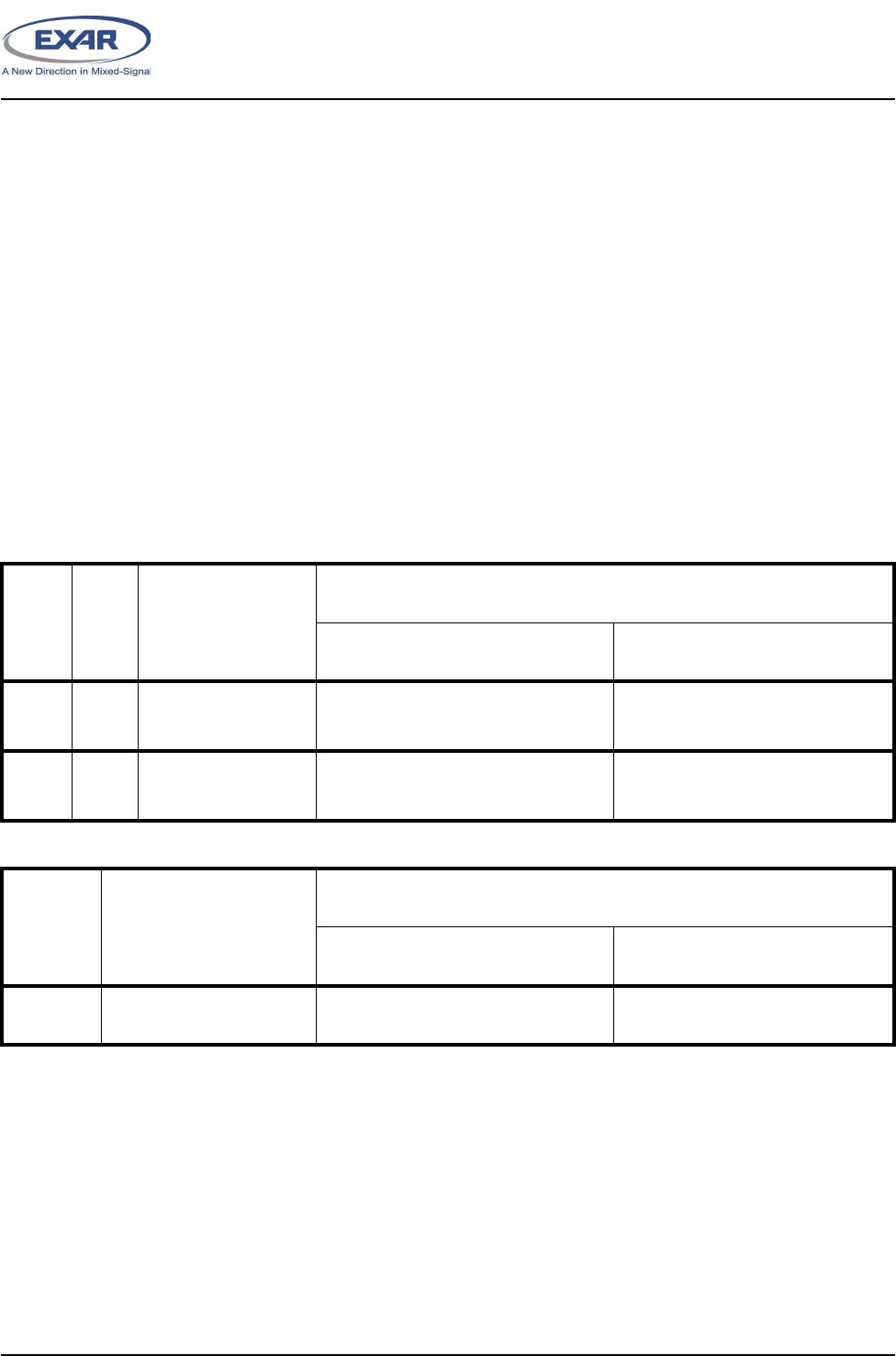

T

ABLE

2: C

HANNEL

A-D S

ELECT

IN

68 M

ODE

CS# A4 A3 F

UNCTION

1 N/A N/A UART de-selected

0 0 0 Channel A selected

0 0 1 Channel B selected

0 1 0 Channel C selected

0 1 1 Channel D selected