51

NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to

improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any

circuits described herein, conveys no license under any patent or other right, and makes no representation that

the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration

purposes and may vary depending upon a user’s specific application. While the information in this publication

has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the

failure or malfunction of the product can reasonably be expected to cause failure of the life support system or

to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless

EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has

been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately

protected under the circumstances.

Copyright 2013 EXAR Corporation

Datasheet April 2013.

Send your UART technical inquiry with technical details to hotline: uarttechsupport@exar.com.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

XR16C864

REV. 2.2.0

2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO

REVISION HISTORY

D

ATE

R

EVISION

D

ESCRIPTION

January 2004 Rev. 2.0

Added Revision History. Changed to standard style format. Clarified

sleep mode conditions. Renamed FIFORdy register to FSTAT register.

Devices with top mark date code of "F2 YYWW" and newer have 5V toler-

ant inputs (except for XTAL1). Devices with top mark date code of "DC

YYWW" and older do not have 5V tolerant inputs.

April 2004 Rev. 2.0.1 Updated FCTR bit-3 description.

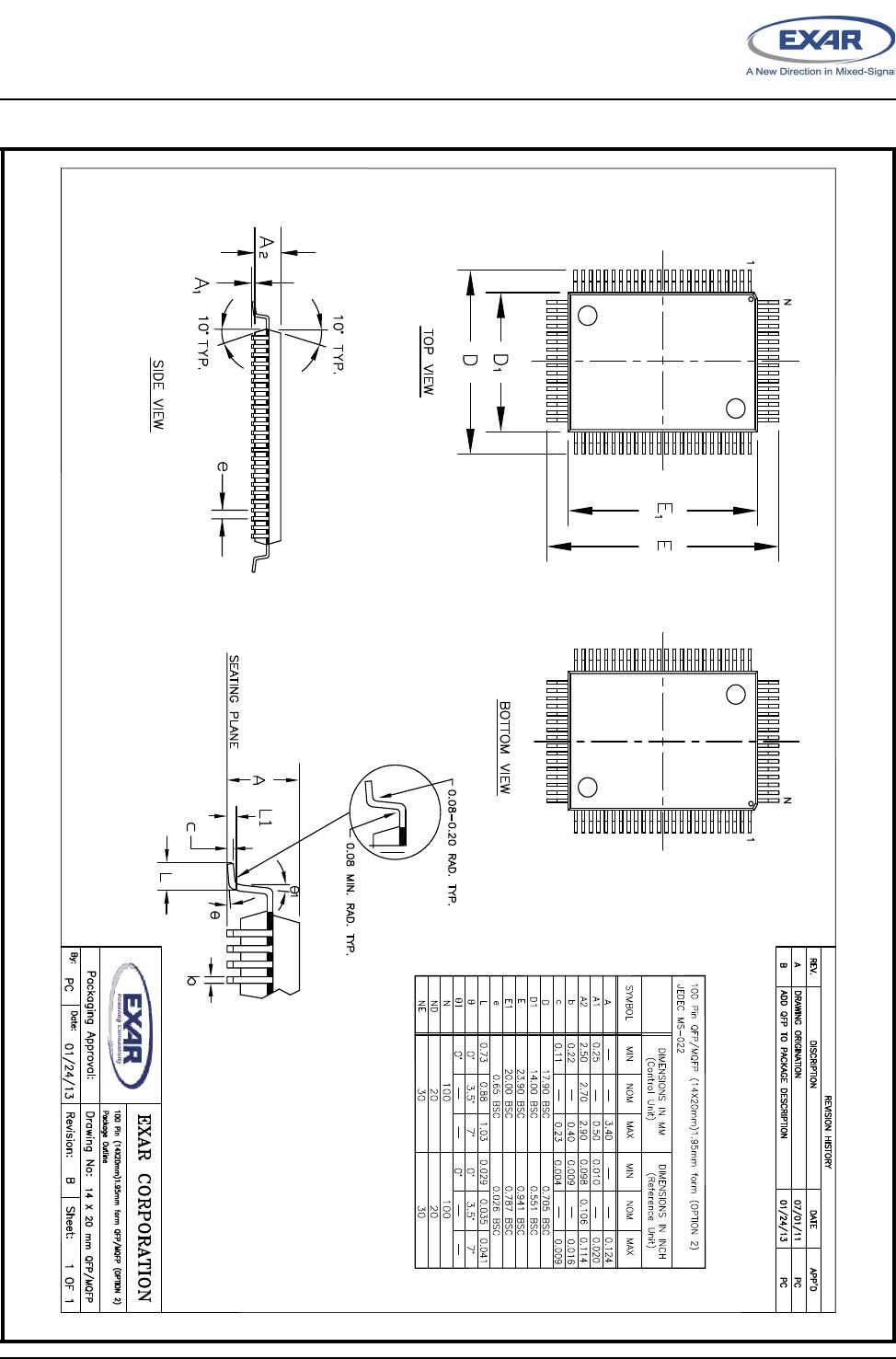

January 2013 Rev 2.1.0 Updated Ordering Information: Removed discontinued part numbers, added

Green/RoHS part numbers and TR part numbers. Updated package drawing.

April 2013 Rev 2.2.0 Updated AC Electrical Characteristics.