XR16C864

40

2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO

REV. 2.2.0

EFR[6]: Auto RTS Flow Control Enable

RTS# output may be used for hardware flow control by setting EFR bit-6 to logic 1. When Auto RTS is

selected, an interrupt will be generated when the receive FIFO is filled to the programmed trigger level and

RTS de-asserts to a logic 1 at the next upper trigger level/hysteresis level. RTS# will return to a logic 0 when

FIFO data falls below the next lower trigger level/hysteresis level. The RTS# output must be asserted (logic 0)

before the auto RTS can take effect. RTS# pin will function as a general purpose output when hardware flow

control is disabled.

•

Logic 0 = Automatic RTS flow control is disabled (default).

•

Logic 1 = Enable Automatic RTS flow control.

EFR[7]: Auto CTS Flow Control Enable

Automatic CTS Flow Control.

•

Logic 0 = Automatic CTS flow control is disabled (default).

•

Logic 1 = Enable Automatic CTS flow control. Data transmission stops when CTS# input de-asserts to logic

1. Data transmission resumes when CTS# returns to a logic 0.

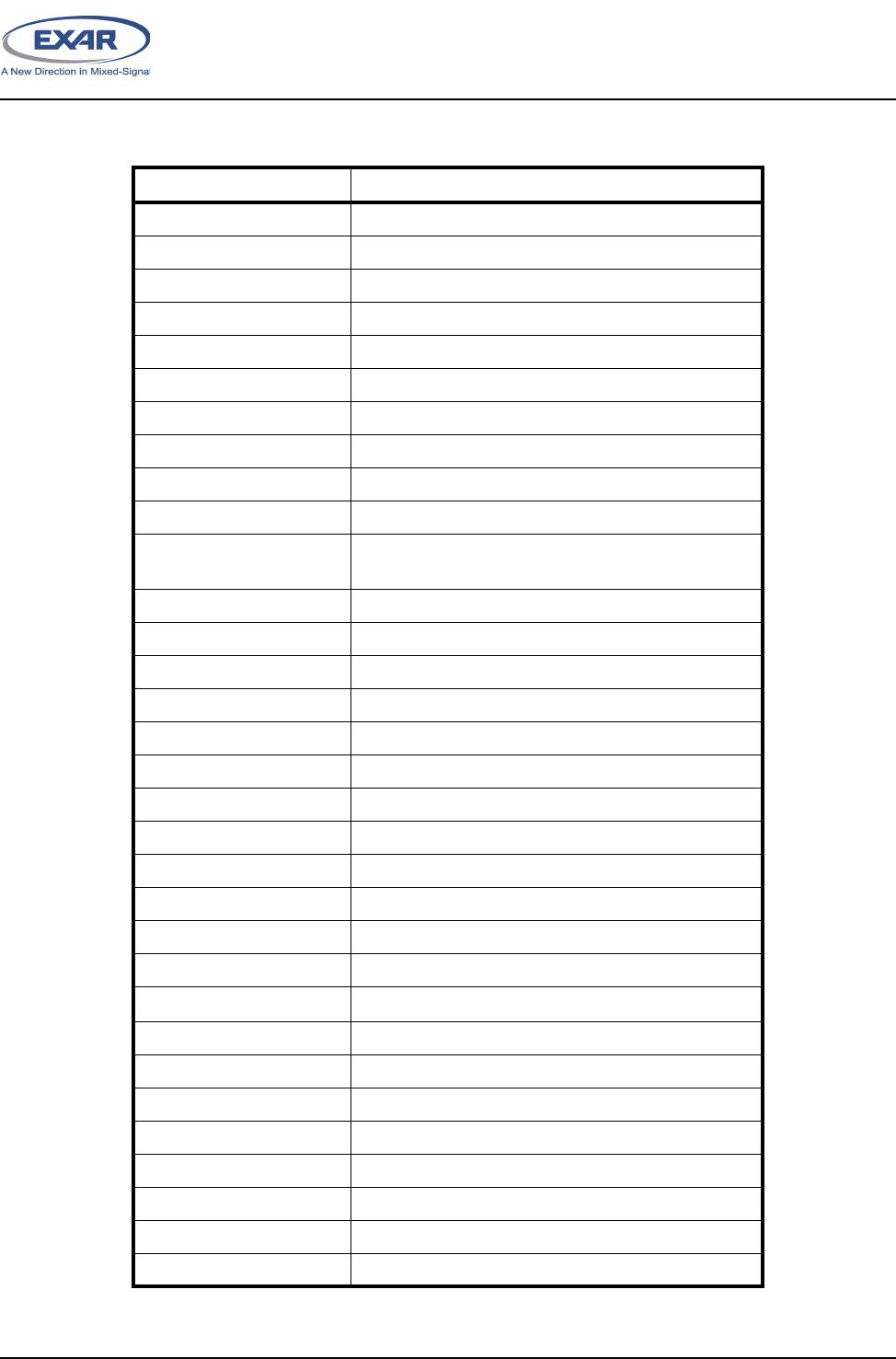

4.20 Software Flow Control Registers (XOFF1, XOFF2, XON1, XON2) - Read/Write

These registers are used as the programmable software flow control characters xoff1, xoff2, xon1, and xon2.

For more details, see

Table 7

.

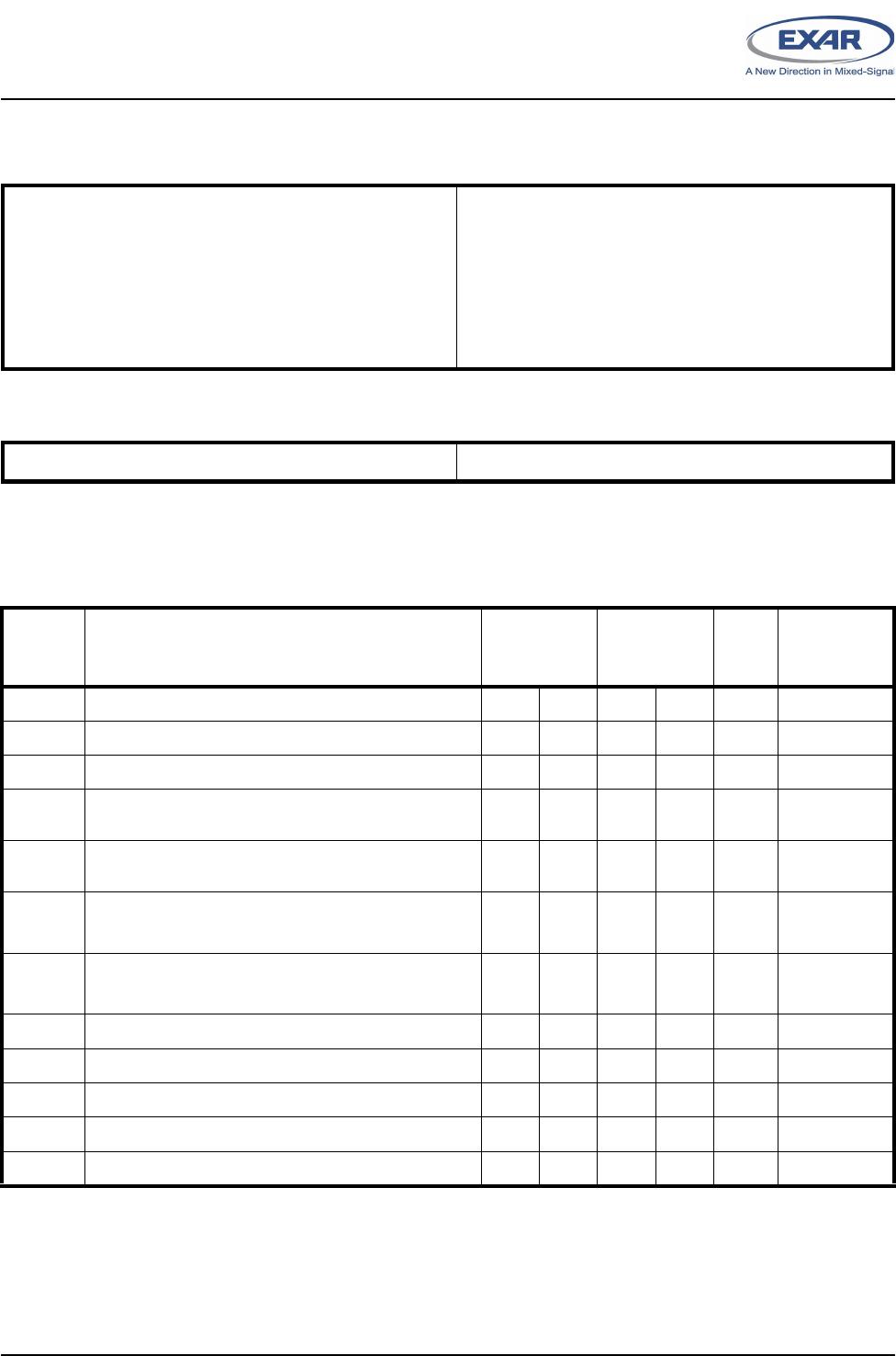

4.21 FIFO Status Register (FSTAT) - Read/Write

The FIFO Status Register provides a status indication for each of the transmit and receive FIFO. These status

bits contain the inverted logic states of the TXRDY# A-D outputs and the (un-inverted) logic states of the

RXRDY# A-D outputs. The contents of the FSTAT register are placed on the data bus when the FSRS# pin (pin

76) is a logic 0. Also see FSRS# pin description.

FSTAT[3:0]: TXRDY# A-D Status Bits

Please see

Table 5

for the interpretation of the TXRDY# signals.

FSTAT[7:4]: RXRDY# A-D Status Bits

Please see

Table 5

for the interpretation of the RXRDY# signals.