XR16C864

4

2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO

REV. 2.2.0

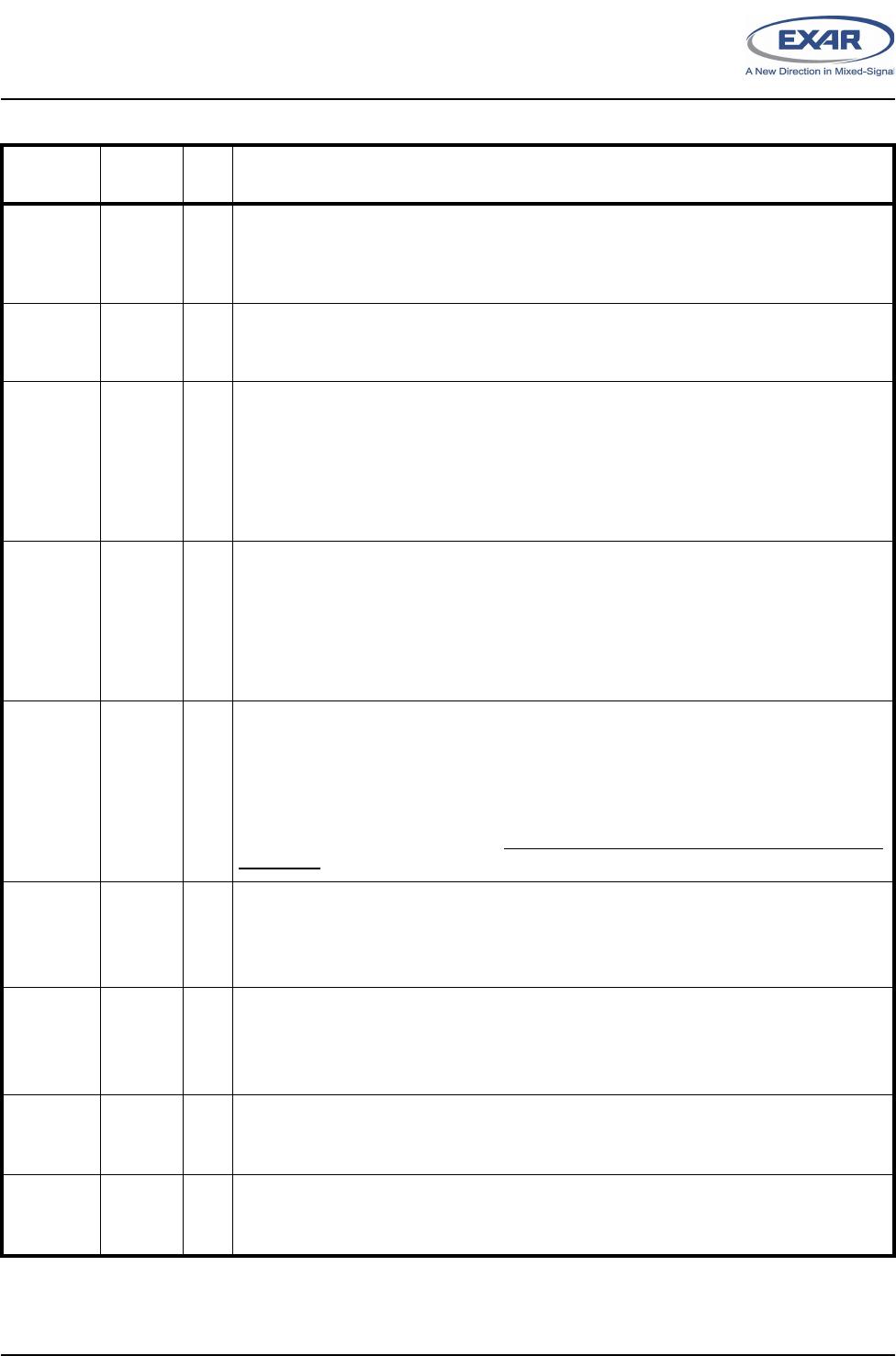

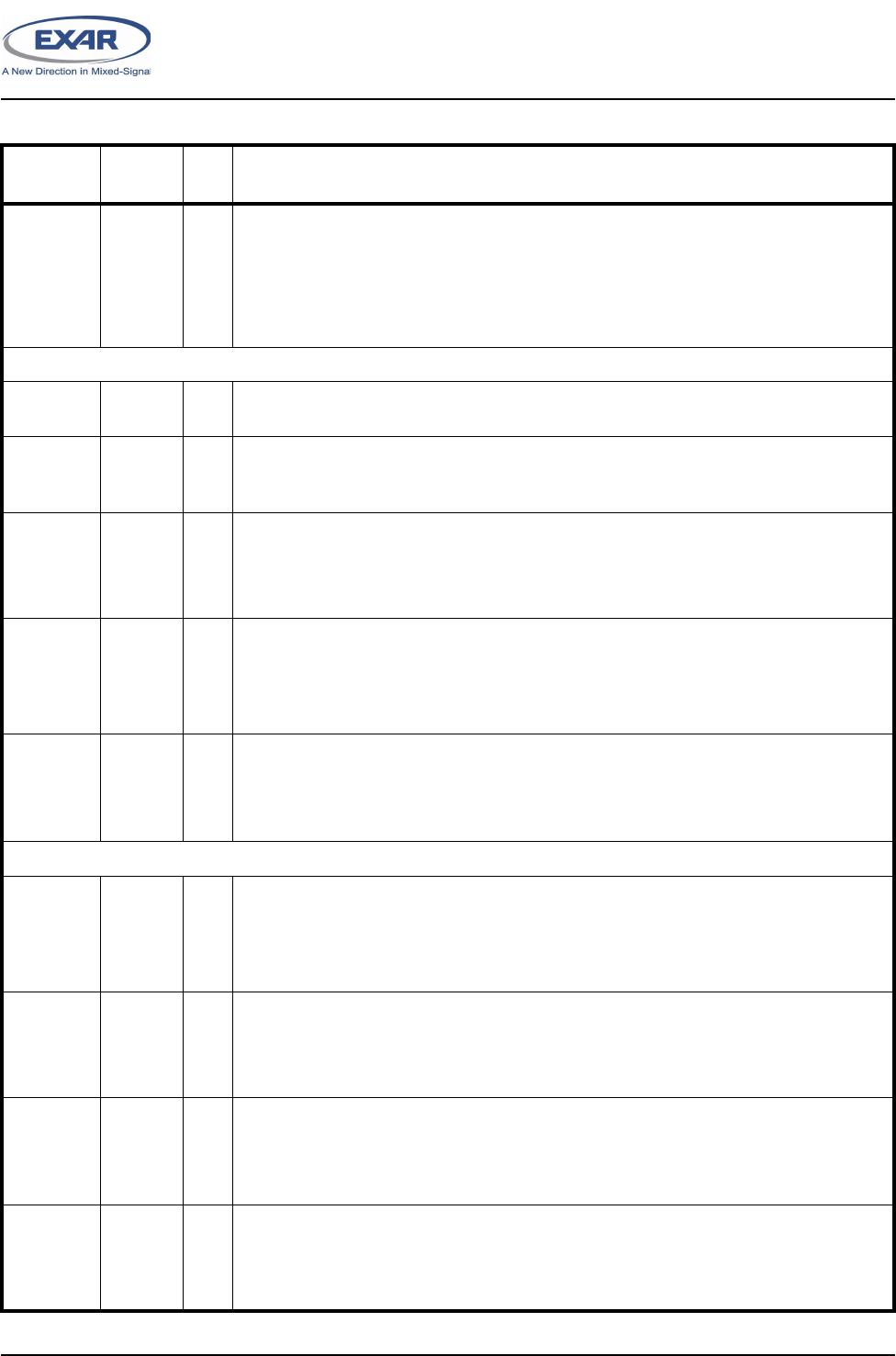

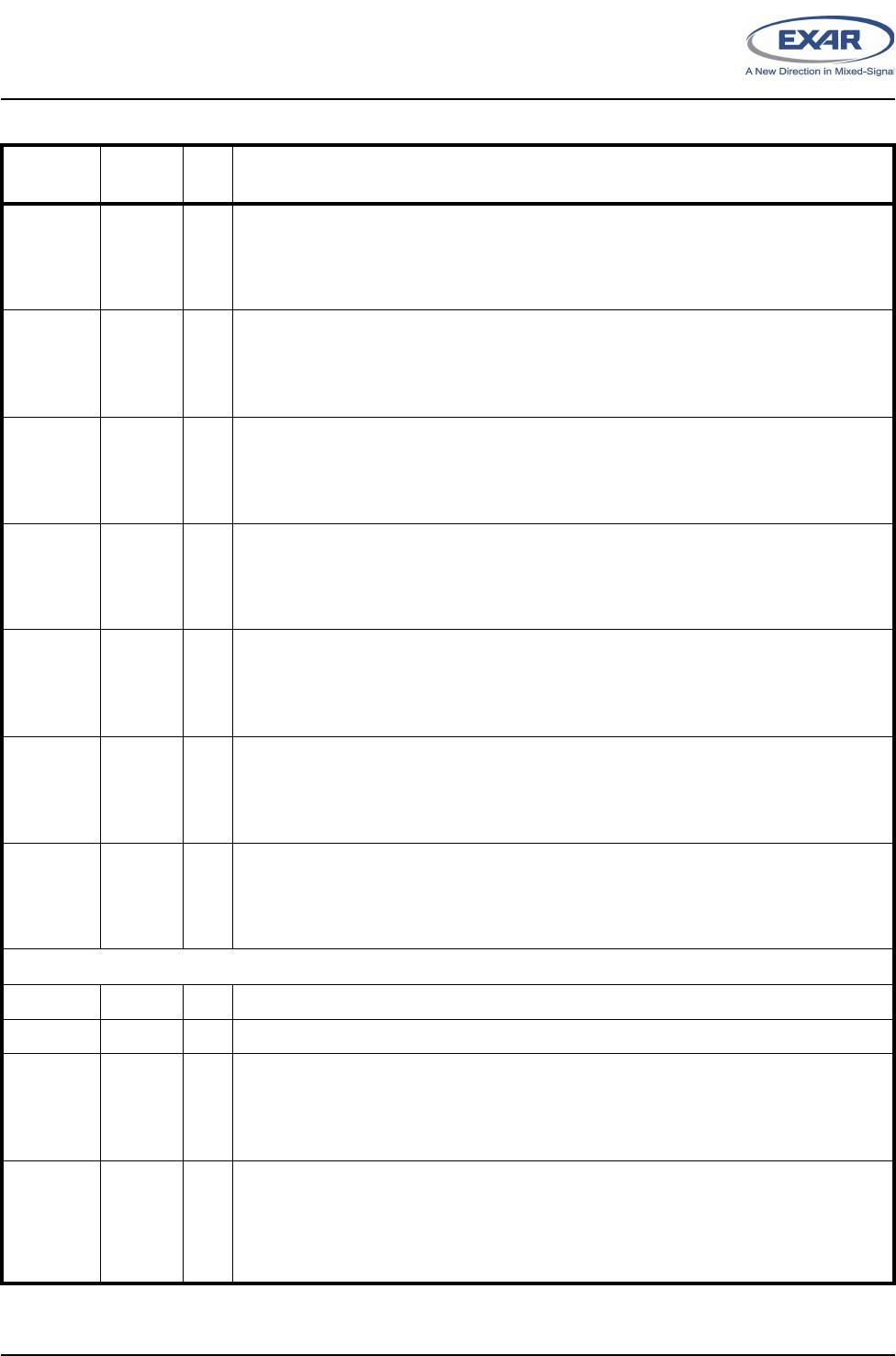

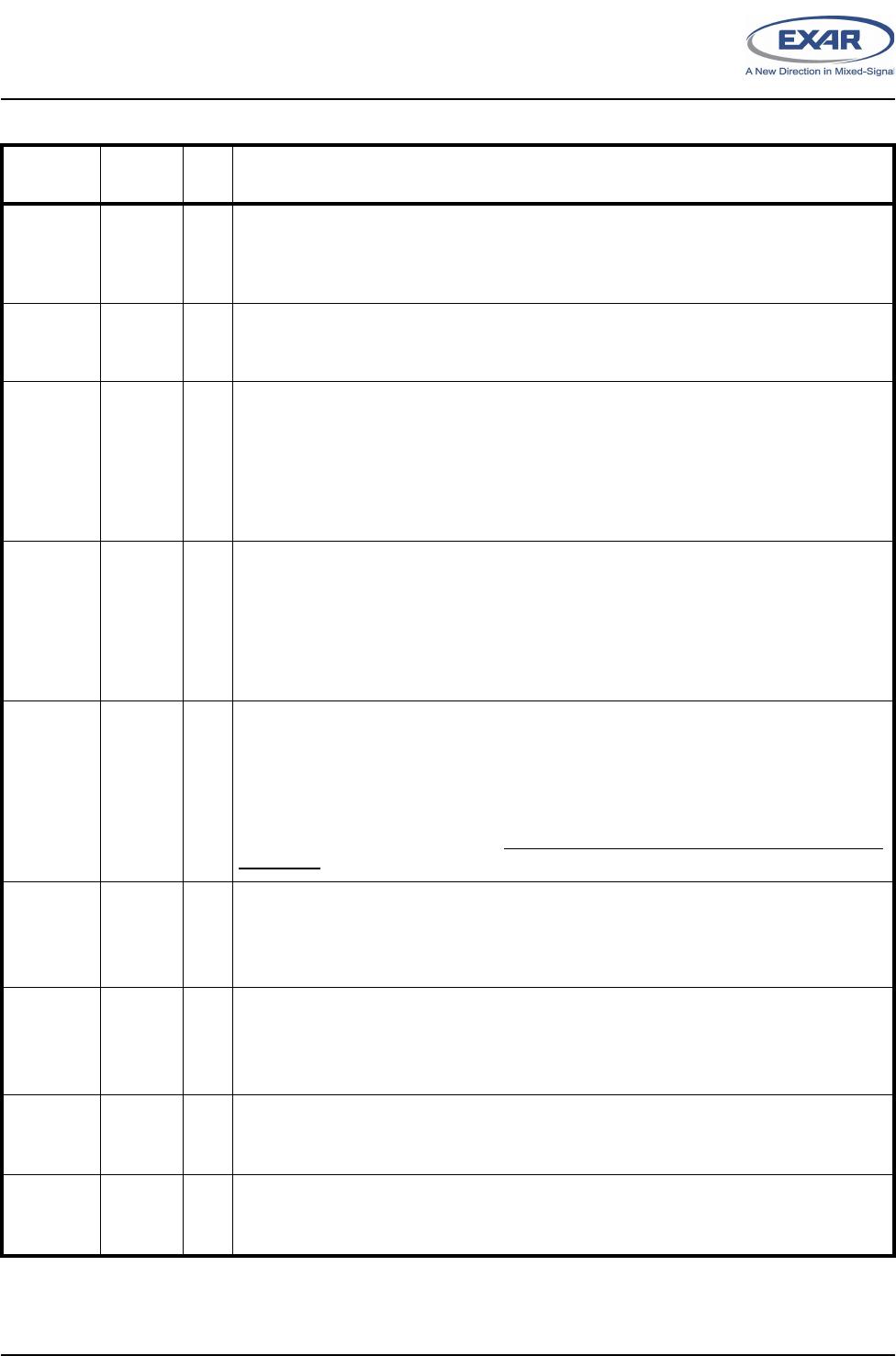

CSC#

(A4)

64 I When 16/68# pin is at logic 1, this input is chip select C (active low) to enable channel C

in the device.

When 16/68# pin is at logic 0, this input becomes address line A4 which is used for chan-

nel selection in the Motorola bus interface.

CSD#

(N.C.)

68 I When 16/68# pin is at logic 1, this input is chip select D (active low) to enable channel D

in the device.

When 16/68# pin is at logic 0, this input is not used.

INTA

(IRQ#)

12 O

(OD)

When 16/68# pin is at logic 1 for Intel bus interface, this ouput becomes channel A inter-

rupt output. The output state is defined by the user and through the software setting of

MCR[3]. INTA is set to the active mode when MCR[3] is set to a logic 1. INTA is set to the

three state mode when MCR[3] is set to a logic 0 (default). See MCR[3].

When 16/68# pin is at logic 0 for Motorola bus interface, this output becomes device inter-

rupt output (active low, open drain). An external pull-up resistor is required for proper

operation.

INTB

INTC

INTD

(N.C.)

18

63

69

O When 16/68# pin is at logic 1 for Intel bus interface, these ouputs become the interrupt

outputs for channels B, C, and D. The output state is defined by the user through the soft-

ware setting of MCR[3]. The interrupt outputs are set to the active mode when MCR[3] is

set to a logic 1 and are set to the three state mode when MCR[3] is set to a logic 0

(default). See MCR[3].

When 16/68# pin is at logic 0 for Motorola bus interface, these outputs are unused and

will stay at logic zero level. Leave these outputs unconnected.

INTSEL 87 I Interrupt Select (active high, input with internal pull-down).

When 16/68# pin is at logic 1 for Intel bus interface, this pin can be used in conjunction

with MCR bit-3 to enable or disable the INT A-D pins or override MCR bit-3 and enable

the interrupt outputs. Interrupt outputs are enabled continuously by making this pin a

logic 1. Making this pin a logic 0 allows MCR bit-3 to enable and disable the interrupt out-

put pins. In this mode, MCR bit-3 is set to a logic 1 to enable the continuous output. See

MCR bit-3 description for full detail. This pin must be at logic 0 in the Motorola bus inter-

face mode.

TXRDYA#

TXRDYB#

TXRDYC#

TXRDYD#

5

25

56

81

O

UART channels A-D Transmitter Ready (active low). These outputs provide the TX FIFO/

THR status for transmit channels A-D. See

Table 5

. If Direct Memory Access is enabled,

these outputs become Transmit Direct Memory Access Request outputs. See TXDRQ pin

description for more details. If these outputs are unused, leave them unconnected.

RXRDYA#

RXRDYB#

RXRDYC#

RXRDYD#

100

31

50

82

O UART channels A-D Receiver Ready (active low). These outputs provide the RX FIFO/

RHR status for receive channels A-D. See

Table 5

. If Direct Memory Access is enabled,

these outputs become Receive Direct Memory Access Request outputs. See RXDRQ pin

description for more details. If these outputs are unused, leave them unconnected.

TXRDY# 45 O Transmitter Ready (active low). This output is a logically wire-ORed status of TXRDY#

A-D. See

Table 5

. If this output is unused, leave it unconnected.

RXRDY# 44 O Receiver Ready (active low). This output is a logically wire-ORed status of RXRDY# A-D.

See

Table 5

. If this output is unused, leave it unconnected.

Pin Description

N

AME

100-QFP

P

IN

#

T

YPE

D

ESCRIPTION