XR16C864

17

REV. 2.2.0

2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO

2.15 Auto RTS Hysteresis

The 864 has a new feature that provides flow control trigger hysteresis while maintaining compatibility with the

XR16C850, ST16C650A and ST16C550 family of UARTs. With the Auto RTS function enabled, an interrupt is

generated when the receive FIFO reaches the programmed RX trigger level. The RTS# pin will not be forced

to a logic 1 (RTS off), until the receive FIFO reaches the upper limit of the hysteresis level. The RTS# pin will

return to a logic 0 after the RX FIFO is unloaded to the lower limit of the hysteresis level. Under the above

described conditions, the 864 will continue to accept data until the receive FIFO gets full. The Auto RTS

function is initiated when the RTS# output pin is asserted to a logic 0 (RTS On). Table 15 shows the complete

details for the Auto RTS# Hysteresis levels. Please note that this table is for programmable trigger levels only

(Table D). The hysteresis values for Tables A-C are the next higher and next lower trigger levels in Tables A-C

(See Table 11).

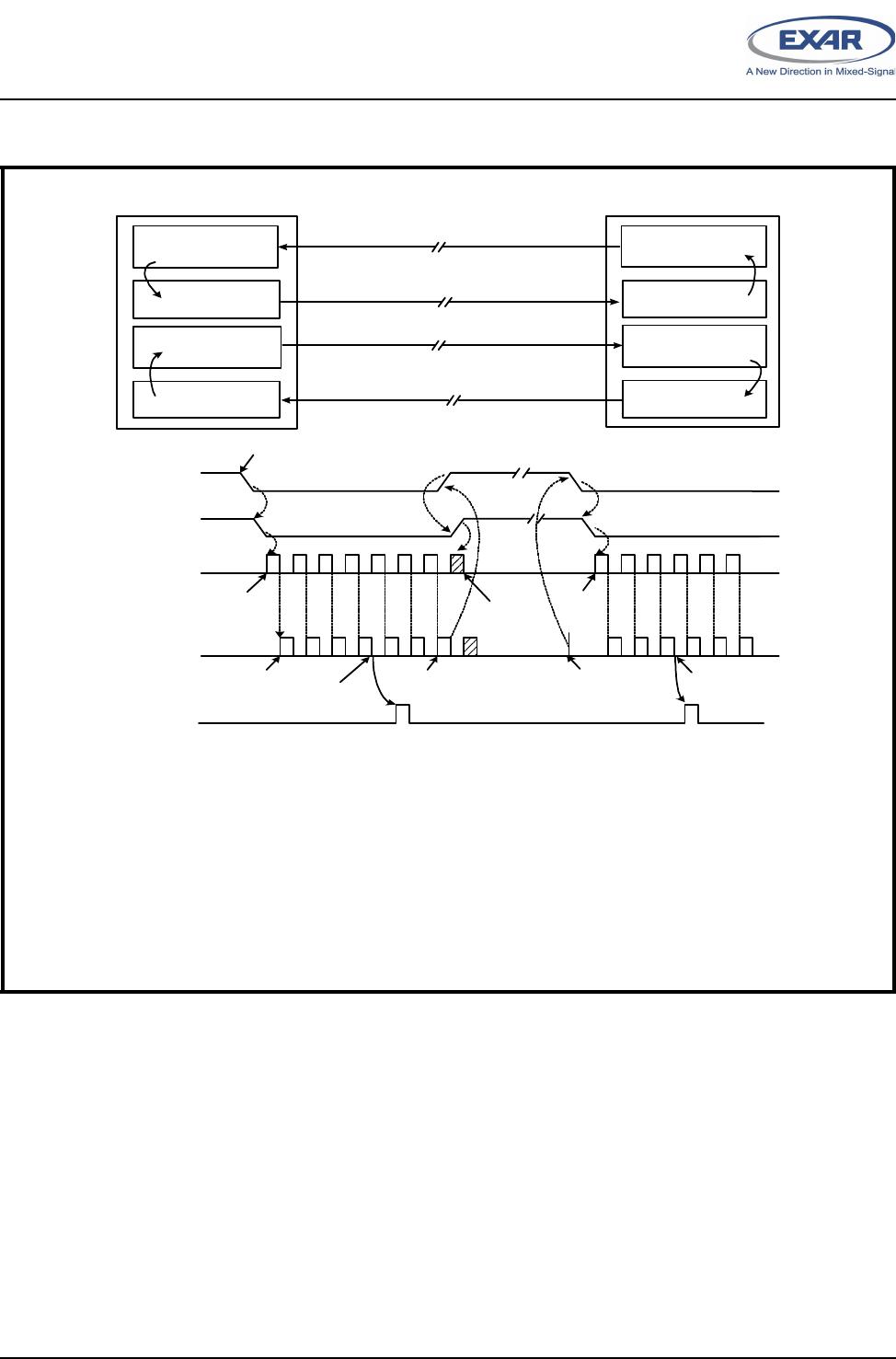

2.16 Auto CTS Flow Control

Automatic CTS flow control is used to prevent data overrun to the remote receiver FIFO. The CTS# input is

monitored to suspend/restart the local transmitter. The auto CTS flow control feature is selected to fit specific

application requirement (see Figure 10):

•

Enable auto CTS flow control using EFR bit-7.

If using the Auto CTS interrupt:

•

Enable CTS interrupt through IER bit-7 (after setting EFR bit-4). The UART issues an interrupt when the

CTS# pin is de-asserted (logic 1): ISR bit-5 will be set to 1, and UART will suspend transmission as soon as

the stop bit of the character in process is shifted out. Transmission is resumed after the CTS# input is re-

asserted (logic 0), indicating more data may be sent.