XR16C864

19

REV. 2.2.0

2.97V TO 5.5V QUAD UART WITH 128-BYTE FIFO

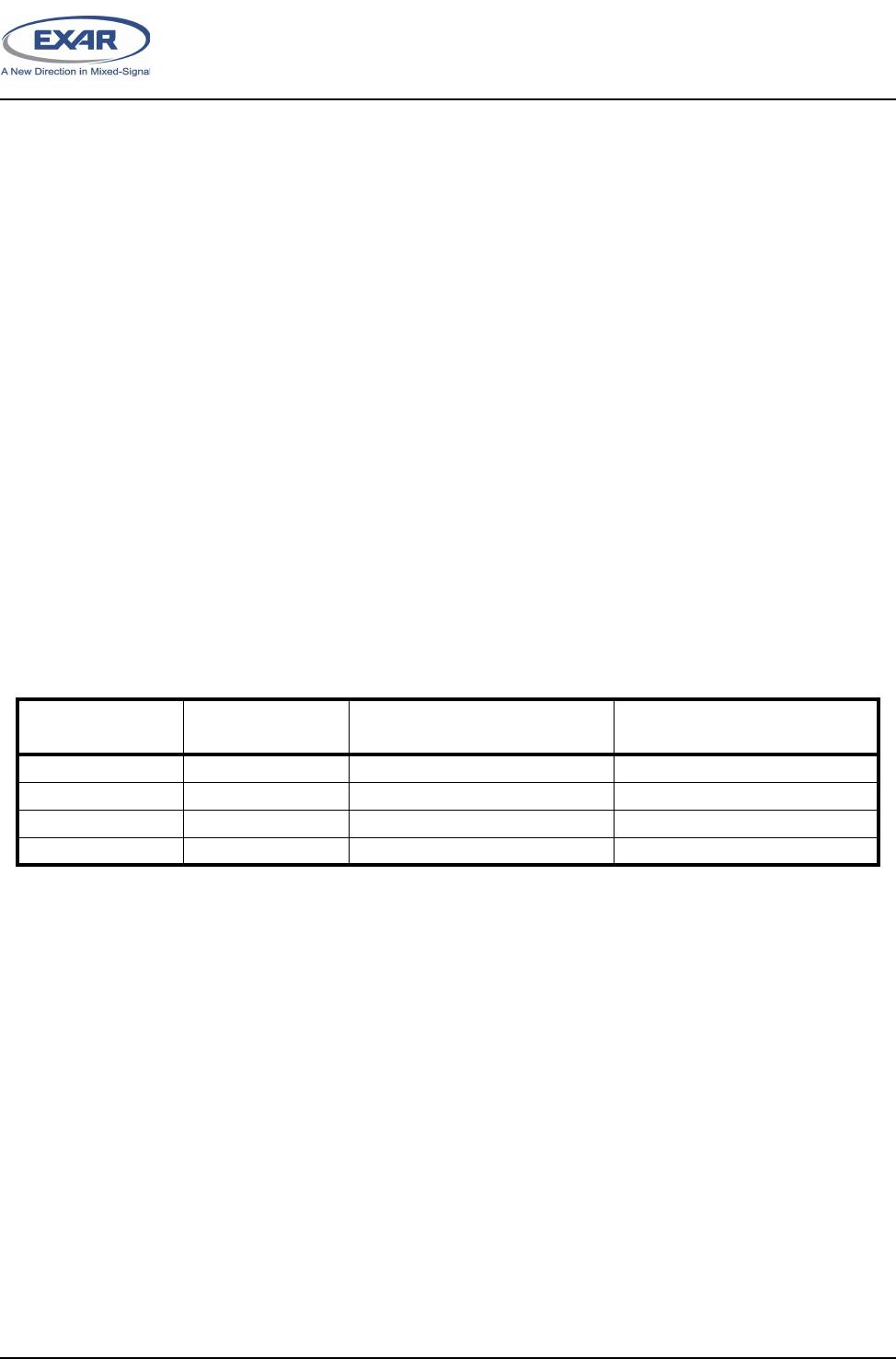

2.17 Auto Xon/Xoff (Software) Flow Control

When software flow control is enabled (See Table 18), the 864 compares one or two sequential receive data

characters with the programmed Xon or Xoff-1,2 character value(s). If receive character(s) match the

programmed values, the 864 will halt transmission as soon as the current character has completed

transmission. When a match occurs, the Xoff (if enabled via IER bit-5) flag will be set and the interrupt output

pin will be activated. Following a suspension due to a match of the Xoff character, the 864 will monitor the

receive data stream for a match to the Xon-1,2 character. If a match is found, the 864 will resume operation

and clear the flags (ISR bit-4).

Reset initially sets the contents of the Xon/Xoff 8-bit flow control registers to a logic 0. Following reset the user

can write any Xon/Xoff value desired for software flow control. Different conditions can be set to detect Xon/

Xoff characters (See Table 18) and suspend/resume transmissions. When double 8-bit Xon/Xoff characters

are selected, the 864 compares two consecutive receive characters with two software flow control 8-bit values

(Xon1, Xon2, Xoff1, Xoff2) and controls TX transmissions accordingly. Under the above described flow control

mechanisms, flow control characters are not placed (stacked) in the user accessible RX data buffer or FIFO.

In the event that the receive buffer is overfilling and flow control needs to be executed, the 864 automatically

sends an Xoff message (when enabled) via the serial TX output to the remote modem. The 864 sends the Xoff-

1,2 characters two-character-times (= time taken to send two characters at the programmed baud rate) after

the receive FIFO crosses the programmed trigger level (for all trigger tables A-D). To clear this condition, the

864 will transmit the programmed Xon-1,2 characters as soon as receive FIFO is less than one trigger level

below the programmed trigger level (for Trigger Tables A, B, and C) or when receive FIFO is less than the

trigger level minus the hysteresis value (for Trigger Table D). This hysteresis value is the same as the Auto

RTS Hysteresis value in Table 15. Table 7 below explains this when Trigger Table-B (See Table 11) is

selected.

* After the trigger level is reached, an xoff character is sent after a short span of time (= time required to send 2

characters); for example, after 2.083ms has elapsed for 9600 baud and 10-bit word length setting.

2.18 Special Character Detect

A special character detect feature is provided to detect an 8-bit character when bit-5 is set in the Enhanced

Feature Register (EFR). When this character (Xoff2) is detected, it will be placed in the FIFO along with normal

incoming RX data.

The 864 compares each incoming receive character with Xoff-2 data. If a match exists, the received data will

be transferred to FIFO and ISR bit-4 will be set to indicate detection of special character. Although the Internal

Register Table shows Xon, Xoff Registers with eight bits of character information, the actual number of bits is

dependent on the programmed word length. Line Control Register (LCR) bits 0-1 defines the number of

character bits, i.e., either 5 bits, 6 bits, 7 bits, or 8 bits. The word length selected by LCR bits 0-1 also

determines the number of bits that will be used for the special character comparison. Bit-0 in the Xon, Xoff

Registers corresponds with the LSB bit for the receive character.

T

ABLE

7: A

UTO

X

ON

/X

OFF

(S

OFTWARE

) F

LOW

C

ONTROL

RX T

RIGGER

L

EVEL

INT P

IN

A

CTIVATION

X

OFF

C

HARACTER

(

S

) S

ENT

(

CHARACTERS

IN

RX

FIFO

)

X

ON

C

HARACTER

(

S

) S

ENT

(

CHARACTERS

IN

RX

FIFO

)

8 8 8* 0

16 16 16* 8

24 24 24* 16

28 28 28* 24