ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 15

ICS1894-40 REV K 022412

Pins for Monitoring the Data Link table

Note:

1. During either power-on reset or hardware reset, each

multi-function configuration pin is an input that is sampled

when the ICS1894-40 exits the reset state. After sampling is

complete, these pins are output pins that can drive status

LEDs.

2. A software reset does not affect the state of a

multi-function configuration pin. During a software reset, all

multi-function configuration pins are outputs.

3. The P0/LED0 and P1/ISO/LED1 pins must be pulled

either up or down with an external resistor to establish the

address of the ICS1894-40. The P2/INT, P3/RXD2 and

P4/LED2 pins have internal pull-up/ pull-down resistors.

LEDs may be placed in series with these resistors to provide

a designated status indicator as described in the Pins for

Monitoring the Data Link table. Use 1KΩ resistors.

Caution: Pins listed in the Pins for Monitoring the Data Link

table must not float.

4. As outputs, the asserted state of a multi-function

configuration pin is the inverse of the sense sampled during

reset. This inversion provides a signal that can illuminate an

LED during an asserted state. For example, if a

multi-function configuration pin is pulled down to ground

through an LED and a current-limiting resistor, then the

sampled sense of the input is low. To illuminate this LED for

the asserted state, the output is driven high.

5. Adding 10KΩ resistors across the LEDs ensures the PHY

address is fully defined during slow VDD power-ramp

conditions.

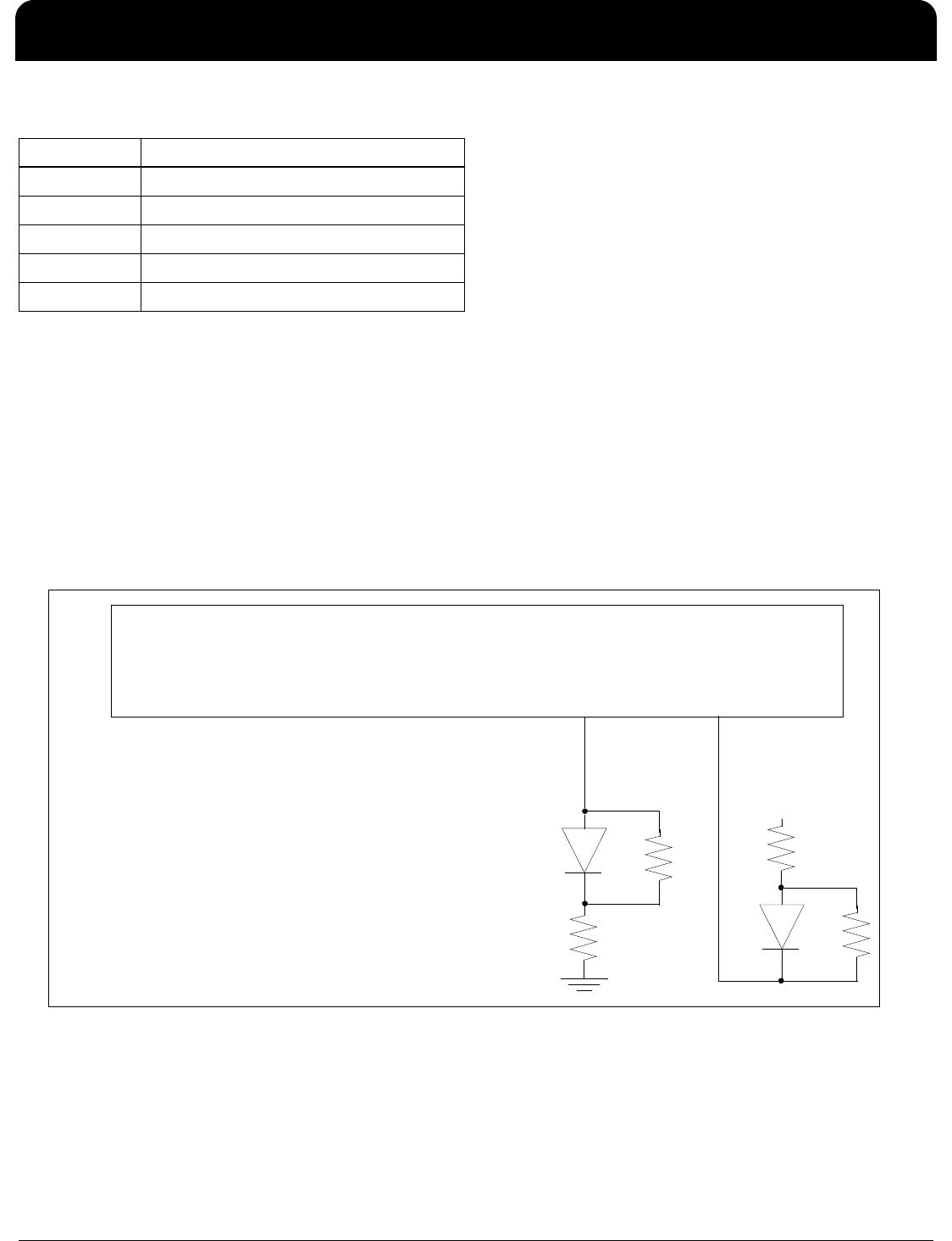

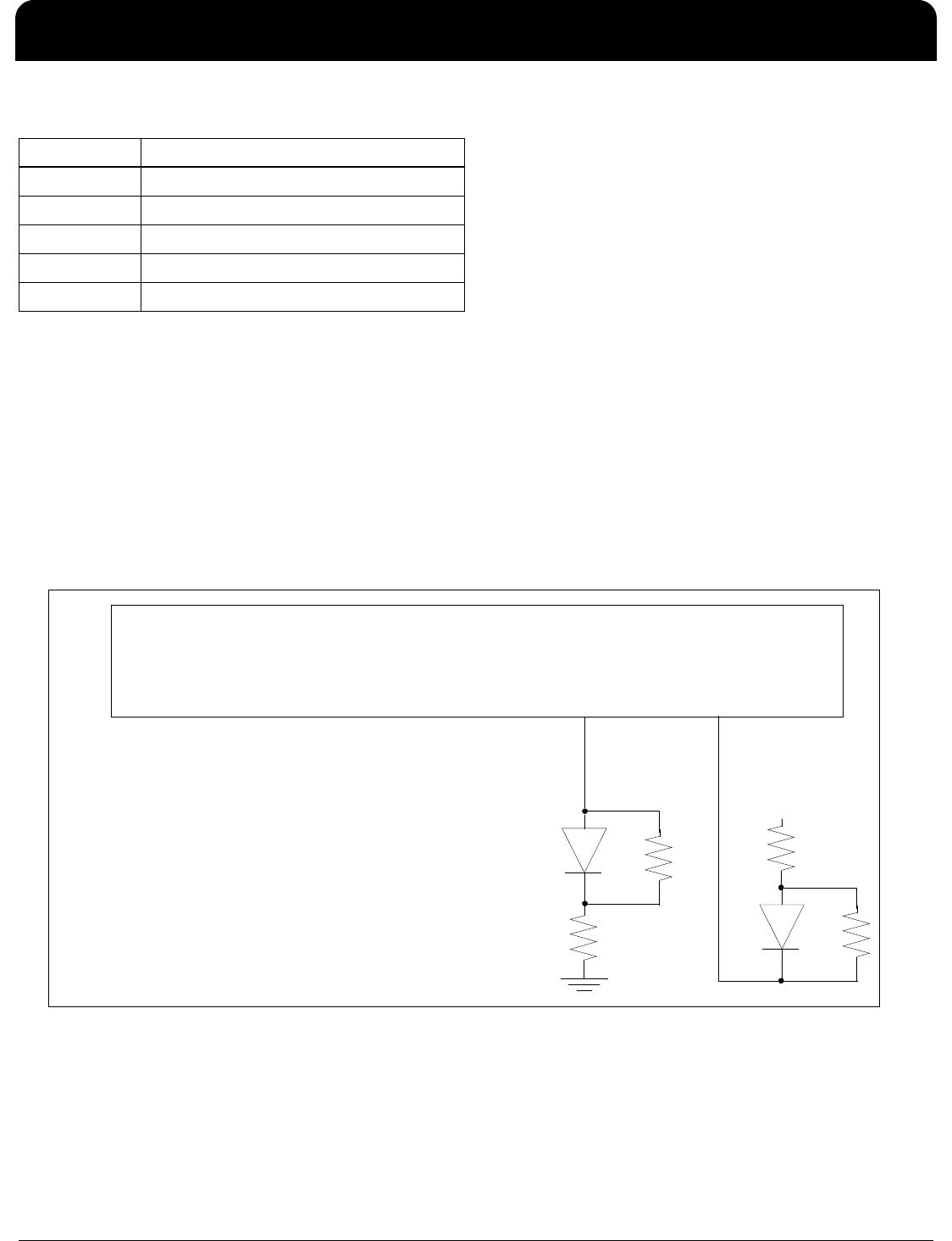

The following figure shows typical biasing and LED connections for the ICS1894-40.

The above circuit decodes the PHY address = 17

Pin LED Driven by the Pin’s Output Signal

P0/LED0 Link, Activity, Tx, Rx, COL, Mode, Dplx

P1/ISO/LED1 Link, Activity, Tx, Rx, COL, Mode, Dplx

P4/LED2 Link, Activity, Tx, Rx, COL, Mode, Dplx

LED3 Link, Activity, Tx, Rx, COL, Mode, Dplx

SI/LED4 Link, Activity, Tx, Rx, COL, Mode, Dplx

ICS1894-40

38

19 12 40 39

P4/LED2

(always

latched high)

P3/RXD2 P2/INT P1/ISO/LED1 P0/LED0

LED0

1KΩ

10KΩ

VDD

LED1

1KΩ

10KΩ