ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 24

ICS1894-40 REV K 022412

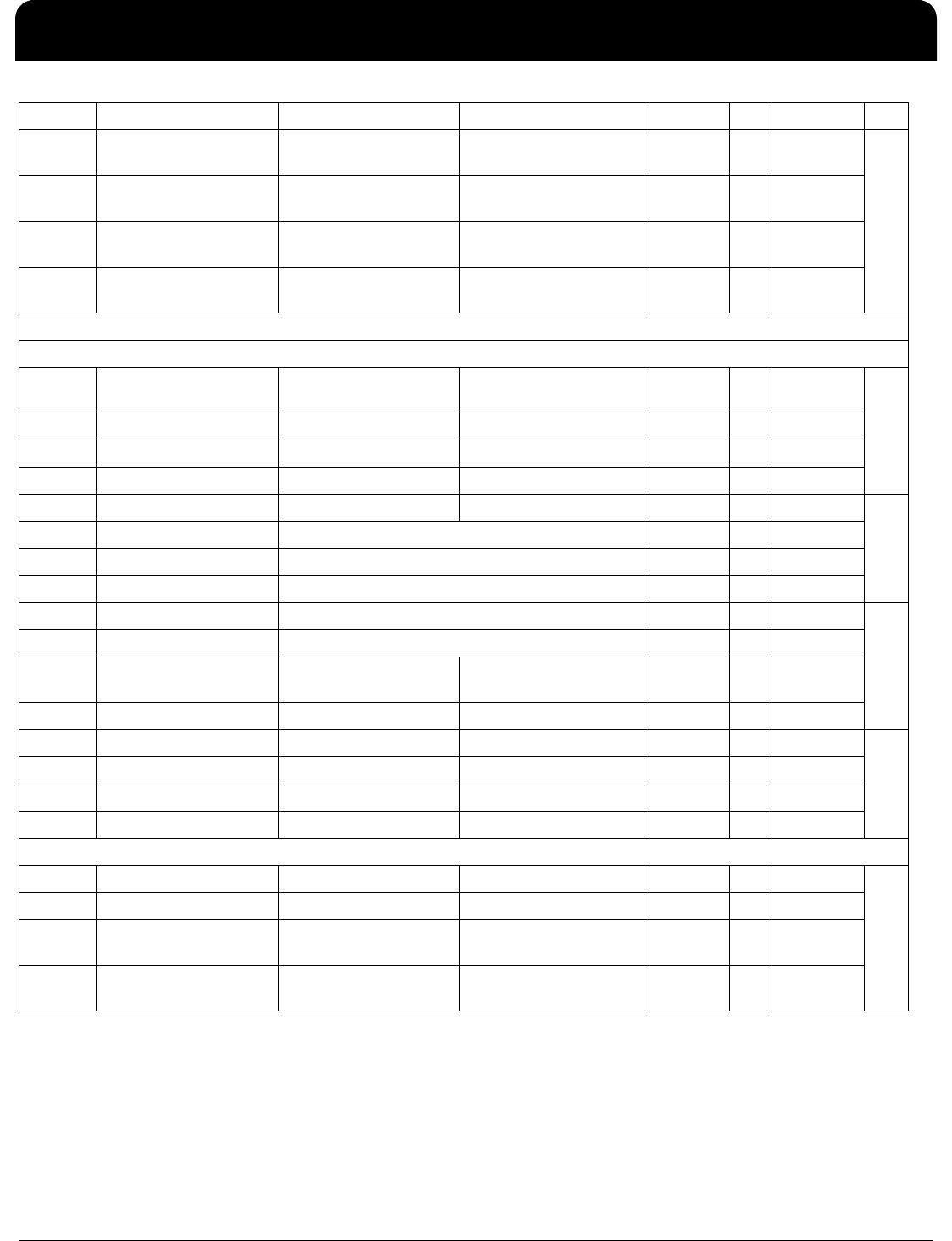

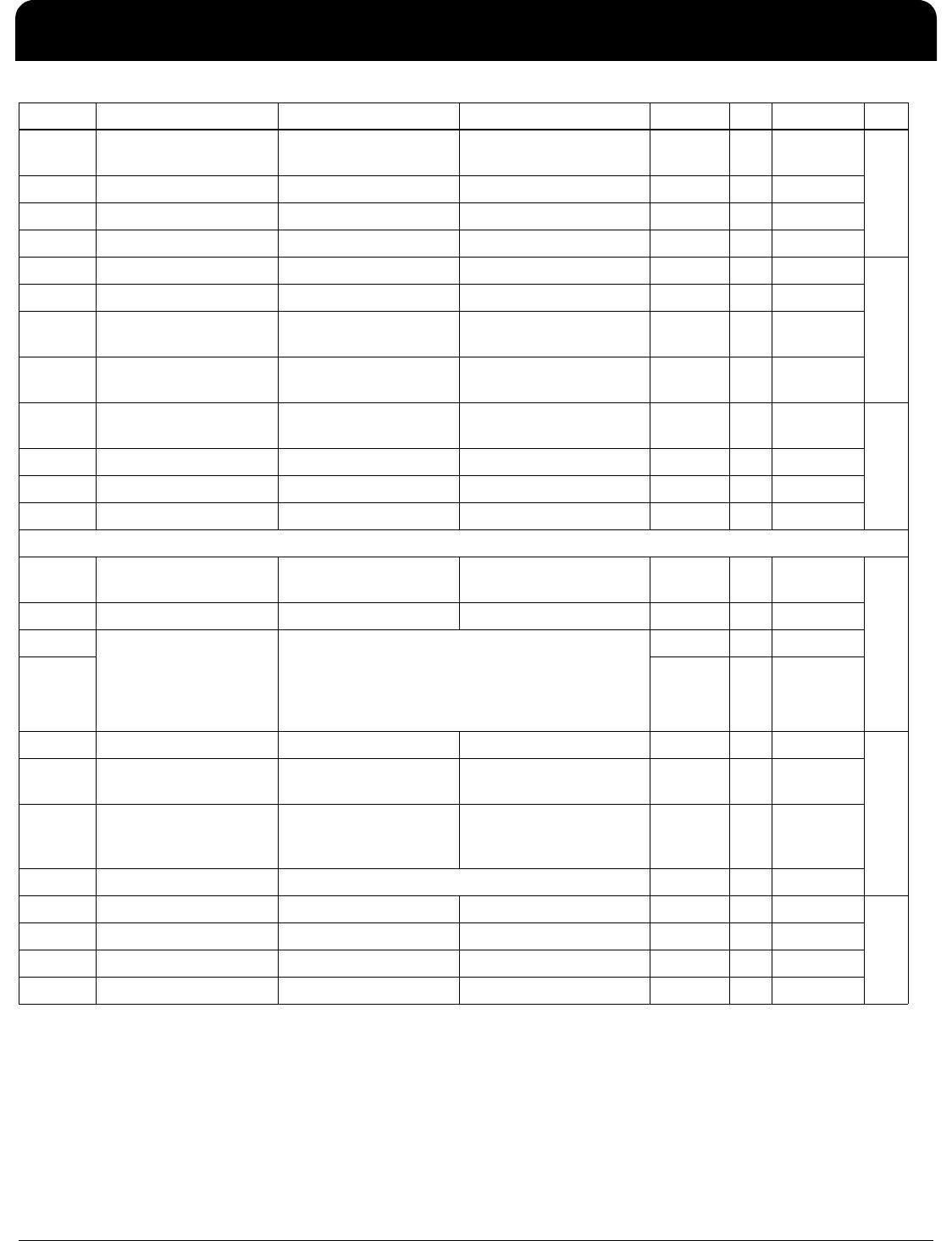

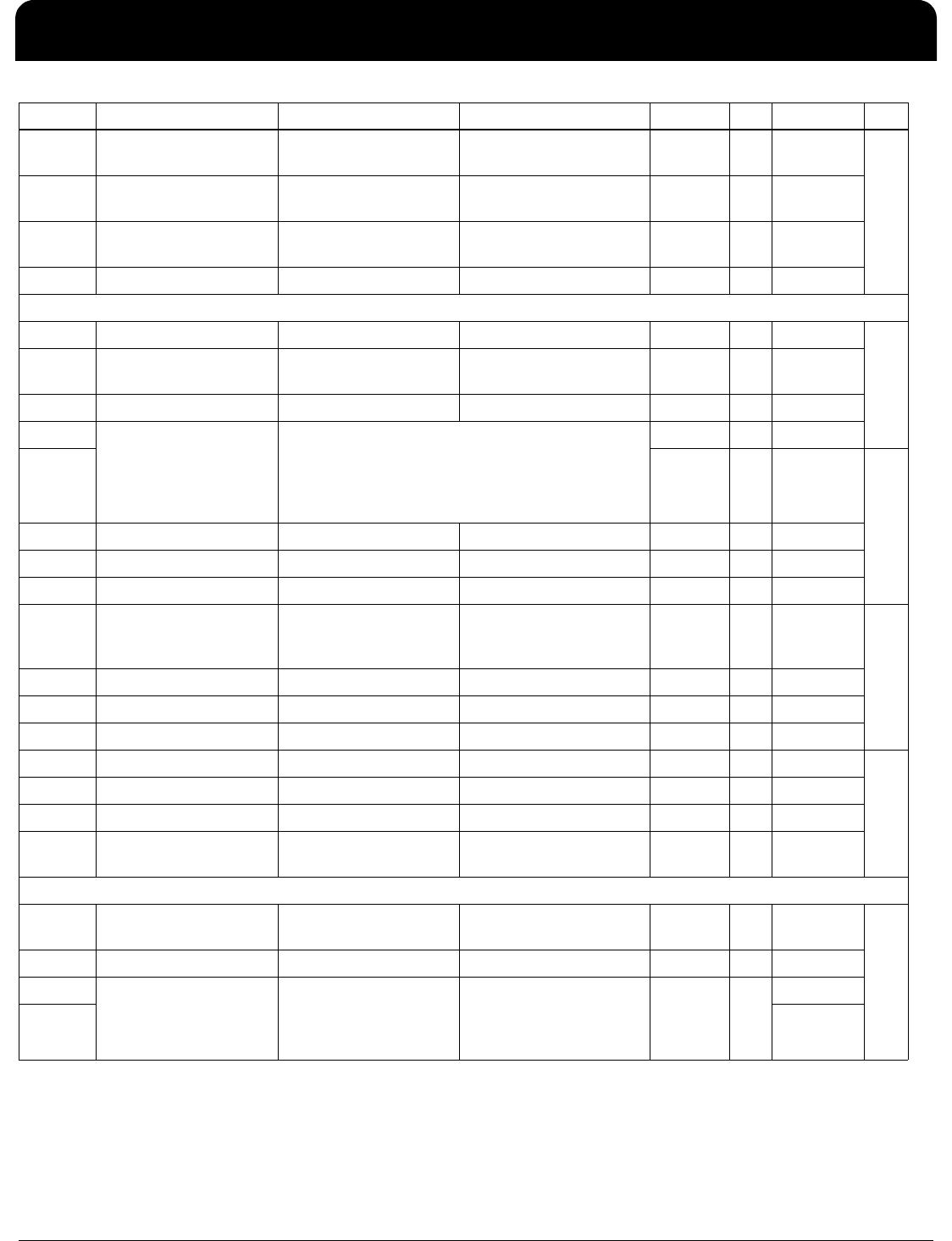

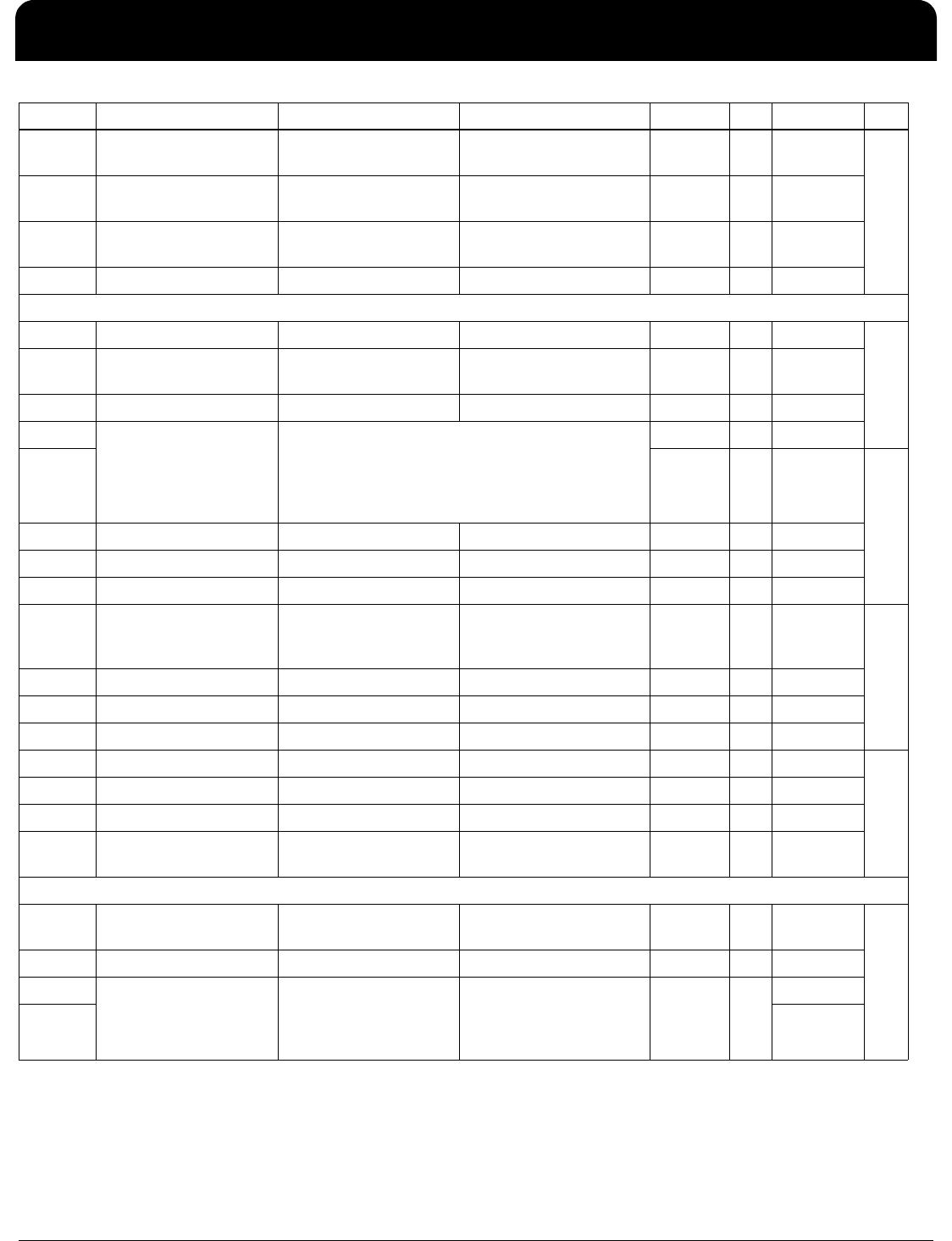

18.3 Auto polarity inhibit Polarity automatically

corrected

Polarity not automatically

corrected

RW – 0 0

18.2 SQE test inhibit Normal SQE test

behavior

SQE test disabled RW – 0

18.1 Link Loss inhibit Normal Link Loss

behavior

Link Always = Link Pass RW – 0

18.0 Squelch inhibit Normal squelch behavior No squelch RW – 0

Register 19 - Extended Control Register

19.15 Node Mode Node mode Repeater mode RW – L –

19.14 Hardware/Software

Mode Speed Select

Use bit00.13 to select

speed

Use real time input pin 22

only to select speed

RW – L

19.13 Remote Fault No faults detected Remote fault detected RO – 0

19.12 Register Bank select [01]=Bank1, access register0x00~0x13 and registers

0x14~0x1F

[00]=Bank0, access register0x00~0x13, new defined

registers 0x14~0x25

[1x]=Bank0, same as [00]

RW – 0

19.11 RW – 0 2

19.10 IDT reserved Read unspecified Read unspecified RO – 0

19.9 AMDIX_EN See Table on page 11 See Table on page 11 RW – 1

19.8 MDI_MODE See Table on page 11 See Table on page 11 RW – 0

19.7 Twisted Pair Tri-State

Enable, TPTRI

Twisted Pair Signals are

not Tri-Stated or No

effect

Twisted Pair Signals are

Tri-Stated

RW – 0 0

19.6 ICS reserved Reserved Reserved RW – 0

19.5 ICS reserved Reserved Reserved RW – 0

19.4 ICS reserved Reserved Reserved RW – 0

19.3 ICS reserved Reserved Reserved RW – 0 1

19.2 ICS reserved Reserved Reserved RW – 0

19.1 ICS reserved Reserved Reserved RW – 0

19.0 Automatic 100Base-TX

Power Down

Do not automatically

power down

Power down automatically RW – 1

Register

20 - Extended Control Register

20.15 Str_enhance Normal digital output

strength

Enhance digital output

strength in 1.8V condition

RW 0

3

20.14 Fast-off Disable the function Enable fast-off circuit RW – 0

20.13 LED4 mode 00=Receive data

01=Collision

10=Fullduplex

11=OFF (default LED4)

RW – 1

20.12 1

Bit Definition When Bit = 0 When Bit = 1 Access

2

SF

2

Default

3

Hex