ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 7

ICS1894-40 REV K 022412

If auto-negotiation is not supported or the ICS1894-40 link

partner is forced to bypass auto-negotiation, the

ICS1894-40 sets its operating mode by observing the signal

at its receiver. This is known as parallel detection, and

allows the ICS1894-40 to establish link by listening for a

fixed signal protocol in the absence of auto-negotiation

advertisement protocol.

MII Management (MIIM) Interface

The ICS1894-40 supports the IEEE 802.3 MII Management

Interface, also known as the Management Data Input /

Output (MDIO) Interface. This interface allows upper-layer

devices to monitor and control the state of the ICS1894-40.

An external device with MIIM capability is used to read the

PHY status and/or configure the PHY settings. Additional

details on the MIIM interface can be found in Clause

22.2.4.5 of the IEEE 802.3u Specification.

The MIIM interface consists of the following:

• A physical connection that incorporates the clock line

(MDC) and the data line (MDIO).

• A specific protocol that operates across the

aforementioned physical connection that allows an

external controller to communicate with one or more

ICS1894-40 devices. Each ICS1894-40 device is

assigned a PHY address that is set by the P[4:0]

strapping pins

• An internal addressable set of thirty-one 8-bit MDIO

registers. Register [0:6] are required, and their functions

are defined by the IEEE 802.3u Specification. The

additional registers are provided for expanded

functionality.

The ICS1894-40 supports MIIM in both MII mode and RMII

mode.

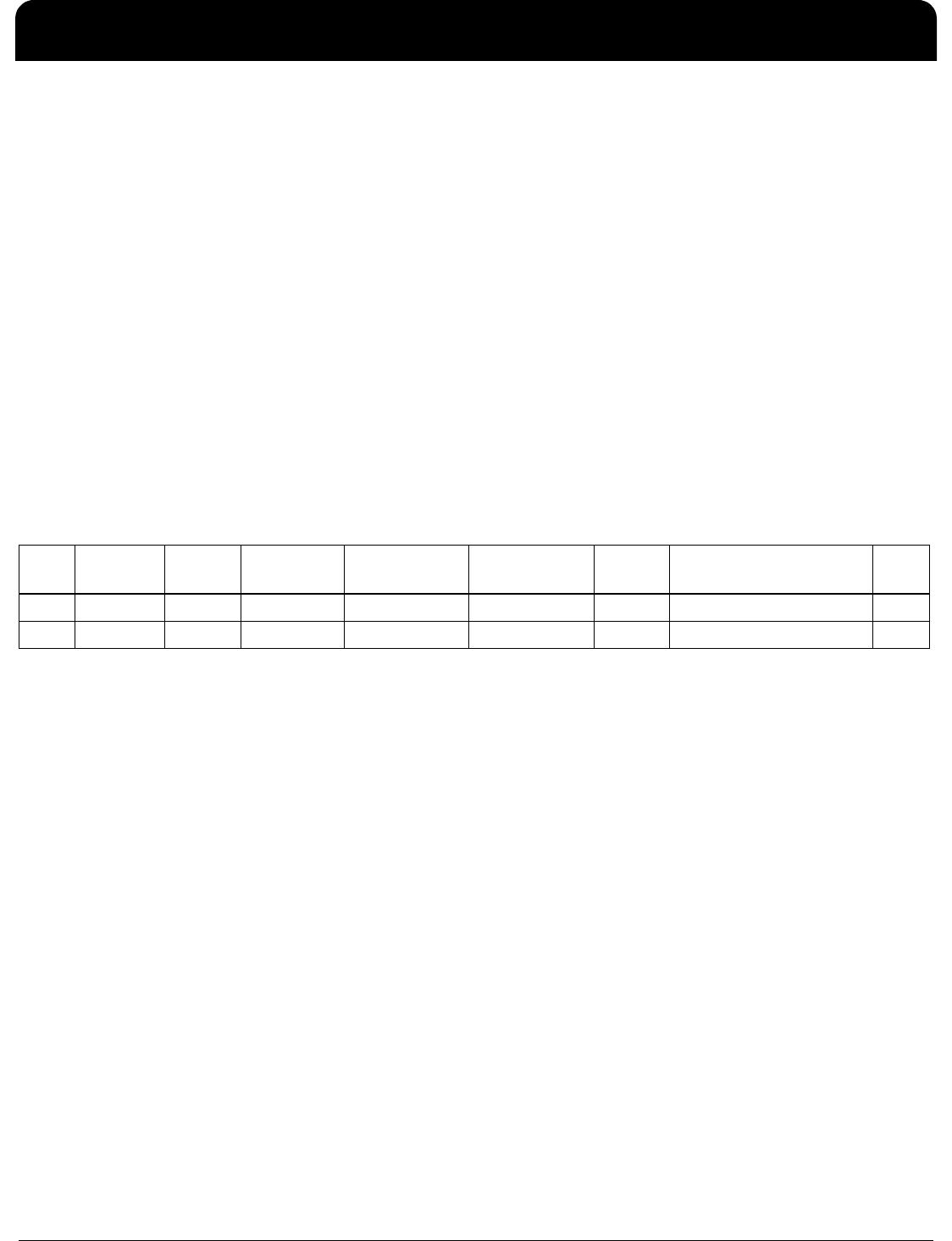

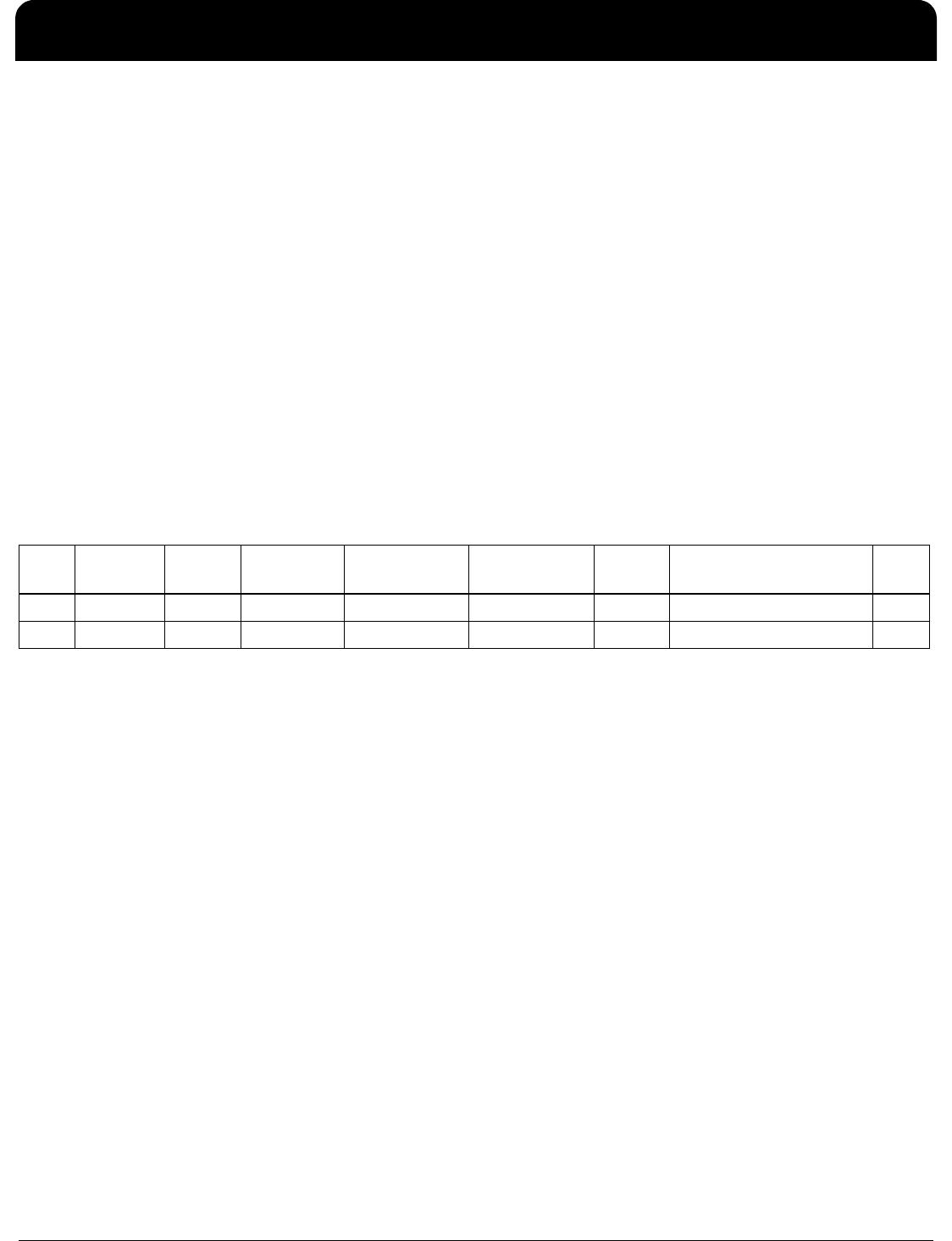

The following table shows the MII Management frame

format for the ICS1894-40.

MII Management Frame Format

Interrupt (INT)

P2/INT (pin 12) is an optional interrupt signal that is used to

inform the external controller that there has been a status

update in the ICS1894-40 PHY register. Register 23 shows

the status of the various interrupts while register 22 controls

the enabling/disabling of the interrupts.

MII Data Interface

The Media Independent Interface (MII) is specified in

Clause 22 of the IEEE 802.3u Specification. It provides a

common interface between physical layer and MAC layer

devices, and has the following key characteristics:

• Supports 10Mbps and 100Mbps data rates.

• Uses a 25MHz reference clock, sourced by the PHY.

• Provides independent 4-bit wide (nibble) transmit and

receive data paths.

• Contains two distinct groups of signals: one for

transmission and the other for reception.

The ICS1894-40 is configured for MII mode upon power-up

or hardware reset with the following:

• A 25MHz crystal connected to REFIN, REFOUT (pins 7,

36), or an external 25MHz clock source (oscillator)

connected to REFIN

Preamble Start of

Frame

Read/Write

OP Code

PHY Address

Bits [4:0]

REG Address

Bits [4:0]

TA Data Bits

[15:0]

Idle

Read 32 1’s 01 10 1AAAA RRRRR Z0 DDDDDDDD_DDDDDDDD Z

Write 32 1’s 01 01 00AAA RRRRR 10 DDDDDDDD_DDDDDDDD Z