ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 28

ICS1894-40 REV K 022412

Note 1: Ignored if Auto negotiation is enabled.

Note 2: CW = Command Override Write

LH = Latching High

LL = Latching Low

LMX = Latching Maximum

RO = Read Only

RW = Read/Write

RW/0 = Read/Write Zero

RW/1 = Read/Write One

SC = Self-clearing

SF = Special Functions

Note 3: L = Latched on power-up/hardware reset

† As per the IEEE Std 802.3u, during any write operation to any bit in this register, the STA must write the default value to all Reserved bits.

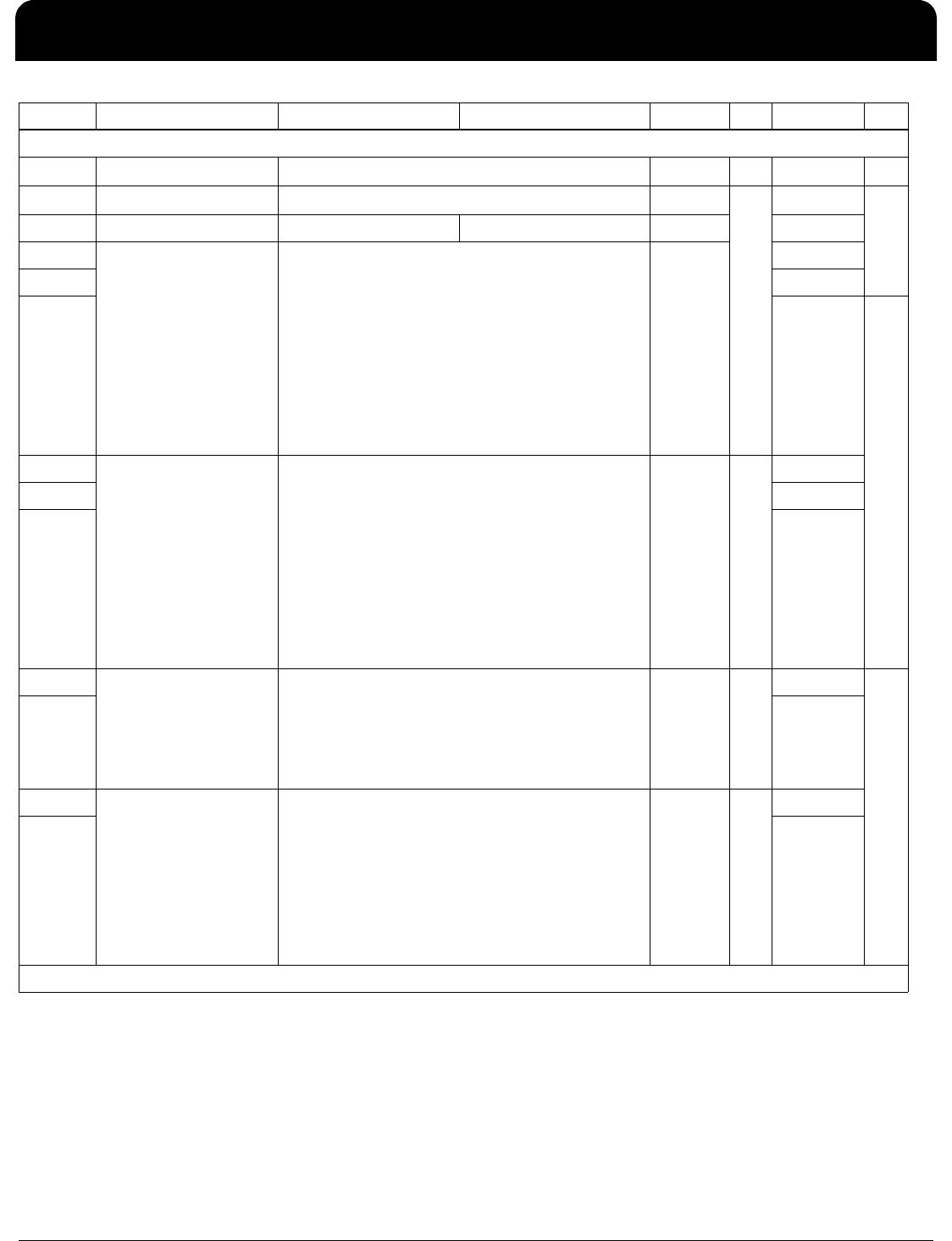

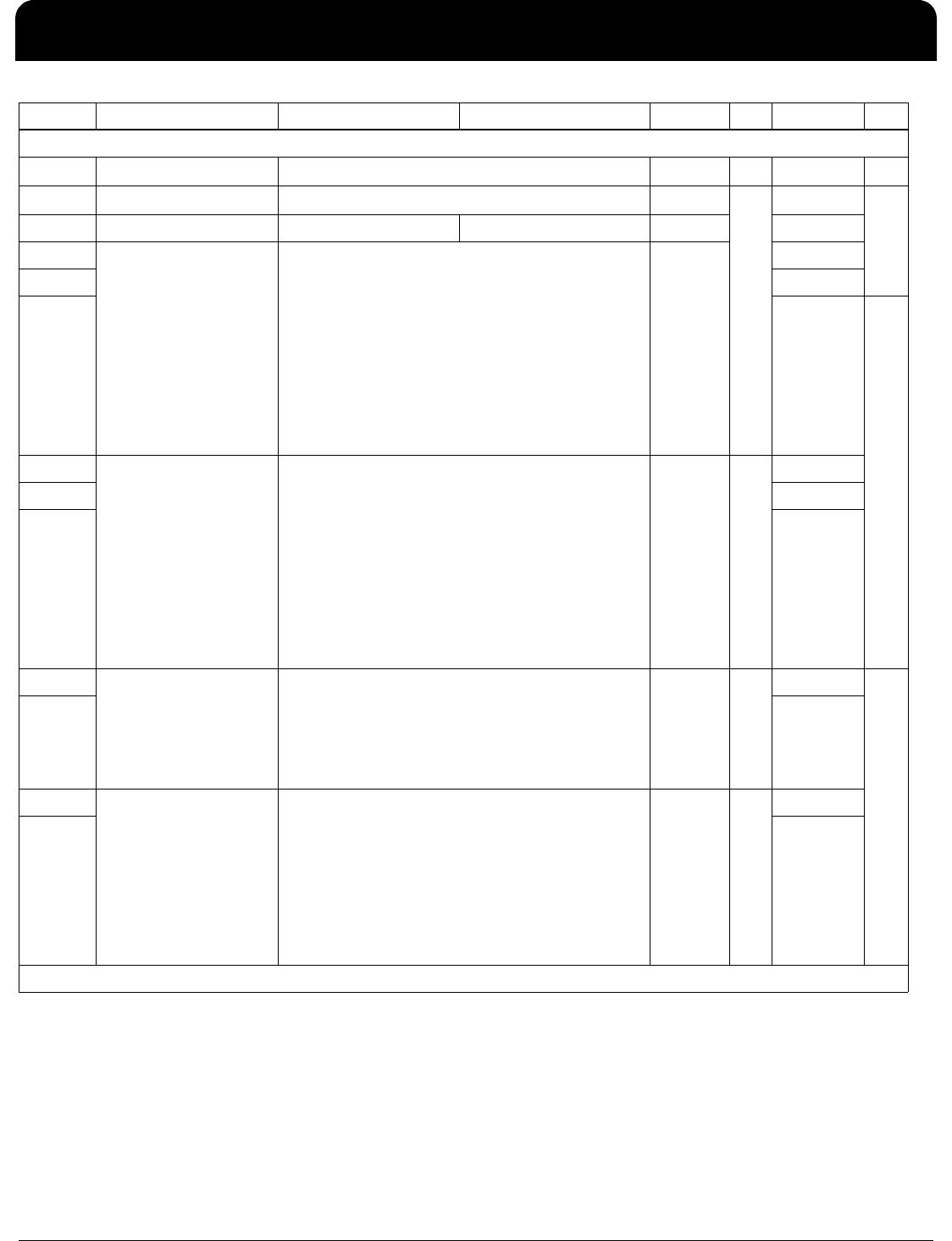

Register 25 - Extended Control Register

25.15:12 Reserved

Reserved

RW 0 0

25.11 Reserved

Reserved

RW 0 6

25.10 Add_Bias Disable Enable RW 1

25.9 TX10BIAS_SET The normal output current of the Bias block for

10BaseT is 540uA. Changing the register can modify

the current with a step size of 5%

000: output 80% current

001: output 85% current

010: output 90% current

011: output 95% current

100: output 100% current

101: output 105% current

110: output 110% current

111: output 115% current

RW 1

25.8 0

25.7 04

25.6 TX100BIAS_SET The normal output current of the Bias block for

100BaseTX is 180uA. Changing the register can

modify the current with a step size of 5%

000: output 80% current

001: output 85% current

010: output 90% current

011: output 95% current

100: output 100% current

101: output 105% current

110: output 110% current

111: output 115% current

RW 1

25.5 0

25.4 0

25.3 OUTDLY_CTL This register controls the delay time of the digital

control signal for xmit_dac.

00: Longest delay time (same as original design)

01: Long delay time

10: Short delay time

11: Shortest delay time

RW 0 1

25.2

25.1 RX_SET The output current of Bias block for RX block is

108µA. The register can change the current with a

step about 16.5%

00: Output 83.5% current

01: Output 100% current

10: Output 116.5% current

11: Output 133% current

Changing this value may modify the RX block

performance

RW 0

25.0 1

Register

26 - 31 - Extended Control Register (Reserved)

Bit Definition When Bit = 0 When Bit = 1 Access

2

SF

2

Default

3

Hex