ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 33

ICS1894-40 REV K 022412

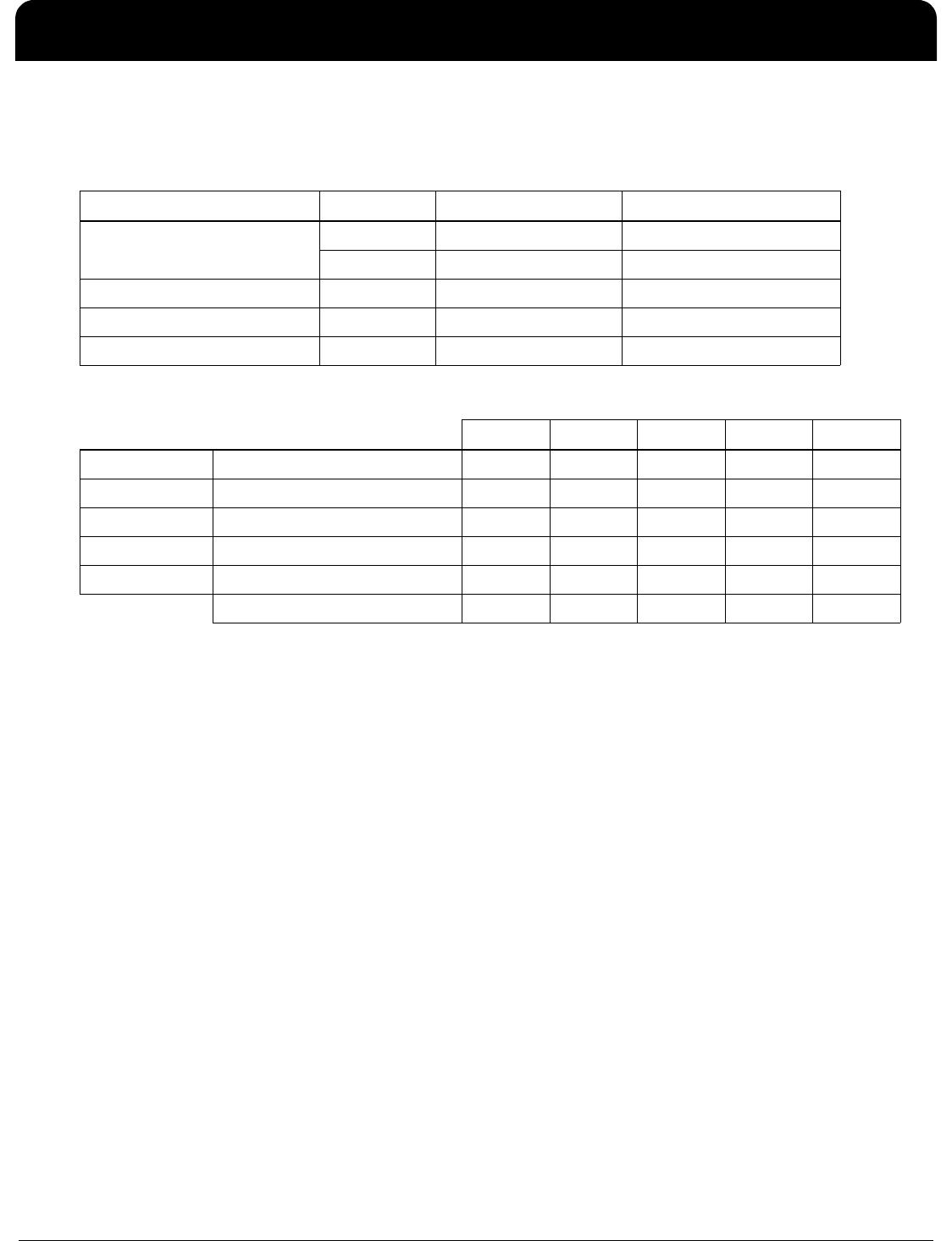

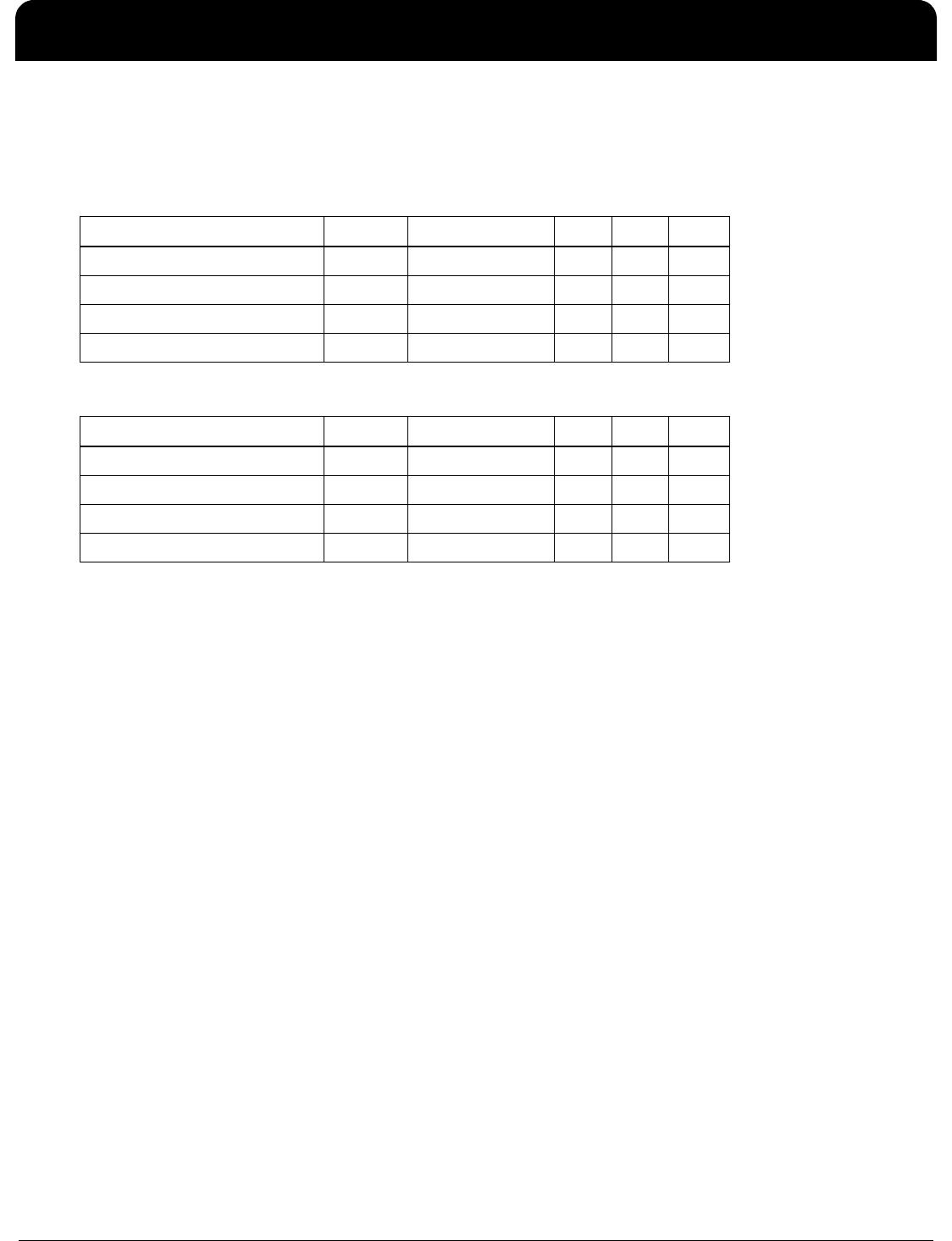

DC Operating Characteristics for REF_IN

The table below lists the 3.3V DC characteristics for the REF_IN pin.

DC Operating Characteristics for MII Pins

The table below lists DC operating characteristics for the Media Independent Interface (MII) for the ICS1894-40.

Timing Diagrams

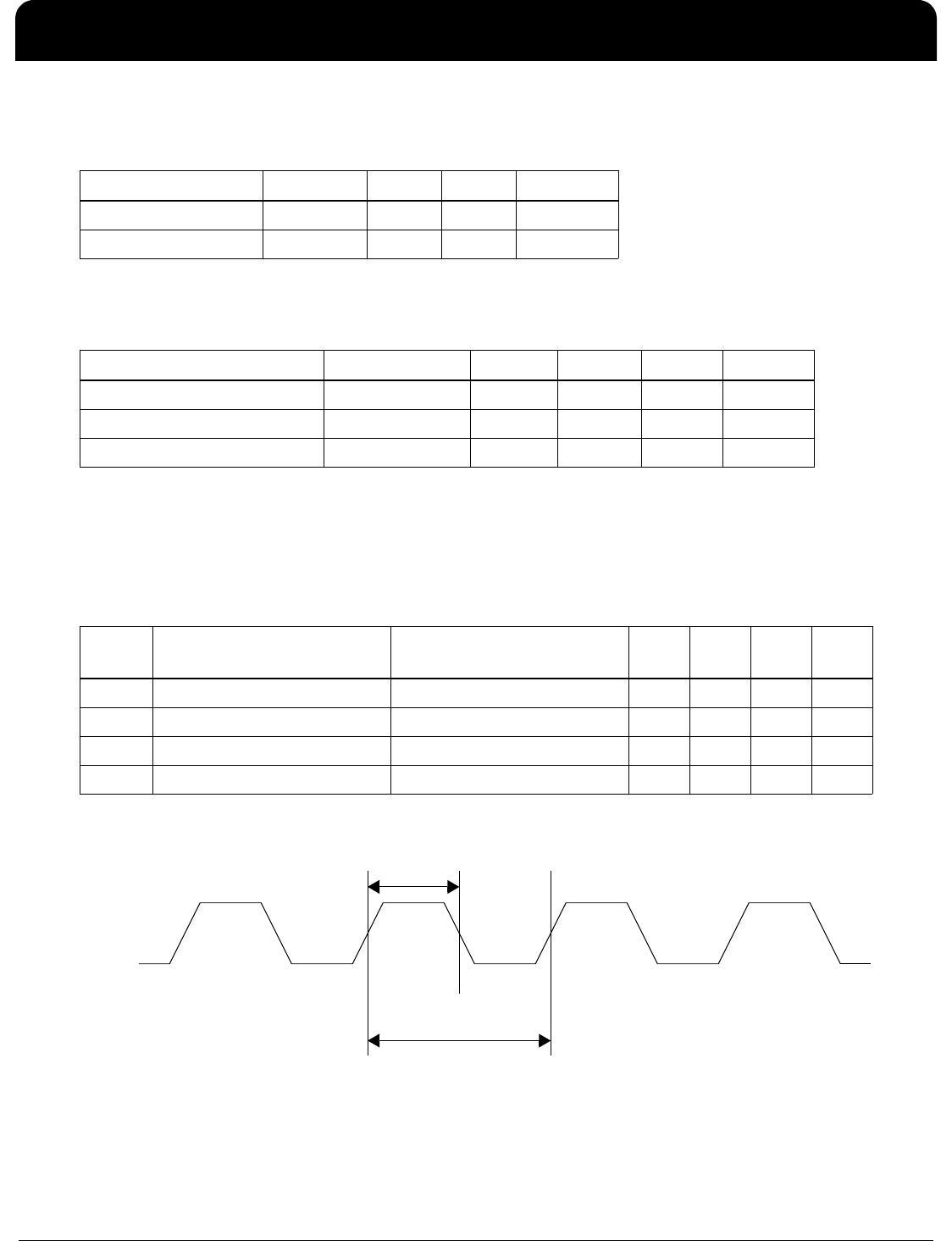

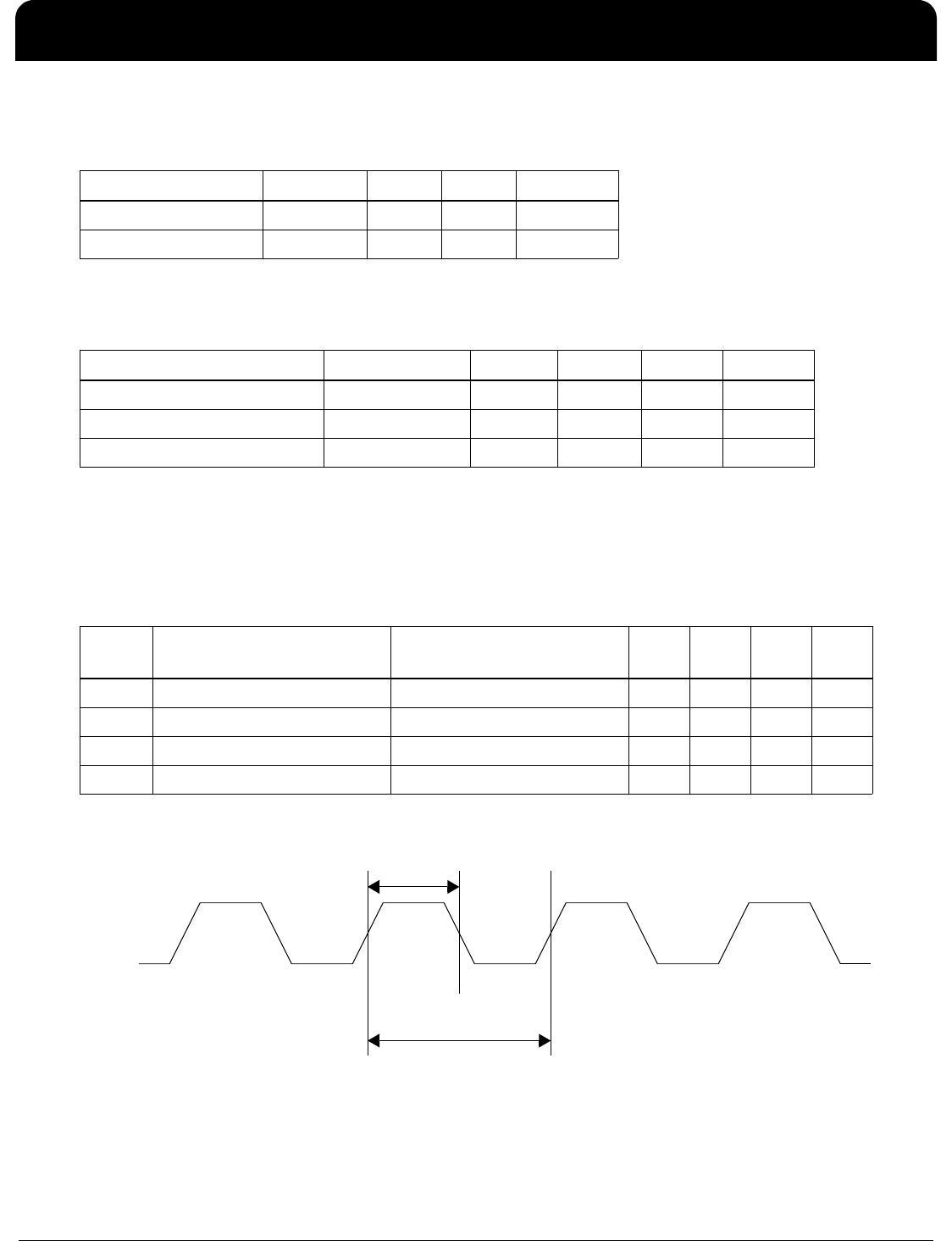

Timing for Clock Reference (REF_IN) Pin

The table below lists the significant time periods for signals on the clock reference (REF_IN) pin. The REF_IN

Timing Diagram figure shows the timing diagram for the time periods.

REF_IN Timing Diagram

Parameter Symbol Min. Max. Units

Input High Voltage V

IH

2.97 – V

Input Low Voltage V

IL

–0.33 V

Parameter Conditions Min. Typ. Max. Units

MII Input Pin Capacitance – – – 8 pF

MII Output Pin Capacitance – – – 14 pF

MII Output Drive Impedance VDDIO = 3.3V – 20 – Ω

Time

Period

Parameter Conditions Min. Typ. Max. Units

t1 REF_IN Duty Cycle (MII) – 45 50 55 %

t2 REF_IN Period (MII) – – 40 – ns

t1 REF_IN Duty Cycle (RMII) – 45 50 55 %

t2 REF_IN Period (RMII) – – 20 – ns