ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 17

ICS1894-40 REV K 022412

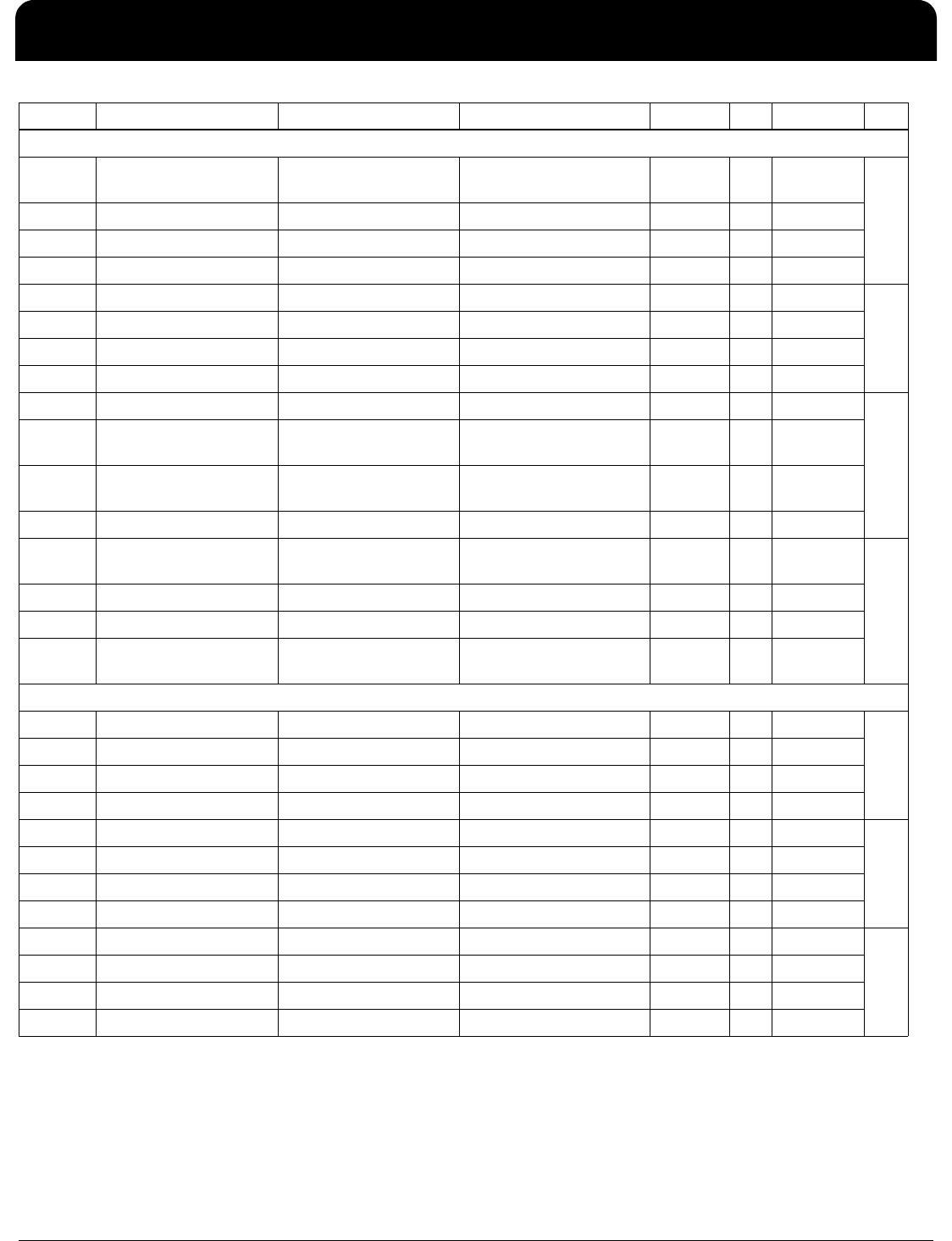

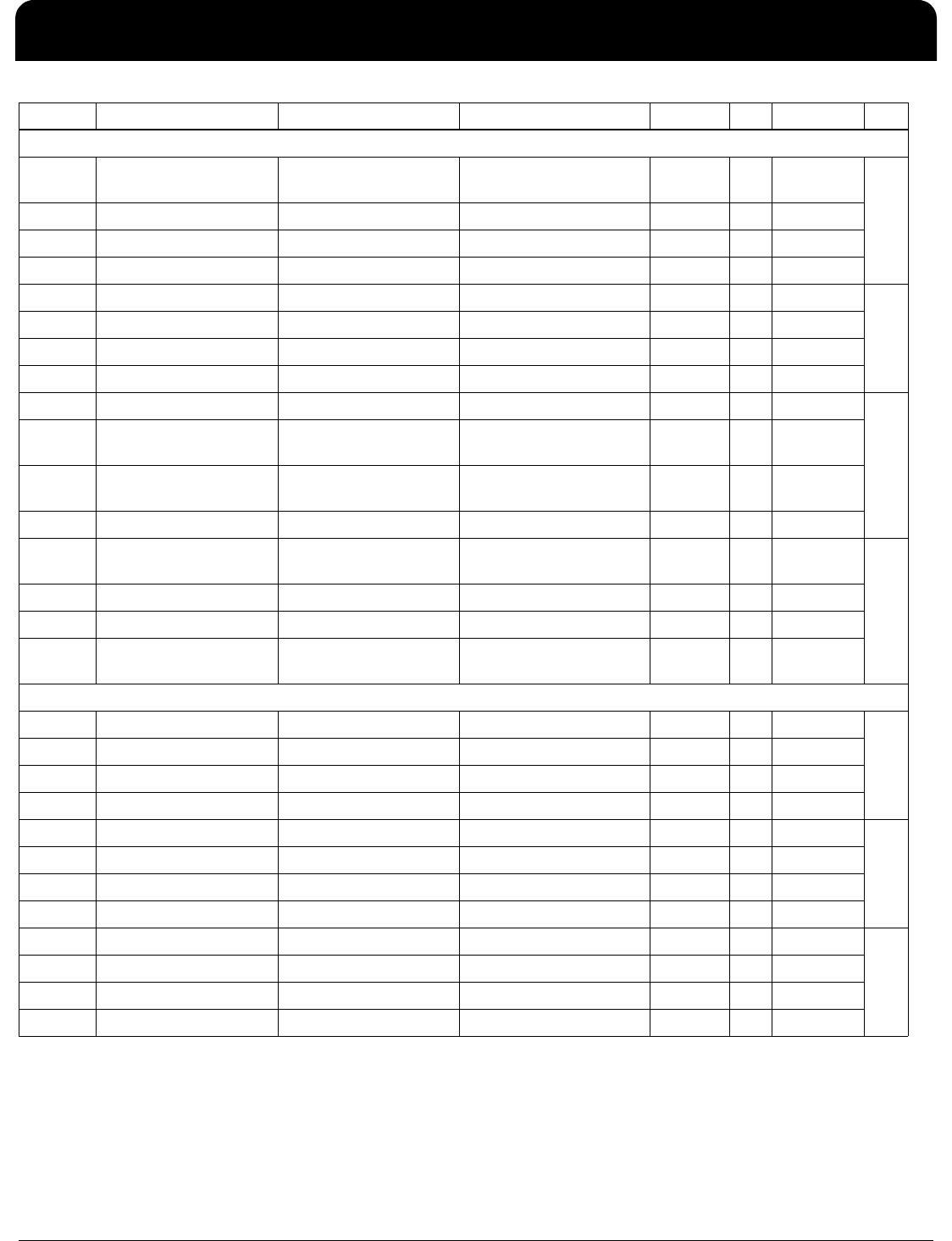

Register 1 - Control

1.15 100Base-T4 Always 0. (Not

supported.)

N/A RO – 0 7

1.14 100Base-TX full duplex Mode not supported Mode supported CW – 1

1.13 100Base-TX half duplex Mode not supported Mode supported CW – 1

1.12 10Base-T full duplex Mode not supported Mode supported CW – 1

1.11 10Base-T half duplex Mode not supported Mode supported CW – 1 8

1.10 IEEE reserved Always 0 N/A CW – 0†

1.9 IEEE reserved Always 0 N/A CW – 0†

1.8 IEEE reserved Always 0 N/A CW – 0†

1.7 IEEE reserved Always 0 N/A CW – 0† 0

1.6 MF Preamble

suppression

PHY requires MF

Preambles

PHY does not require MF

Preambles

RO – 0

1.5 Auto-Negotiation

complete

Auto-Negotiation is in

process, if enabled

Auto-Negotiation is

completed

RO LH 0

1.4 Remote fault No remote fault detected Remote fault detected RO LH 0

1.3 Auto-Negotiation ability N/A Always 1: PHY has

Auto-Negotiation ability

RO – 1 9

1.2 Link status Link is invalid/down Link is valid/established RO LL 0

1.1 Jabber detect No jabber condition Jabber condition detected RO LH 0

1.0 Extended capability N/A Always 1: PHY has

extended capabilities

RO – 1

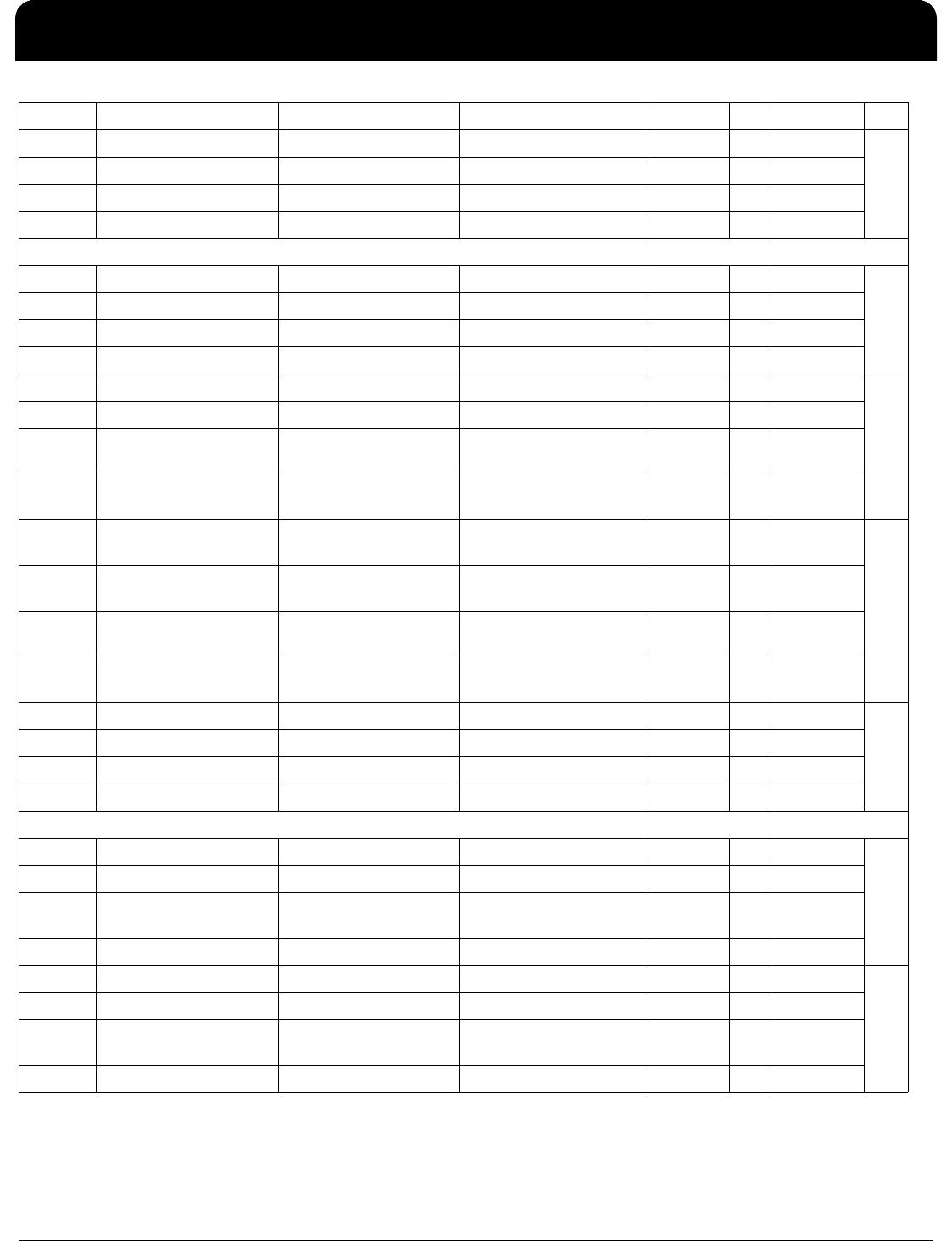

Register 2 - PHY Identifier

2.15 OUI bit 3 | c N/A N/A CW – 0 0

2.14 OUI bit 4 | d N/A N/A CW – 0

2.13 OUI bit 5 | e N/A N/A CW – 0

2.12 OUI bit 6 | f N/A N/A CW – 0

2.11 OUI bit 7 | g N/A N/A CW – 0 0

2.10 OUI bit 8 | h N/A N/A CW – 0

2.9 OUI bit 9 | I N/A N/A CW – 0

2.8 OUI bit 10 | j N/A N/A CW – 0

2.7 OUI bit 11 | k N/A N/A CW – 0 1

2.6 OUI bit 12 | l N/A N/A CW – 0

2.5 OUI bit 13 | m N/A N/A CW – 0

2.4 OUI bit 14 | n N/A N/A CW – 1

Bit Definition When Bit = 0 When Bit = 1 Access

2

SF

2

Default

3

Hex