ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 44

ICS1894-40 REV K 022412

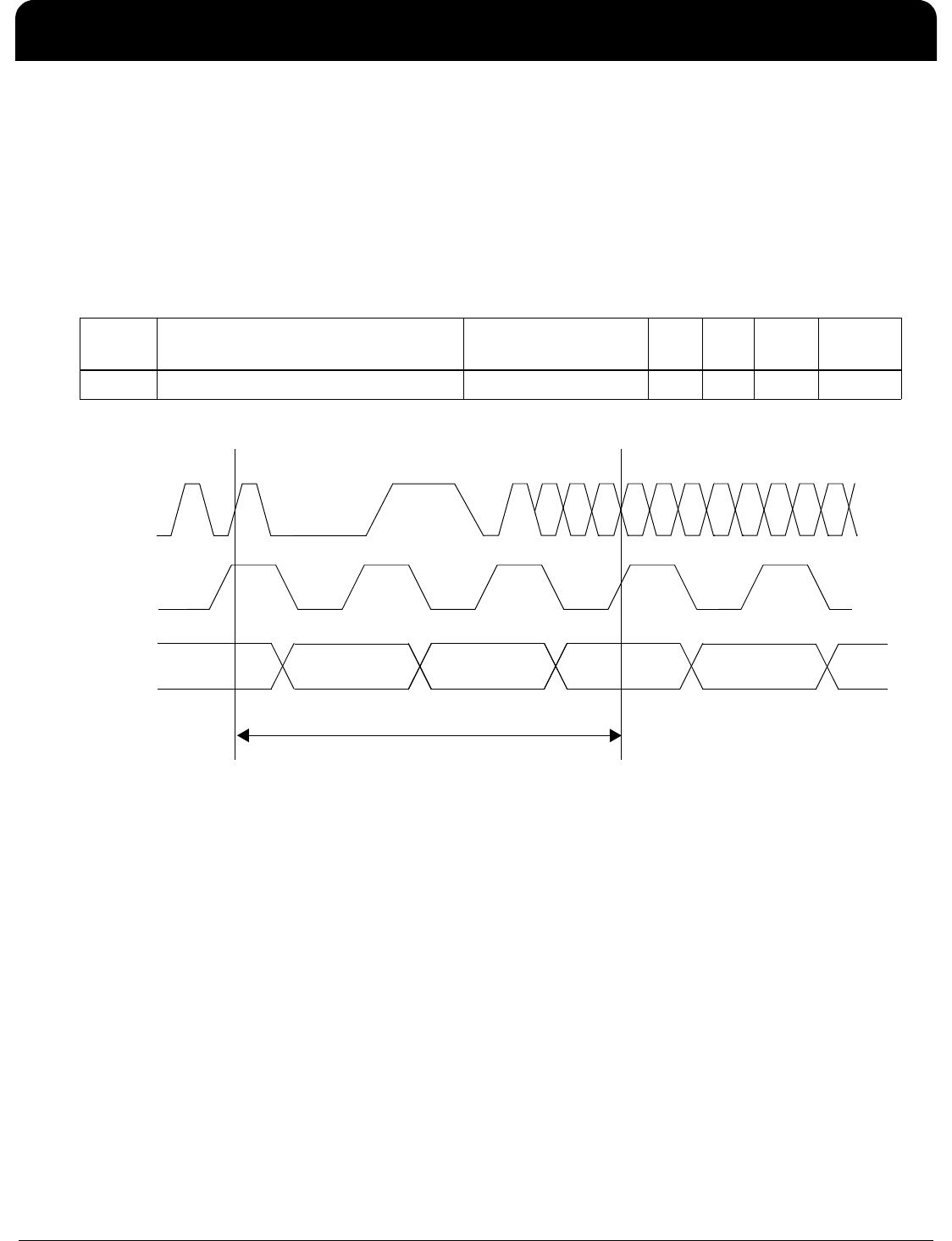

100M Media Independent Interface: Input-to-Carrier Assertion/De-Assertion

The table below lists the significant time periods for the 100M MDI input-to-carrier assertion/de-assertion. The time

periods consist of timings of signals on the following pins:

• TP_RX (that is, TP_RXP and TP_RXN)

• CRS

• COL

The 100M MDI Input to Carrier Assertion/De-Assertion Timing Diagram shows the timing diagram for the time

periods.

† The IEEE maximum is 20 bit times.

‡ The IEEE minimum is 13 bit times, and the maximum is 24 bit times.

100M MDI Input to Carrier Assertion/De-Assertion Timing Diagram

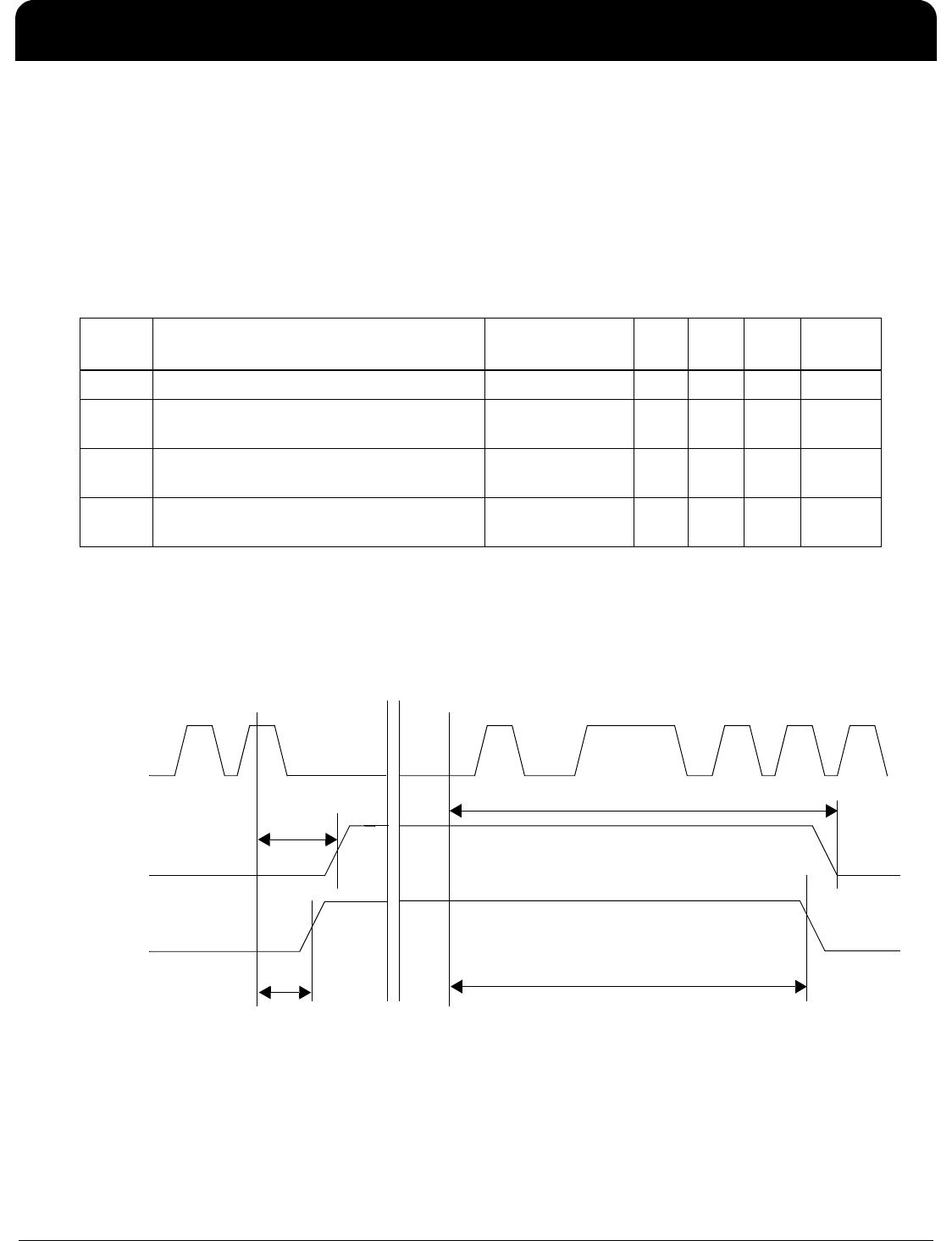

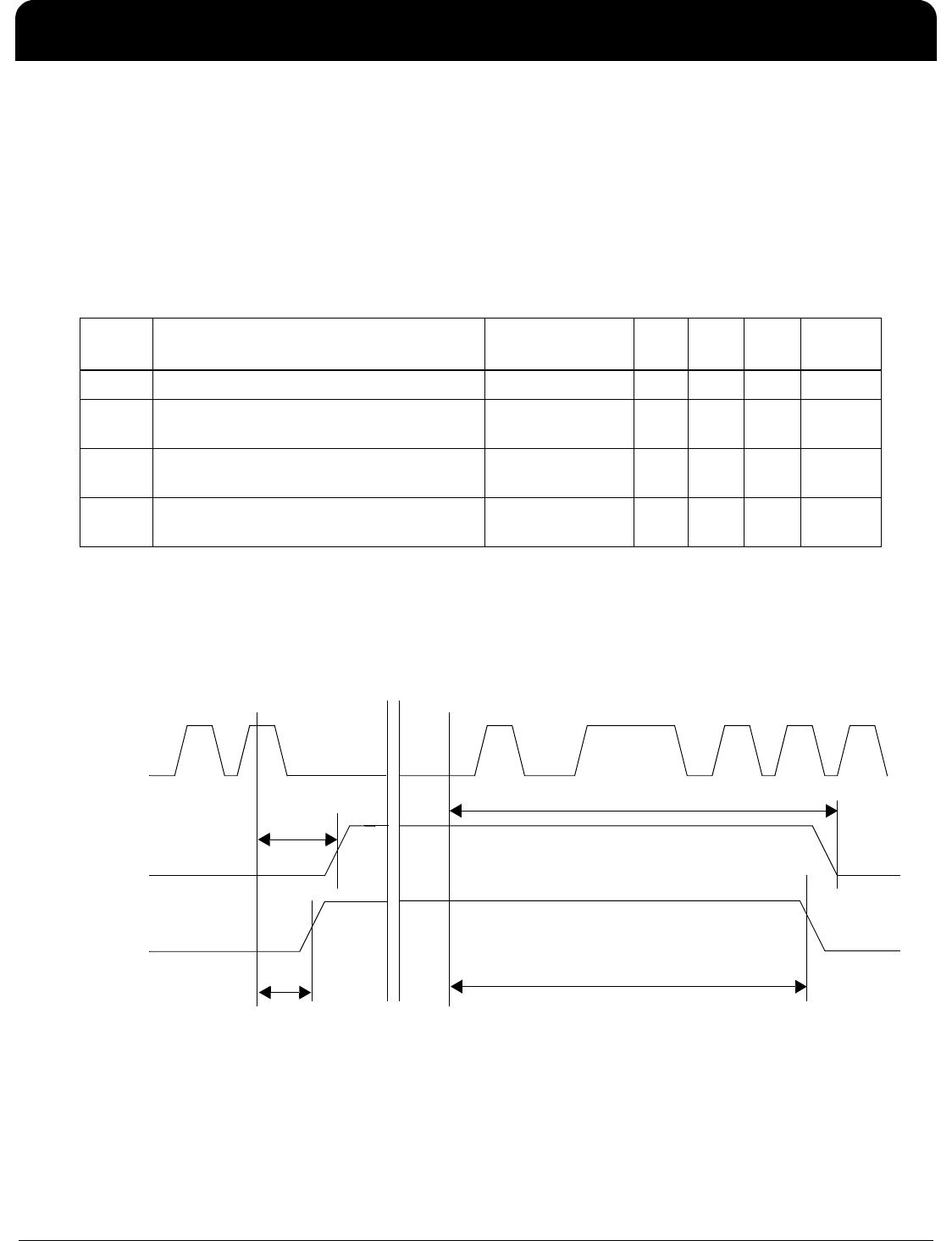

Time

Period

Parameter Conditions Min. Typ. Max. Units

t1 First Bit of /J/ into TP_RX to CRS Assert † – 10 – 14 Bit times

t2 First Bit of /J/ into TP_RX while

Transmitting Data to COL Assert †

Half-Duplex Mode 9 – 13 Bit times

t3 First Bit of /T/ into TP_RX to CRS

De-Assert ‡

–13–18Bit times

t4 First Bit of /T/ Received into TP_RX to

COL De-Assert ‡

Half-Duplex Mode 13 – 18 Bit times

t1

t2

t3

t4

First bit First bit of /T/

†

Shown

unscrambled.

TP_RX

†

CRS

COL