ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 47

ICS1894-40 REV K 022412

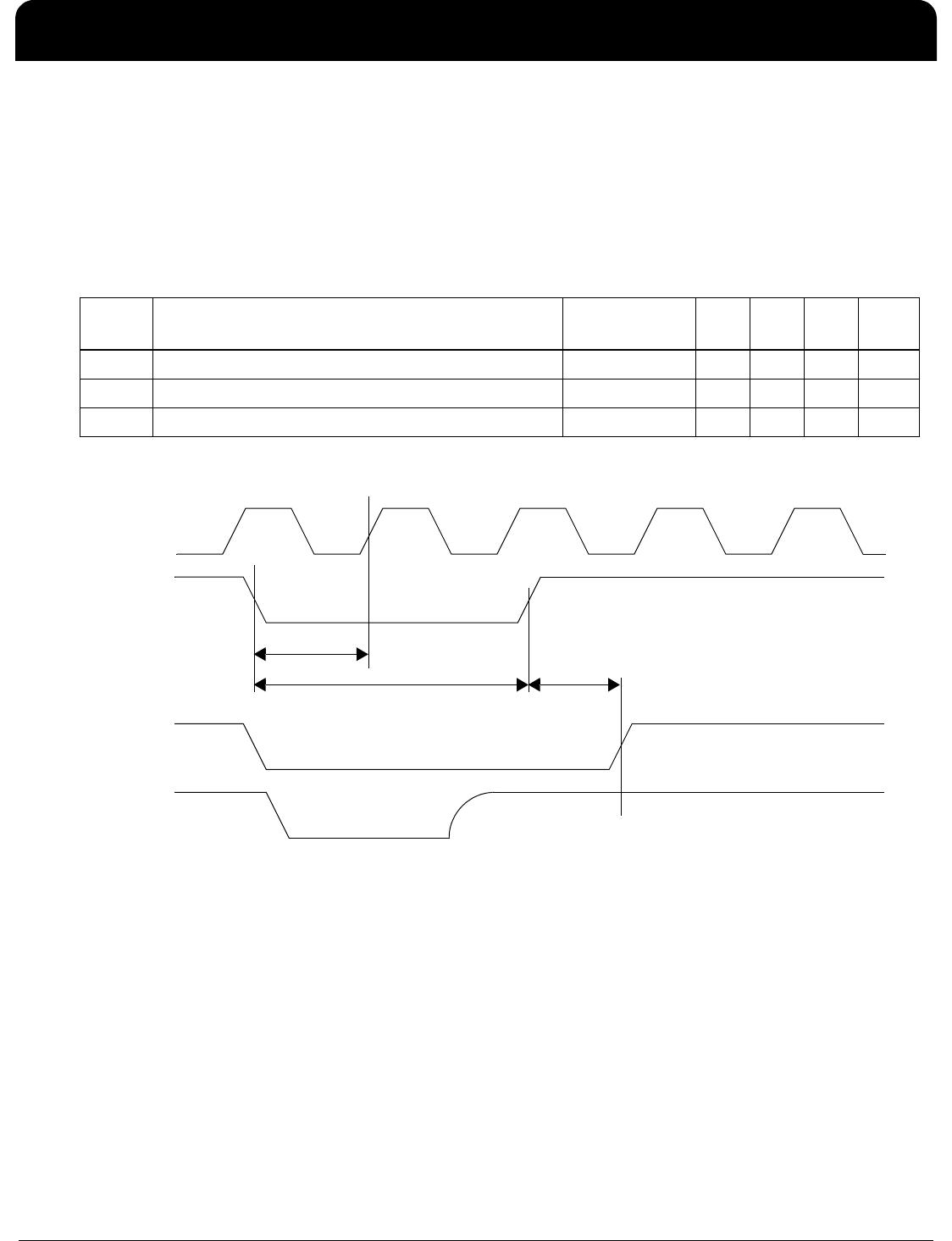

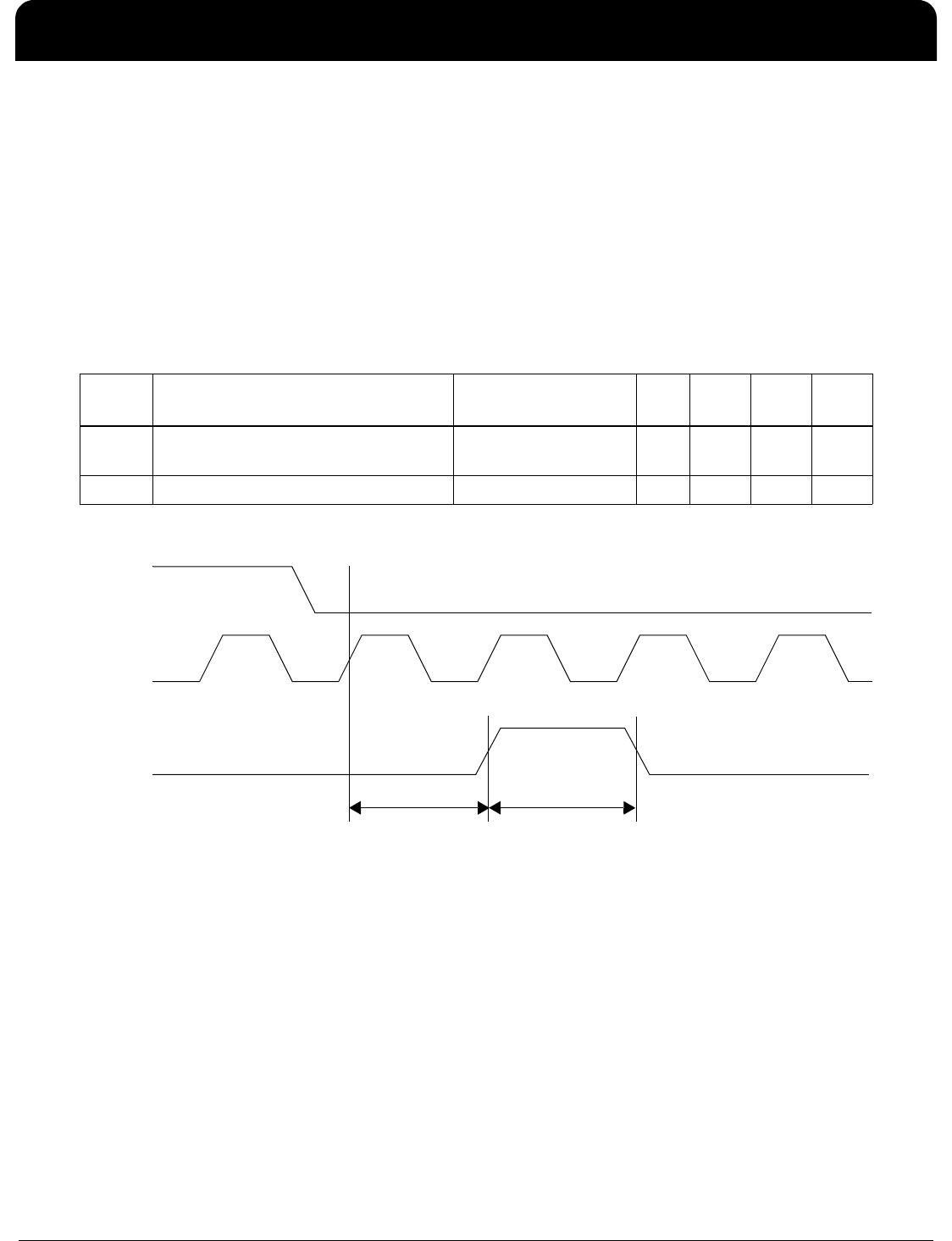

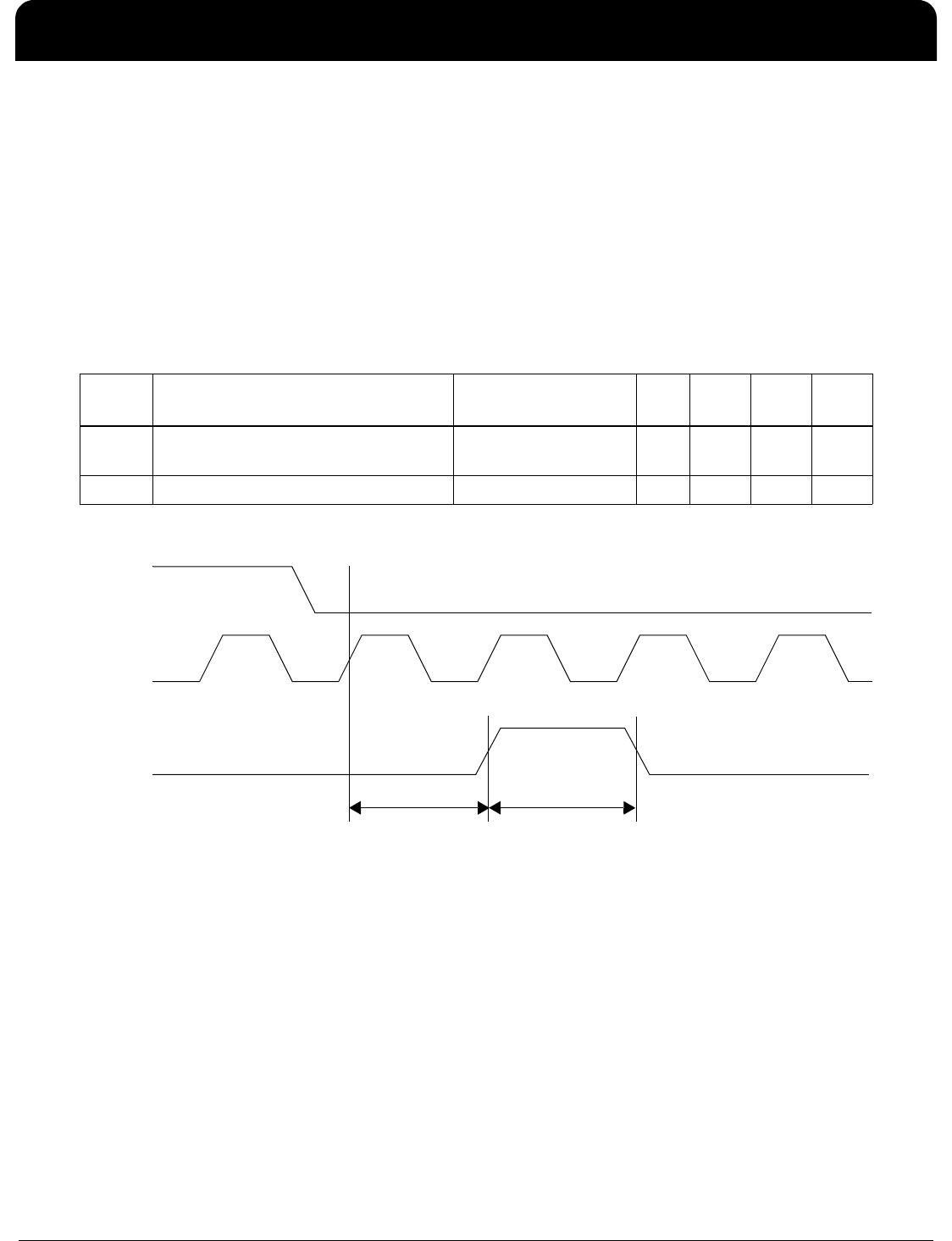

10Base-T: Heartbeat Timing (SQE)

The table below lists the significant time periods for the 10Base-T heartbeat (that is, the Signal Quality Error). The

time periods consist of timings of signals on the following pins:

• TXEN

• TXCLK

• COL

The 10Base-T Heartbeat (SQE) Timing Diagram shows the timing diagram for the time periods.

Note:

1. For more information on 10Base-T SQE operations, see the section “10Base-T Operation: SQE Test”.

2. In 10Base-T mode, one bit time = 100 ns.

10Base-T Heartbeat (SQE) Timing Diagram

Time

Period

Parameter Conditions Min. Typ. Max. Units

t1 COL Heartbeat Assertion Delay from

TXEN De-Assertion

10Base-T Half Duplex – 850 1500 ns

t2 COL Heartbeat Assertion Duration 10Base-T Half Duplex – 1000 1500 ns