ICS1894-40

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE PHYCEIVER

IDT®

10BASE-T/100BASE-TX INTEGRATED PHYCEIVER WITH RMII INTERFACE 26

ICS1894-40 REV K 022412

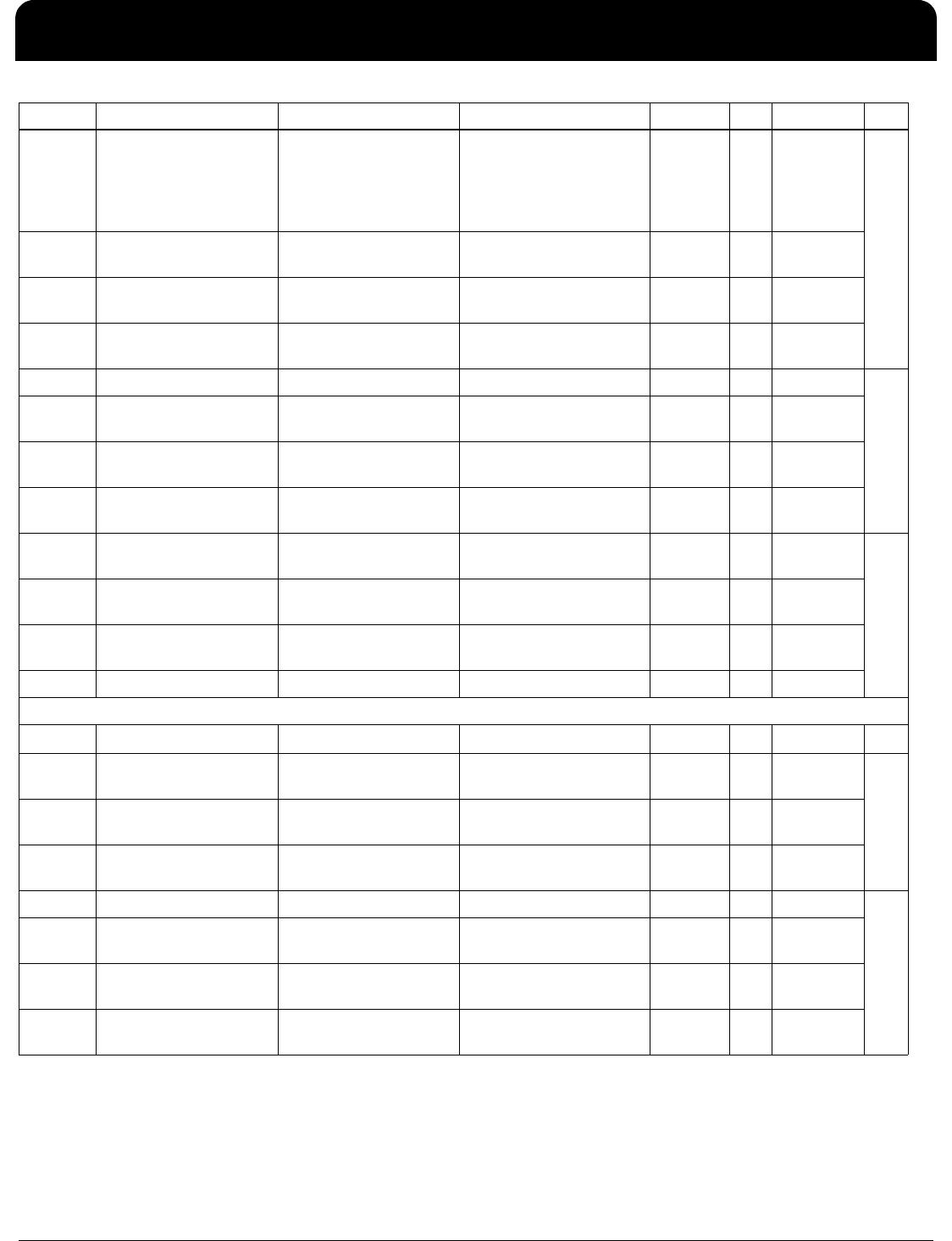

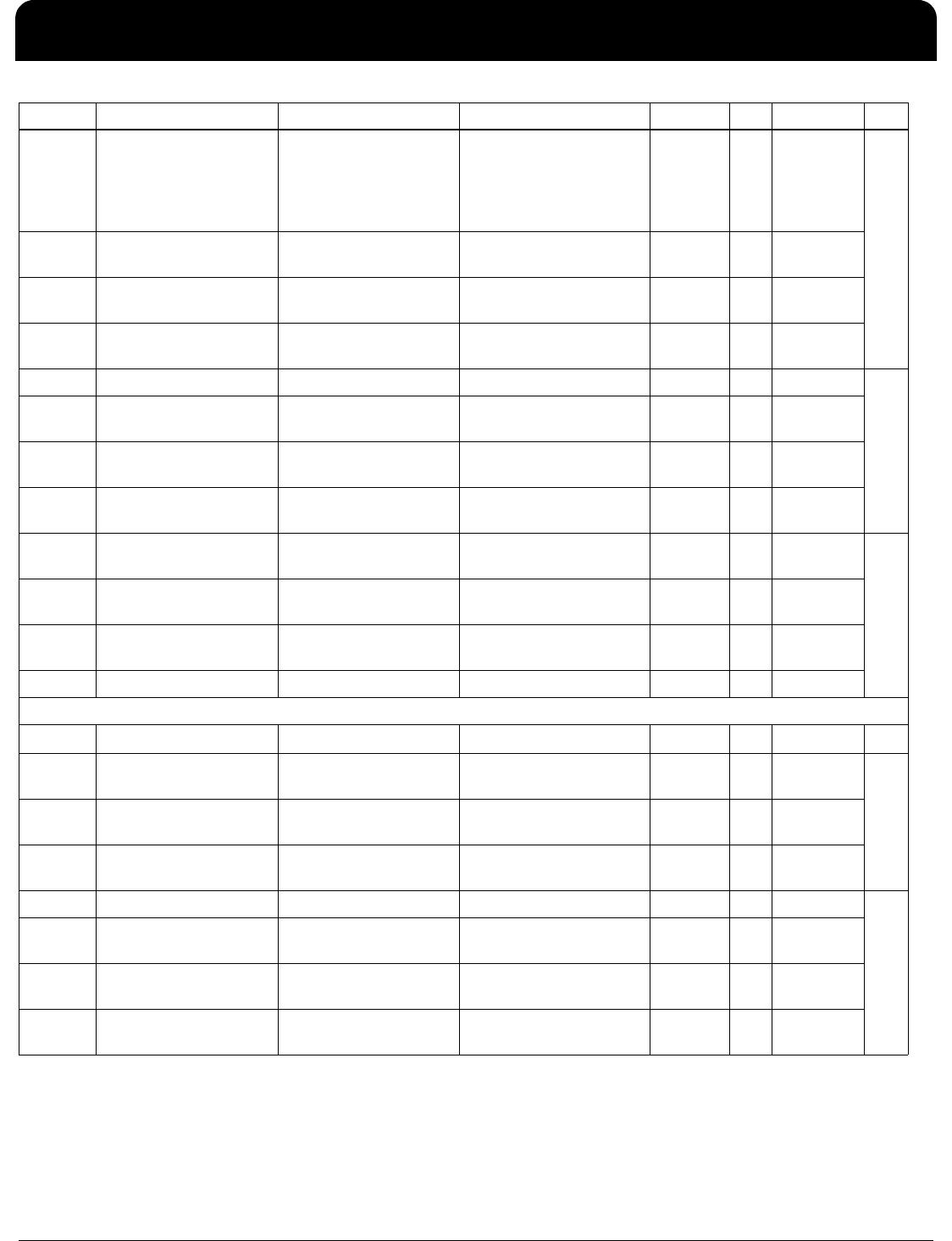

22.11 Interrupt flag re-setup

enable

Interrupt flag always

cleared when write 1 to

flag bit

Interrupt flag remains

unchanged when

interrupt condition exists

when a 1 is written to flag

bit.

RW 0

0

22.10 Interrupt Enable Disable Deep power

down wake up Interrupt

Enable Deep power down

wake up Interrupt

RW 0

22.9 Interrupt Enable Disable Deep power

down Interrupt

Enable Deep power down

Interrupt

RW 0

22.8 Interrupt Enable Disable Auto-Negotiation

Complete Interrupt

Enable Auto-Negotiation

Complete Interrupt

RW 0

22.7 Interrupt Enable Disable Jabber Interrupt Enable Jabber Interrupt RW 0

0

22.6 Interrupt Enable Disable Receive Error

Interrupt

Enable Receive Error

Interrupt

RW 0

22.5 Interrupt Enable Disable Page Received

Interrupt

Enable Page Received

Interrupt

RW 0

22.4 Interrupt Enable Disable Parallel Detect

Fault Interrupt

Enable Parallel Detect

Fault Interrupt

RW 0

22.3 Interrupt Enable Disable Link Partner

Acknowledge Interrupt

Enable Link Partner

Acknowledge Interrupt

RW 0

0

22.2 Interrupt Enable Disable Link Down

Interrupt

Enable Link Down

Interrupt

RW 0

22.1 Interrupt Disable Remote Fault

Interrupt

Enable Remote Fault

Interrupt

RW 0

22.0 Enable Disable Link Up Interrupt Enable Link Up Interrupt RW 0

Register

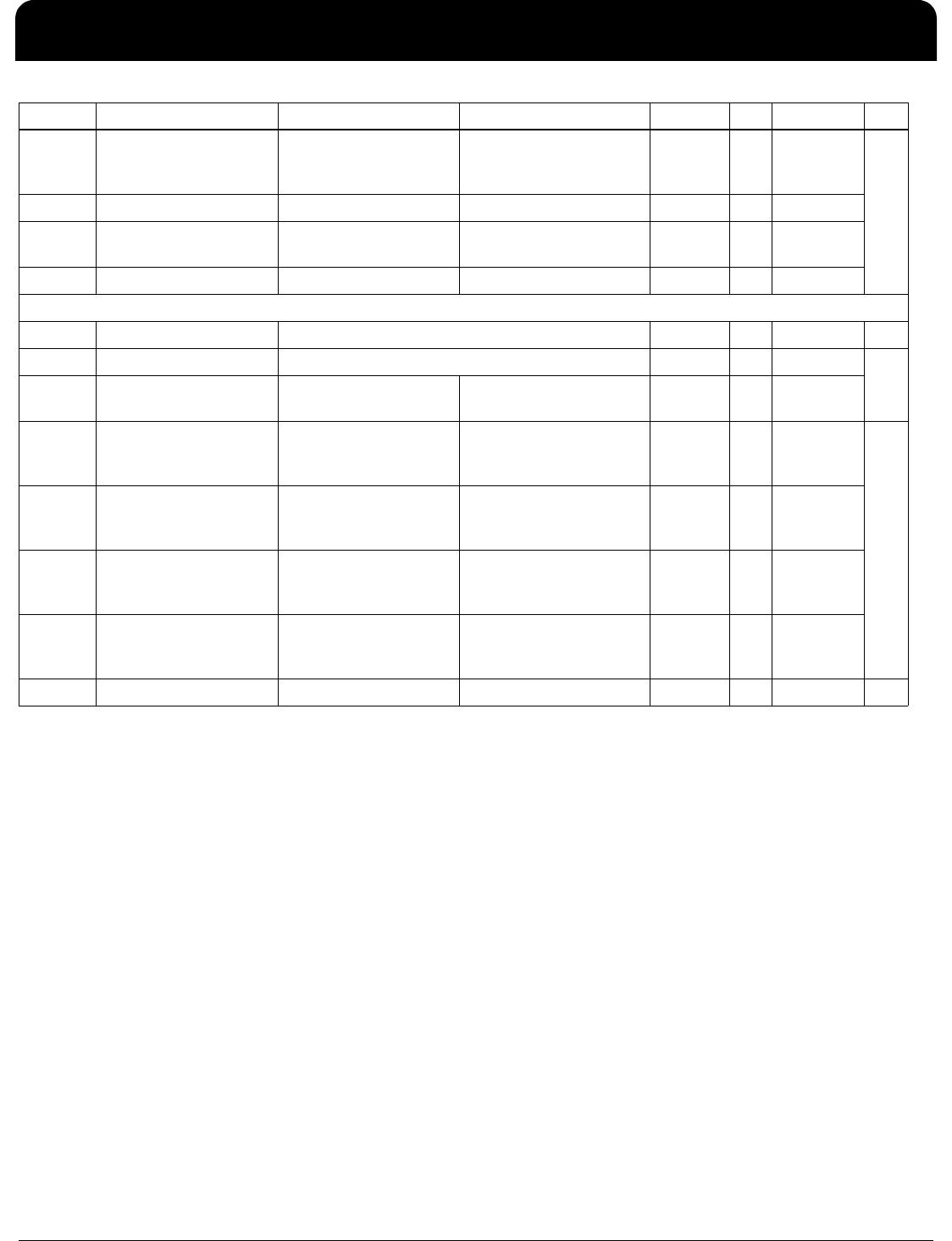

23 - Extended Control Register

23.15:11 Reserved Reserved RO 0

0

23.10 Deep power down wake

up Interrupt

Deep power down wake

up did not occur

Deep power down wake

up occurred

RO/SC 0

0

23.9 Deep power down

Interrupt

Deep power down did

not occur

Deep power down

occurred

RO/SC 0

23.8 Auto-Negotiation

Interrupt

Auto-Negotiation

Complete did not occur

Auto-Negotiation

Complete occurred

RO/SC 0

23.7 Jabber Interrupt Jabber did not occur Jabber occurred RO/SC 0

0

23.6 Receive Error Interrupt Receive Error did not

occur

Receive Error occurred RO/SC 0

23.5 Page Receive Interrupt Page Receive did not

occur

Page Receive occurred RO/SC 0

23.4 Parallel Detect Fault

Interrupt

Parallel Detect Fault did

not occur

Parallel Detect Fault

occurred

RO/SC 0

Bit Definition When Bit = 0 When Bit = 1 Access

2

SF

2

Default

3

Hex