Tsi721 Datasheet 21 April 4, 2016

Integrated Device Technology

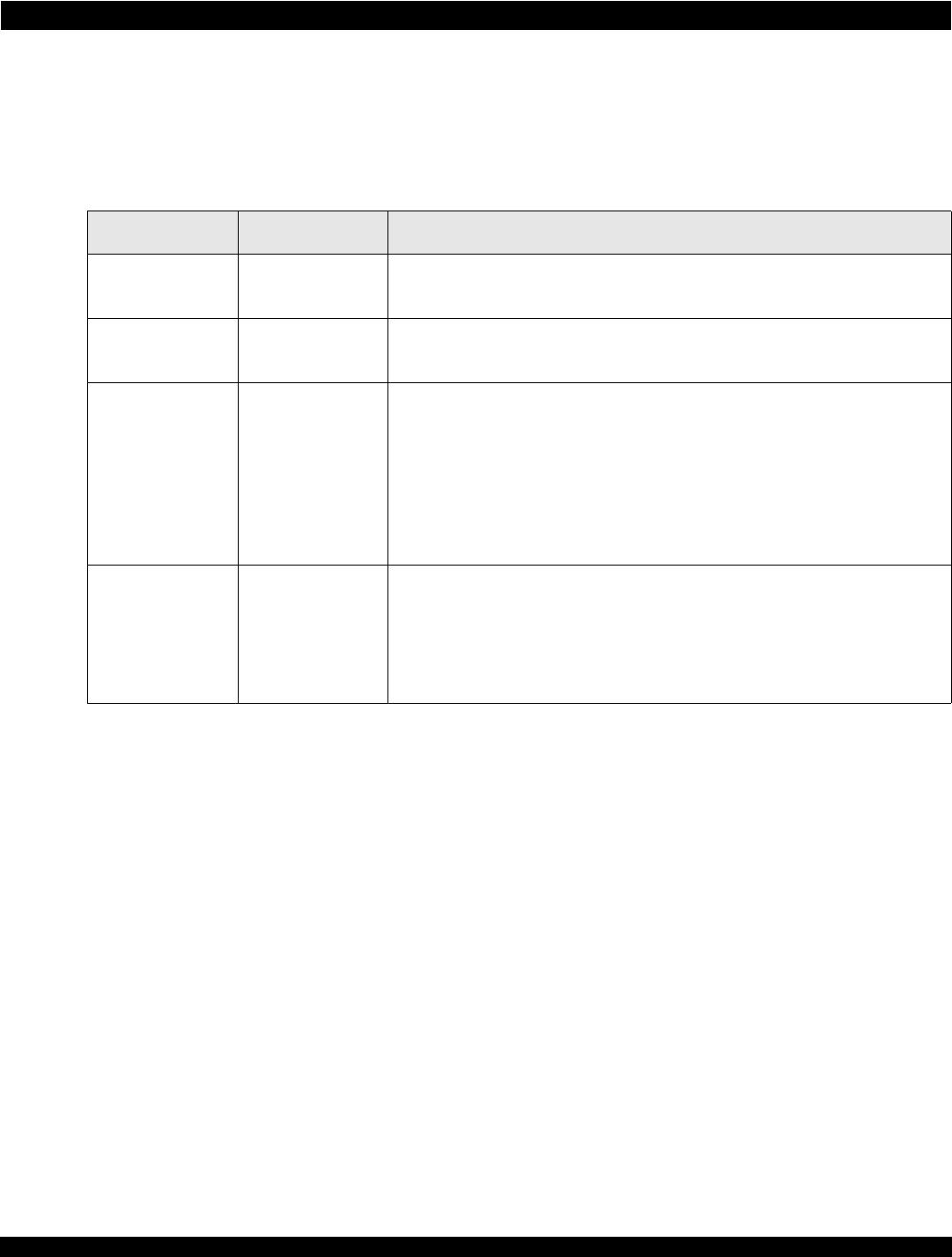

2.7 I2C Signals

The I2C Interface is used for the following:

• As a master, downloading configuration from EEPROM

• As a master, allowing the PCIe root complex or the S-RIO host to configure other I2C expansion devices

• As a slave, exposing internal register space to an I2C master (Note: To be used for lab debug or another master-driven

initialization).

2.8 JTAG and Test Interface Signals

Table 5: I

2

C Signals

Name Pin Type Description

a

a. For information on I2C signals that are used for power-up purposes only, see Power-up Signals.

I2C_SCL IO-OD Serial clock for the I2C Interface with a maximum frequency of 100 kHz.

I2C_SDA IO-OD Serial data for the I2C Interface.

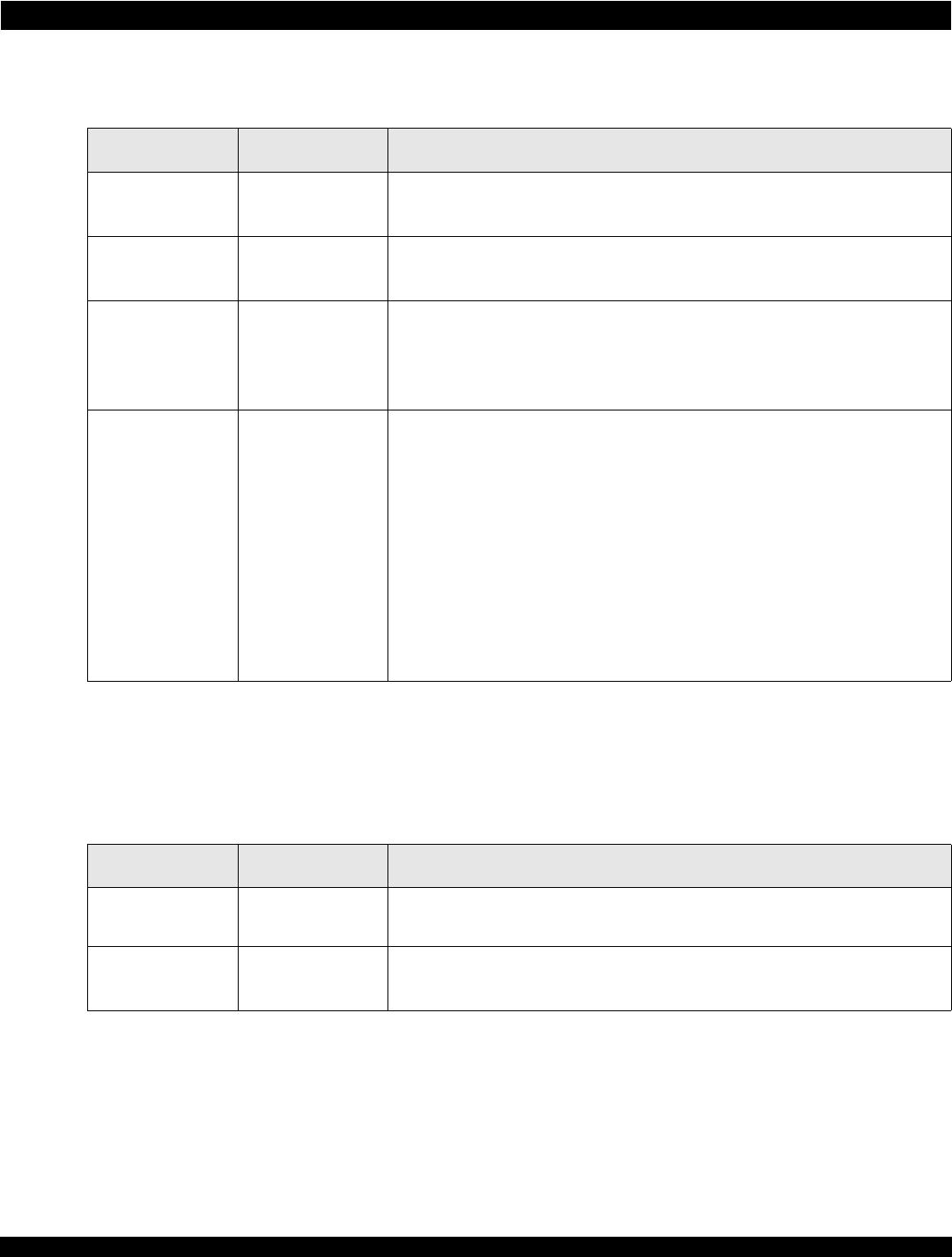

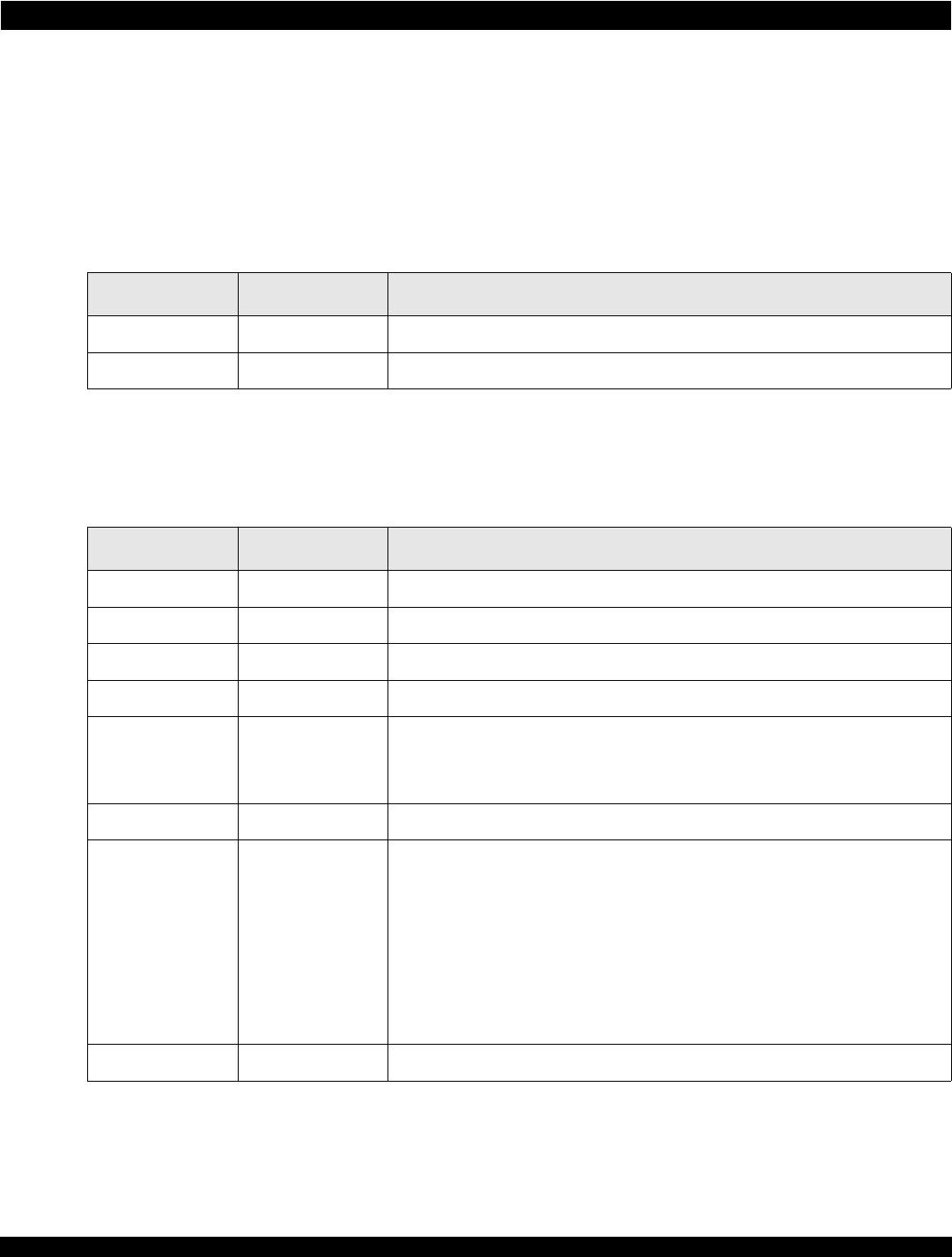

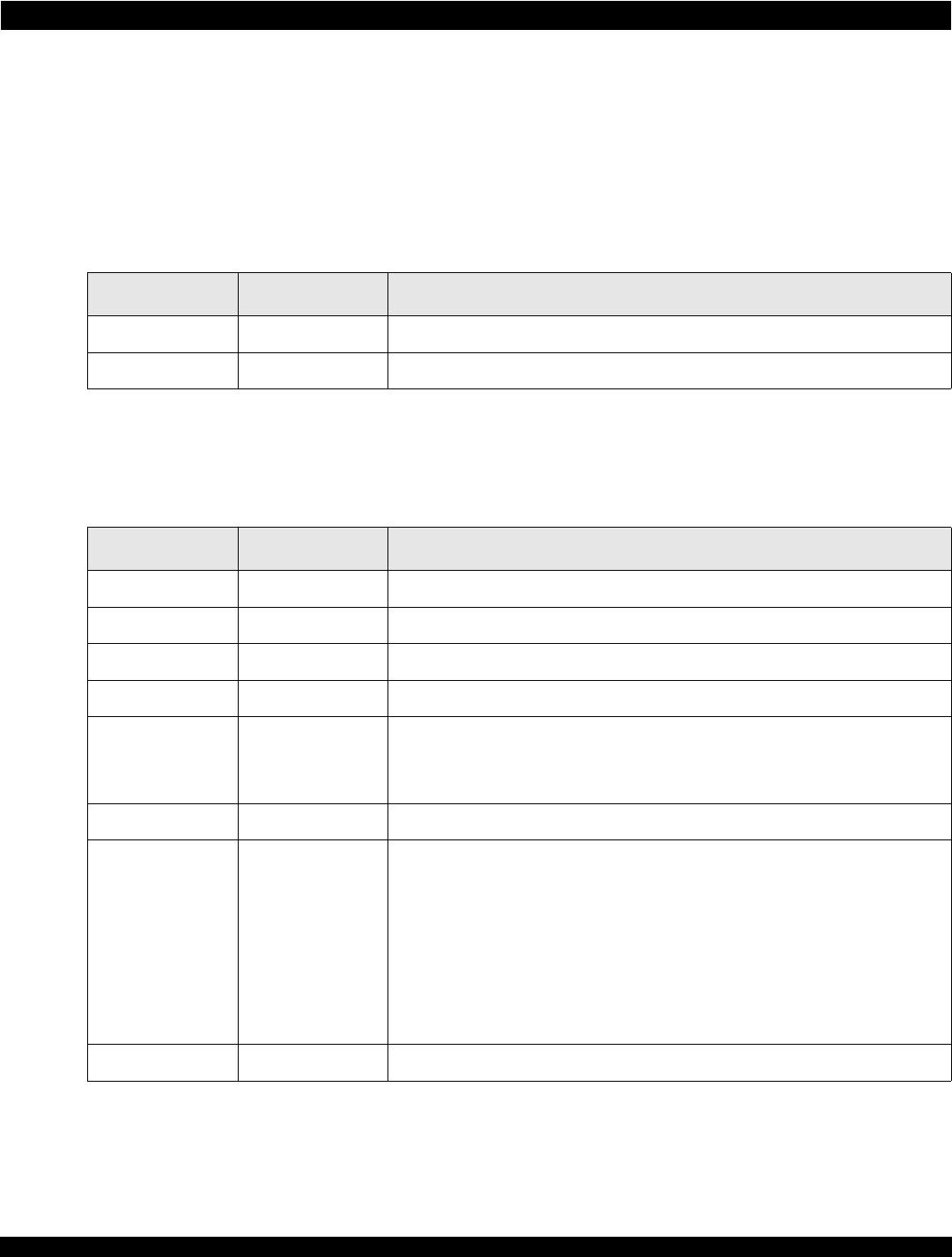

Table 6: JTAG Interface Signals

Name Pin Type Description

TCK I-PD IEEE 1149.1/1149.6 test access port. Clock input.

TDI I-PU IEEE 1149.1/1149.6 test access port. Serial data input

TDO O IEEE 1149.1/1149.6 test access port. Serial data output

TMS I-PU IEEE 1149.1/1149.6 test access port. Test mode select

TRSTn I-PU IEEE 1149.1/1149.6 test access port. Reset input.

This input must be asserted during the assertion of RSTn. Thereafter, it can be

left in either state.

TEST_ON I-PD Test mode pin. Tie low or NC for normal operation.

TEST_BCE I-PU Boundary scan compatibility enabled pin. This input aids 1149.6 testing. It must

be tied to VDDIO (or NC as there is internal pull up in pad) during normal

operation of the device.

0 = JTAG chain includes SerDes registers. SerDes registers are accessible to

external JTAG pins. Used during ATE and lab debug of SerDes registers through

an external JTAG Controller.

1 = JTAG chain does not include SerDes registers. SerDes register are

accessible through the internal register bus for BAR 0 access.

TEST_BIDIR_CTL I-PU Test mode pin. Tie high or NC for normal operation.