Tsi721 Datasheet 33 April 4, 2016

Integrated Device Technology

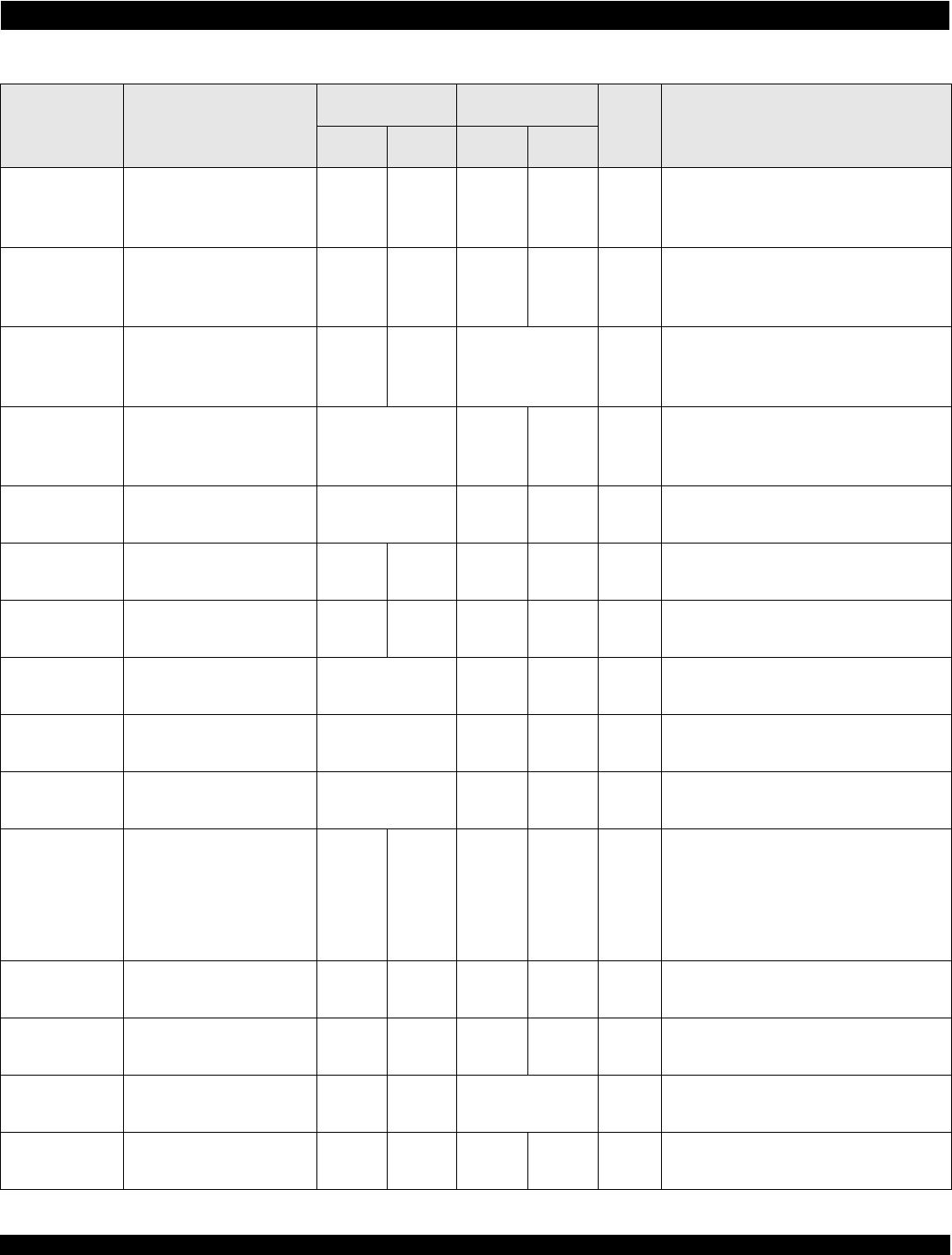

1. Receiver eye margins are defined into a 2 x 50 W reference load. A Receiver is characterized by driving it with a signal whose

characteristics are defined by the parameters specified in Table 4-10 and Table 4-11 of the PCI Express Base Specification

(Rev. 2.1)

2. The four inherent timing error parameters are defined for the convenience of Rx designers, and they are measured during

Receiver tolerancing.

3. Two combinations of PLL BW and peaking are specified at 5.0 Gbps to permit designers to make a trade off between the

two parameters. If the PLL’s minimum BW is >= 8MHz, then up to 3.0 dB of peaking is permitted. If the PLL’s minimum BW

is relaxed to >= 5.0 MHz, then a tighter peaking value of 1.0 dB must be met. Note: A PLL BW extends from zero up to the

value(s) defined as the minimum or maximum in the table. For 2.5 Gbps a single PLL bandwidth and peaking value of 1.5-22

MHz and 3.0 dB are defined.

4. Measurements must be made for both common mode and differential return loss. In both cases the DUT must be powered

up and DC isolated, and its D+/D- inputs must be in the low-Z state.

5. The Rx DC Common Mode Impedance must be present when the Receiver terminations are first enabled to ensure that the

Receiver Detect occurs properly. Compensation of this impedance can start immediately and the Rx Common Mode

Impedance (constrained by RLRX-CM to 50 W +/-20%) must be within the specified range by the time Detect is entered.

6. Common mode peak voltage is defined by the expression: maximum{|(Vd+ - Vd-) - VCMDC|}.

Z

RX-HIGH-IMP-D

C-POS

DC input CM input

impedance for V>0 during

reset or power down

50 k - 50 k - W Rx DC CM impedance with the Rx

terminations not powered, measured

over the range 0 - 200 mV with respect

to ground. See Note 7.

Z

RX-HIGH-IMP-D

C-NEG

DC input CM input

impedance for V<0 during

reset or power down

1.0 k - 1.0 k - W Rx DC CM impedance with the Rx

terminations not powered, measured

over the range -150 - 0 mV with respect

to ground. See Note 7.

V

RX-IDLE-DET-DI

FFp-P

Electrical idle detect

threshold

65 175 65 175 mV V

RX-IDEL-DET-DIFFp-p

= 2*|V

RX-D+

-

V

RX-D-

|. Measured at the package pins

of the Receiver. See Section 4.2.4.3 of

PCI Express Base Specification

(Rev. 2.1)

T

RX-IDLE-DET-DI

FF-ENTERTIME

Unexpected electrical Idle

enter detect threshold

integration time

- 10 - 10 ms An unexpected Electrical Idle

(V

RX-DIFFp-p

< V

RX-IDEL-DET-DIFFp-p

)

must be recognized no longer then

T

RX-IDLE-DET-DIFF-ENTERTIME

to signal an

unexpected idle condition.

L

RX-SKEW

Lane-to-lane skew - 20 - 8 ns Across all Lanes on a Port. this includes

variation in the length of a SKP Ordered

Set at the Rx as well as any delay

differences arising from the interconnect

itself. See Note 8.

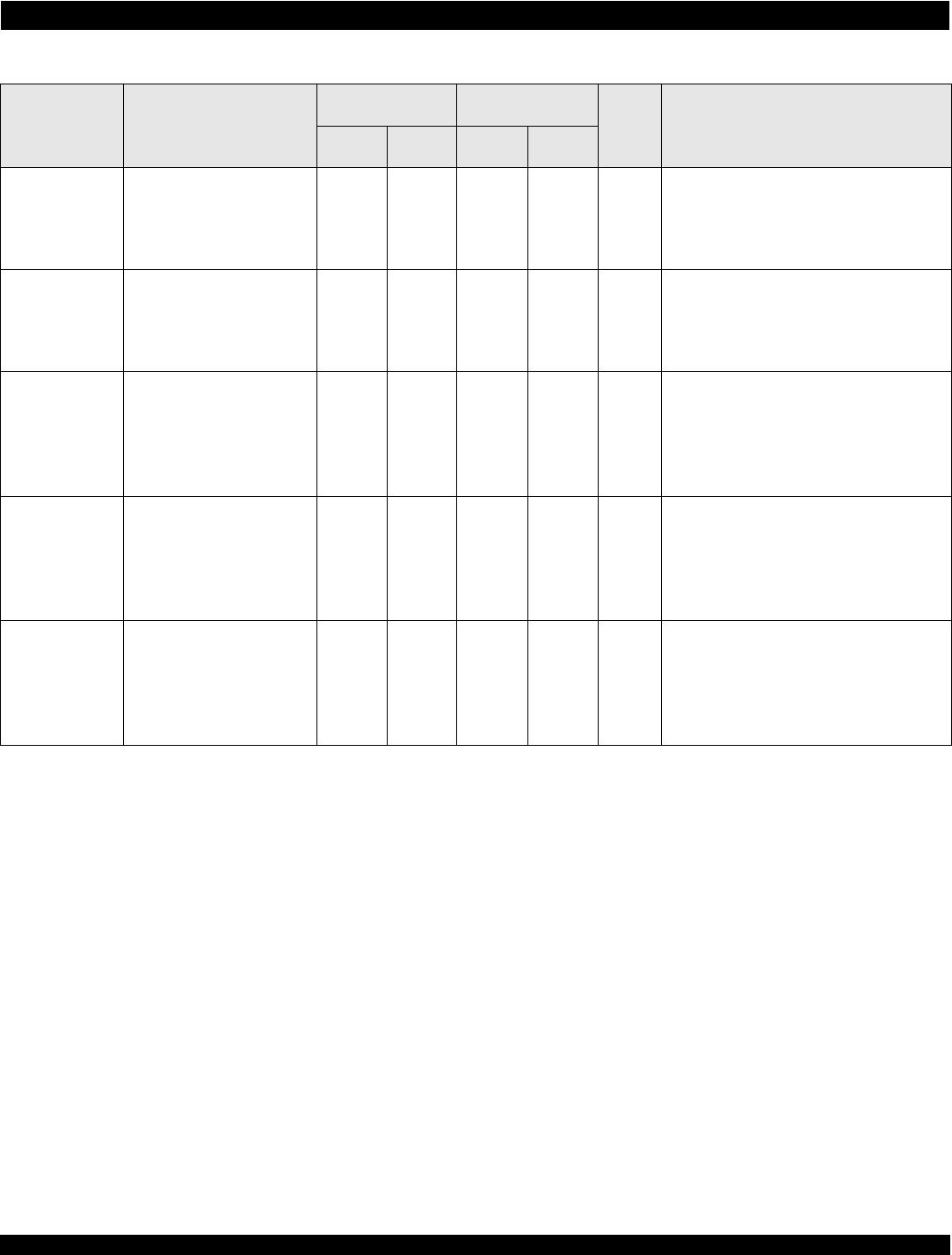

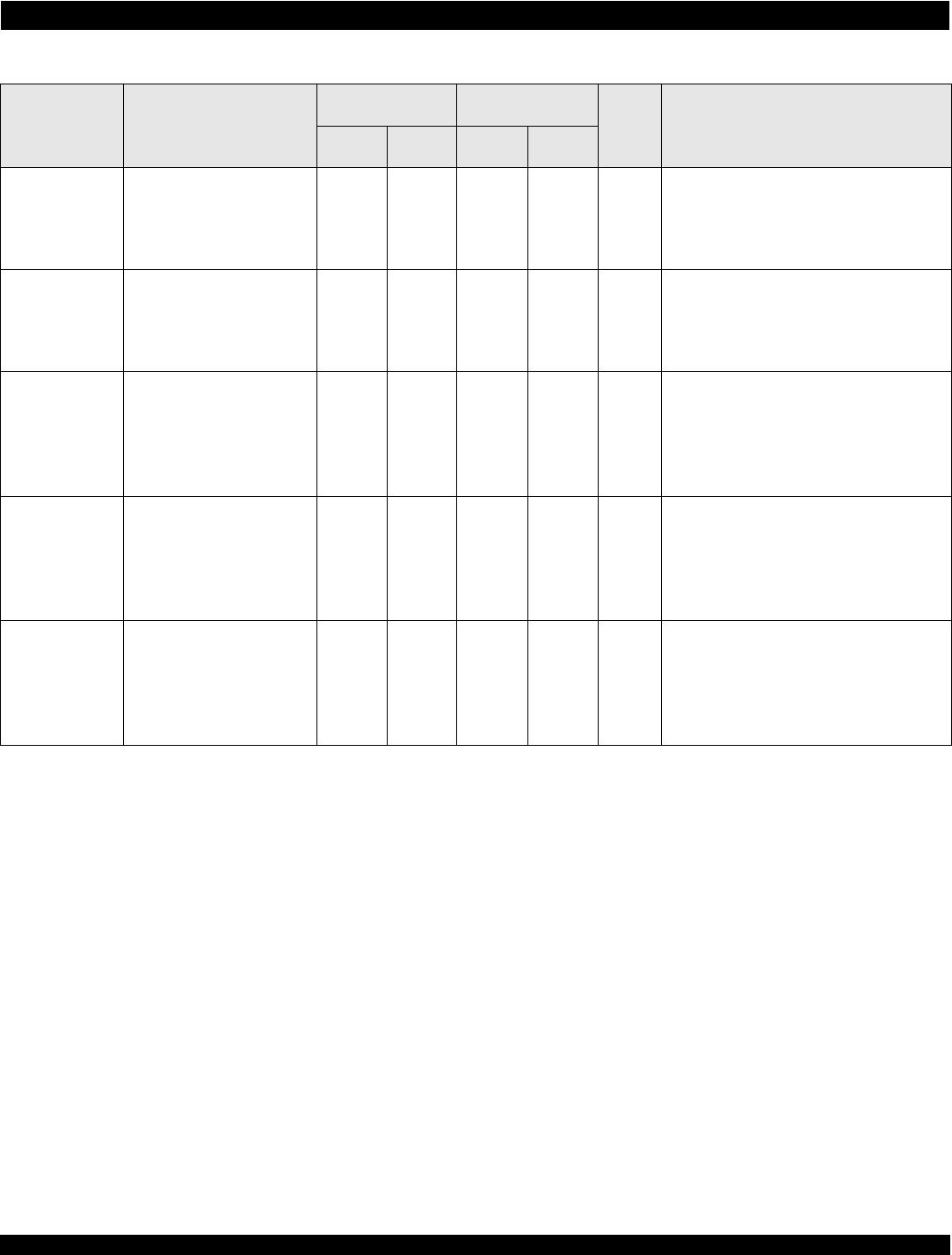

Table 18: PCIe Differential Receiver Specifications (Continued)

Symbol Parameter

2.5 Gbps 5.0 Gbps

Unit NotesMin. Max. Min. Max.