Tsi721 Datasheet 34 April 4, 2016

Integrated Device Technology

7. ZRX-HIGH-IMP-DC-NEG and ZRX-HIGH-IMP-DC-POS are defined respectively for negative and positive voltages at the

input of the Receiver. Transmitter designers need to comprehend the large difference between >0 and <0 Rx impedances

when designing Receiver detect circuits.

8. The LRX-SKEW parameter exists to handle repeaters that regenerate Refclk and introduce differing numbers of skips on

different lanes.

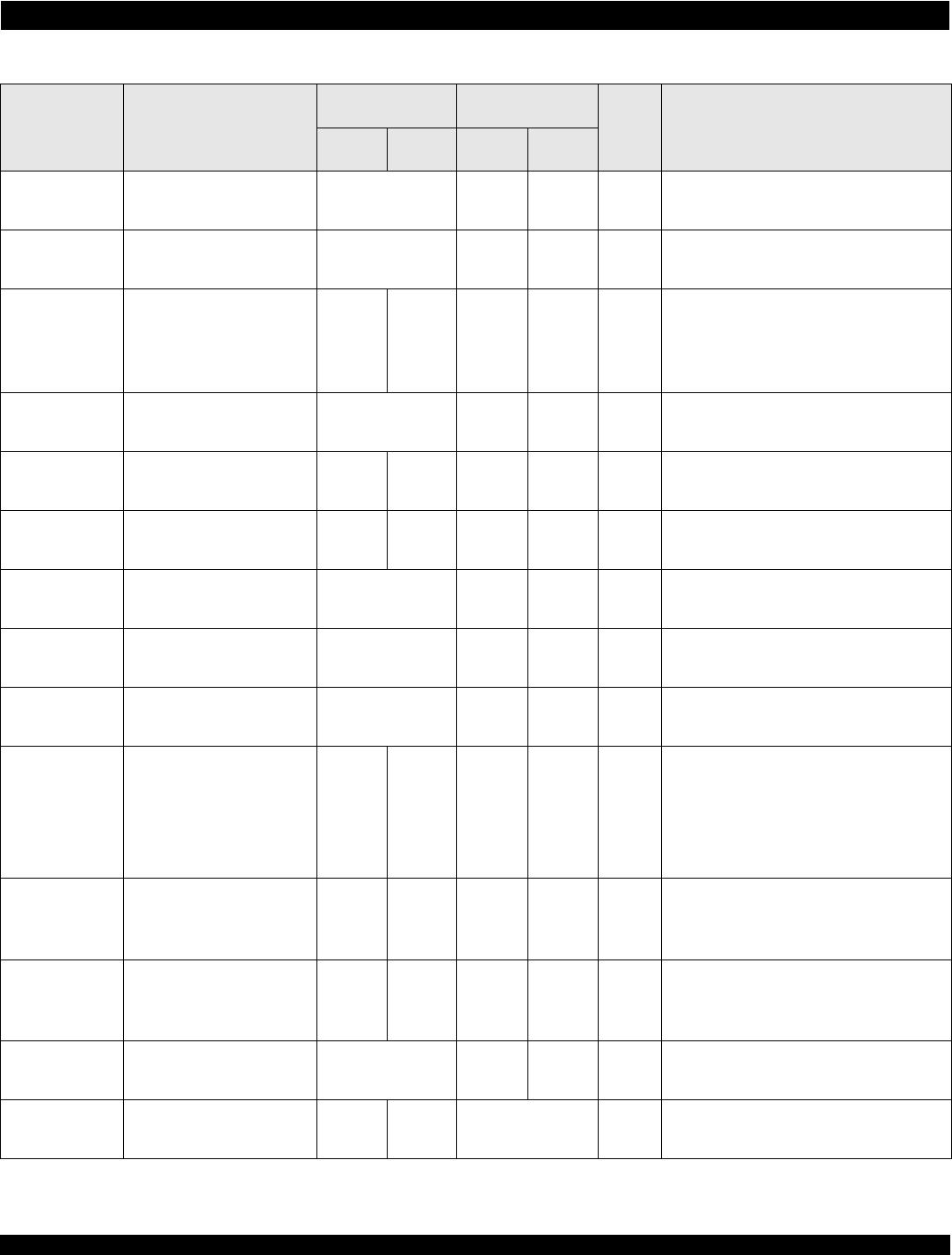

3.7.2 PCIe Differential Transmitter Specifications

Table 19 lists the electrical characteristics for the PCIe differential transmitters in the Tsi721. Parameters are defined

separately for 2.5 Gbps and 5.0 Gbps implementations. Table 19 is duplicated from the PCI Express Base Specification

(Rev. 2.1) Section 4.3.3.5 Table 4-9 on page 252.

Table 19: PCIe Differential Transmitter Specifications

Symbol Parameter

2.5 Gbps 5.0 Gbps

Unit NotesMin. Max. Min. Max.

UI Unit interval 399.88 400.12 199.94 200.06 ps The specified UI is equivalent to a

tolerance of +/- 300ppm for each Refclk

source. Period does not account for

SSC induced variations. See Note 1.

V

TX-DIFF-PP

Differential p-p Tx voltage

swing

0.8 1.2 0.8 1.2 V As measured with compliance test load.

Defined as 2*|V

TXD+

- V

TXD-

|

V

TX-DIFF-PP-LOW

Low power differential p-p

Tx voltage swing

0.4 1.2 0.4 1.2 V As measured with compliance test load.

Defined as 2*|V

TXD+

- V

TXD-

|. See Note

9.

V

TX-DE-RATIO-3.

5DB

Tx de-emphasis level

ratio

3.0 4.0 3.0 4.0 dB See Section 4.3.3.9 of PCI Express

Base Specification (Rev. 2.1) and Note

11 for information.

V

TX-DE-RATIO-6DB

Tx de-emphasis level

ratio

N/A N/A 5.5 6.5 dB See Section 4.3.3.9 of PCI Express

Base Specification (Rev. 2.1) and Note

11 for information.

T

MIN-PULSE

Instantaneous lone pulse

width

Not specified 0.9 - UI Measured relative to rising/falling

pulses. See Notes 2,10 and Figure 4-29

of PCI Express Base Specification

(Rev. 2.1)

T

TX-EYE

Transmitter eye including

all jitter sources

0.75 - 0.75 - UI Does not include SSC or Refclk jitter.

Includes Rj at 10-12. See Notes 2, 3, 4

and 10. Note that 2.5 Gbps and 5.0

Gbps use different jitter determination

methods.

T

TX-EYE-MEDIAN

-to-MAX-JITTER

Maximum time between

the jitter median and

maximum deviation from

the median

- 0.125 Not specified UI Measured differentially at zero crossing

points after applying the 2.5 Gbps clock

recovery function. See Note 2.