Tsi721 Datasheet 61 April 4, 2016

Integrated Device Technology

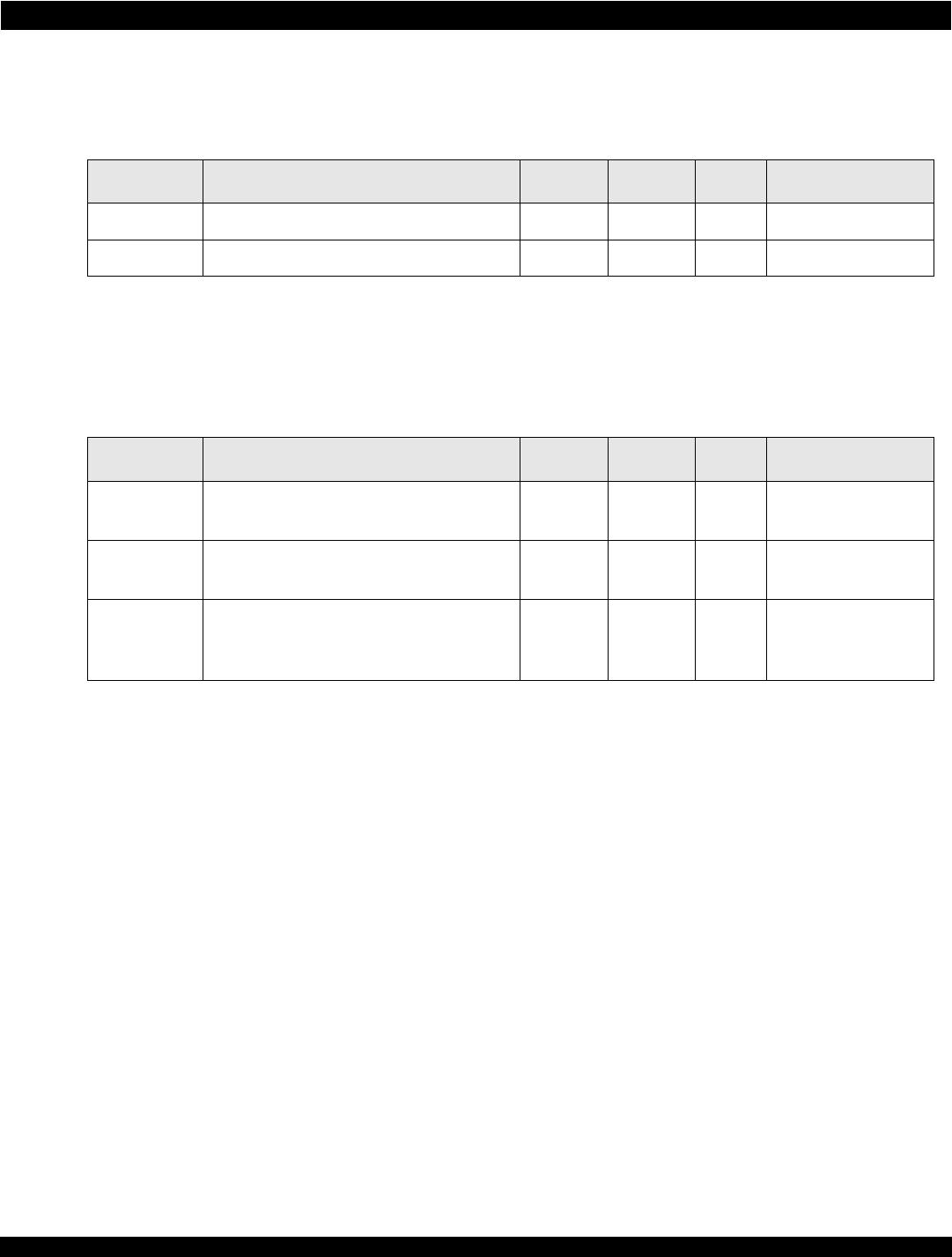

3.7.8 GPIO Interface Signal Timings

The following table lists the AC specifications for the GPIO Interface of the Tsi721.

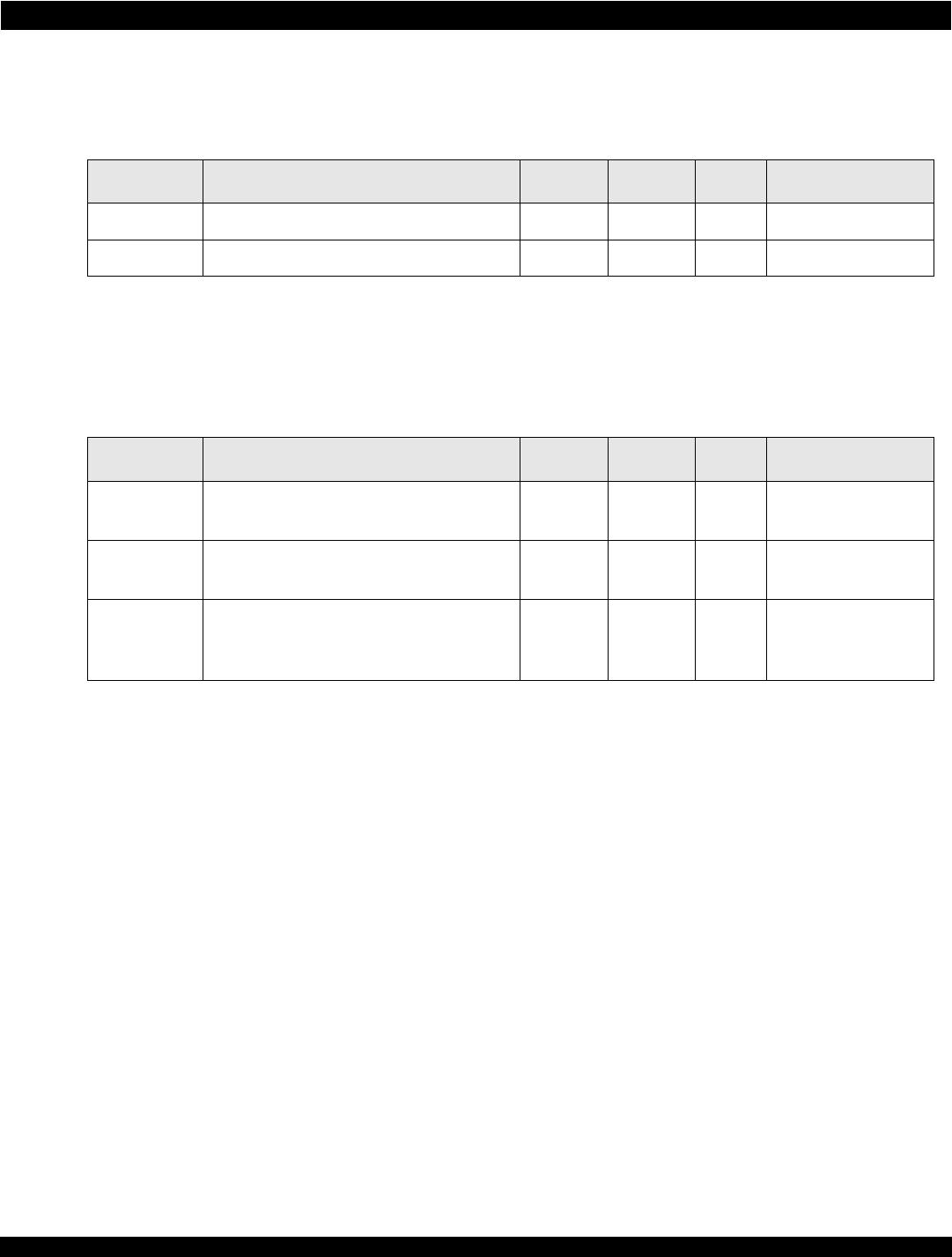

3.7.9 RSTn Signal Timings

The following table lists the RSTn signal timing for the Tsi721 (see PCIe spec 2.1 section 6.6.1 and CEM 2.0 table 2.6.2).

Table 35: GPIO Interface AC Specifications

Symbol Parameter Minimum Maximum Units Notes

T

MIN-HIGH

Minimum signal high time 50 - ns -

T

MIN-LOW

Minimum signal low time 50 - ns -

Table 36: RSTn Signal AC Specifications

Symbol Parameter Minimum Maximum Units Notes

T

perst

When asserted, RSTn must remain

asserted at least this long

100 - us -

T

fail

When power become invalid, RSTn must be

asserted within this time

- 500 ns -

T

perst-clk

RSTn must remain asserted after any

supplied reference clock (REFCLK and

PCCLK) is stable

100 - us -