Tsi721 Datasheet 60 April 4, 2016

Integrated Device Technology

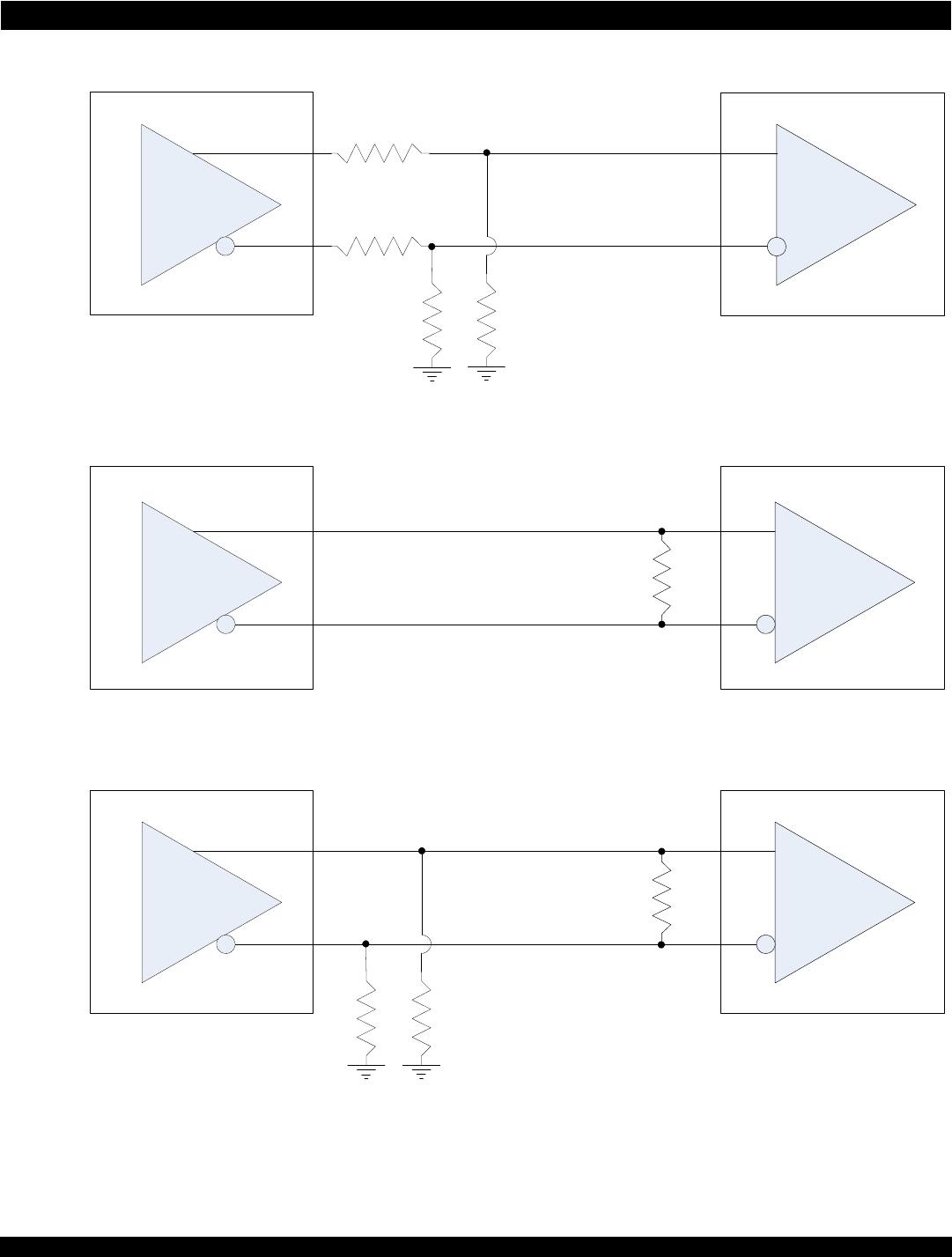

3.7.7 I2C Interface Signal Timings

The following table lists the AC specifications for the I2C Interface of the Tsi721.

1. Not tested.

2. See timing diagram displayed in Figure 16.

3. After this period, the first clock pulse is generated.

Figure 16: I2C Interface Signal Timings

Table 34: I2C Interface AC Specifications

Symbol Parameter Minimum Maximum Units Notes

F

SCL

I2C_SCLK clock frequency 0 100 kHz -

T

LOW

I2C_SCLK clock low time 4.7 - us See Notes 1 and 2.

T

HIGH

I2C_SCLK clock high time 4.0 - us See Notes 1 and 2.

T

HDDAT

Data hold time 0 3.45 us See Note 2.

T

SUDAT

Data setup time 250 - ns See Note 2.

T

SR

Rise time of I2C_SCLK and I2C_SD - 1000 ns See Note 2.

T

SF

Fall time of I2C_SCLK and I2C_SD - 300 ns See Note 2.

T

BUF

Bus free time between STOP and START

condition

4.7 - us See Note 2.

T

HDSTA

Hold Time (repeated) START condition 4.0 - us See Notes 2 and 3.

T

SUSTA

Setup time for repeated START condition 4.7 - us See Note 2.

T

SUSTO

Setup time for STOP condition 4.0 - us See Note 2.

SDA

SCL

T

BUF

Stop Start

T

LOW

T

HDSTA

T

HIGH

T

SR

T

HDDAT

T

SF

T

SUDAT

T

SUSTA

Repeated

T

HDSTA

T

SP

Stop

T

SUSTO

Start